处理完连通性和电源之后,需要对整板的情况进行走线优化调整,以充分满足各类EMC等要求。

14.10.1 3W原则

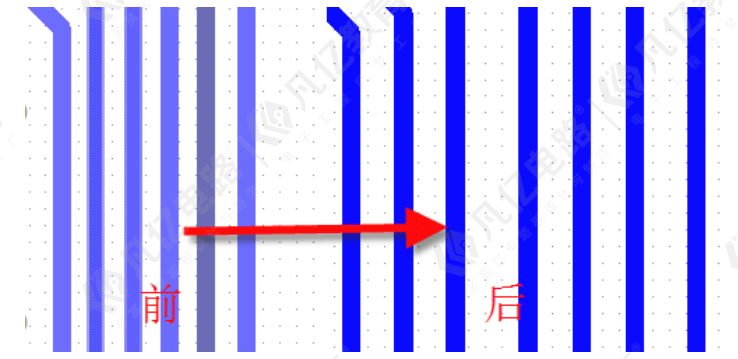

为了减少线间串扰,应保证线间距足够大,当线中心距不少于3倍线宽时,则可保证70%的线间电场不互相干扰,这称为3W原则。如图14-39所示,修线后期需要对此进行优化修整。

图14-39 3W原则优化

14.10.2 修减环路面积

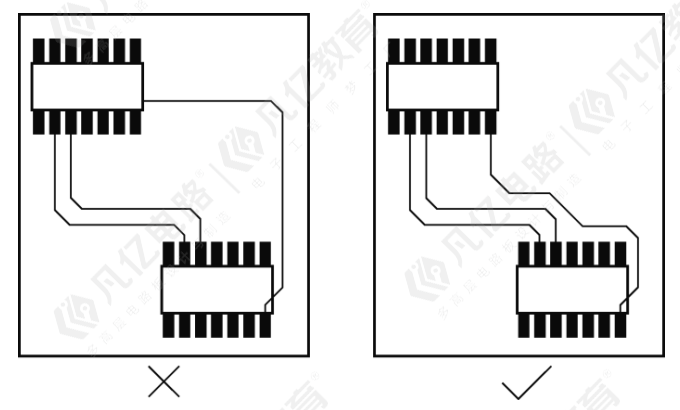

电流的大小与磁通量成正比,较小的环路中通过的磁通量也较小,因此感应出的电流也较小,这就说明环路面积必须最小。如图14-40所示,尽量在出现环路的地方让其面积做到最小。

图14-40 修减环路面积

14.10.3 孤铜及尖岬铜皮的修整

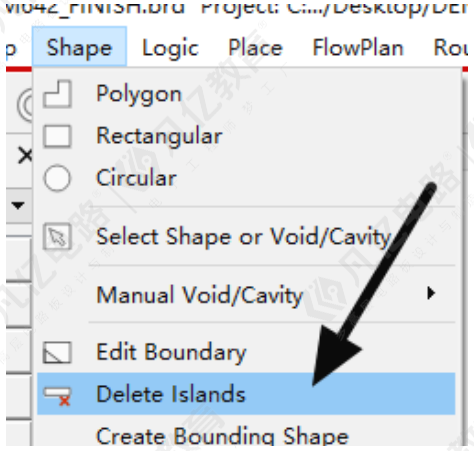

为了满足生产的要求,PCB设计中不应出现孤铜。在allegro软件中通常是手动进行铺铜,因此一般不会出现孤岛铜皮,若是采用整板铺铜则需要移除孤铜,执行菜单命令Shape-Delete Islands,移除孤岛铜,如图14-41所示。

图14-41 移除孤岛铜

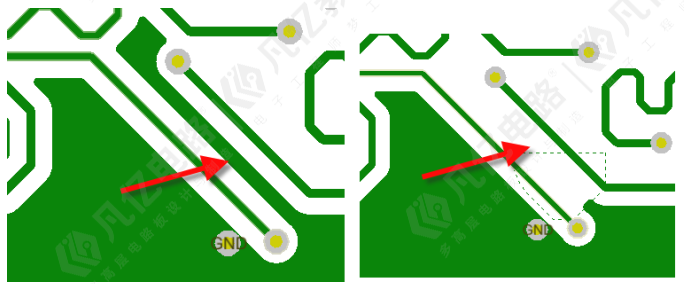

为了满足信号要求(不出现天线效应)及生产要求等,PCB设计中应尽量避免出现狭长的尖岬铜皮。以图14-42为例,可以通过放置禁布区删除尖岬铜皮。

图14-42 尖岬铜皮移除

14.10.4 回流地过孔的放置

信号最终回流的目的地是地平面,为了缩短回流路径,在一些空白的地方或打孔换层的走线附近放置地过孔,特别是在高速线旁边,可以有效地对一些干扰进行吸收,也有利于缩短信号的回流路径。

扫码关注

扫码关注