在PCB设计中,过孔的扇出很重要,扇孔的方式会影响到信号完整性、平面完整性、布线的难度,以至于影响到生产的成本。

从扇孔的直观目的来讲,主要是两个。

(1)缩短回流路径,比如GND孔,就近扇孔可以达到缩短路径的目的。

(2)打孔占位,预先打孔是为了防止不打孔后面走线很密集的时候无法打孔下去,绕很远连一条线,这样就形成很长的回流路径了。这种情况进行高速PCB设计及多层PCB设计的时候经常遇到。预先打孔后面删除很方便,反之等走线完了再想去加一个过孔,很难,这时候通常的想法就是随便找条线连上便是,不能考虑到信号完整性,不太符合规范做法。

10.4.1 扇孔推荐及缺陷做法

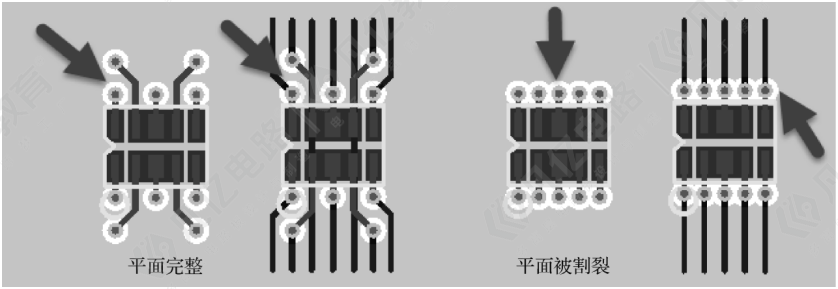

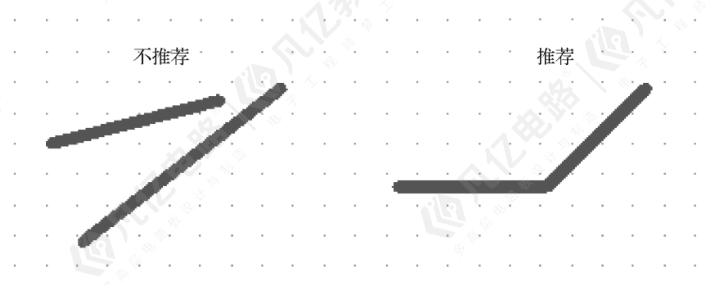

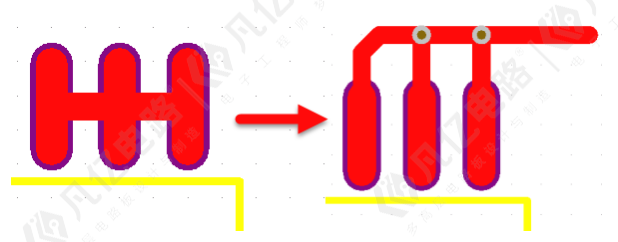

从图10-63中可以看出,推荐做法可以在内层两孔之间过线,参考平面也不会被割裂,反之不推荐做法增加了走线难度,也把参考平面割裂,破坏平面完整性。

图10-63 常规CHIP元件扇出方式对比

同样,这样的元件扇孔方式也适用于打孔换层的情景,如图10-64所示。

图10-64 打孔换层的情景

10.4.2 PCB过孔添加与设置

在进行PCB设计时,都必须使用到过孔,对走线进行换层处理。在走线进行打过孔之前,必须先要添加过孔,这样在PCB布线时才可以使用过孔,具体操作的步骤如下所示;

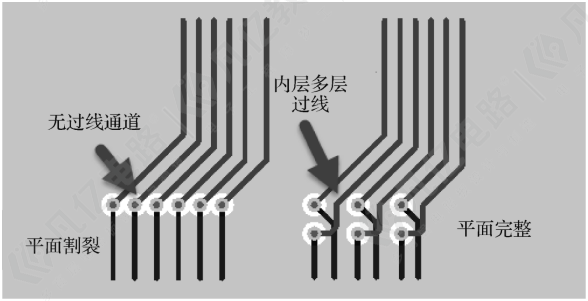

(1)需要使用pad designer工具制作过孔,这个在前面的PCB封装库问答中已经详细讲述过,这里不再做赘述,我们在PCB常用的过孔有几下几种,如图10-65所示:

图10-65 常用过孔类型示意图

过孔制作完成之后,在PCB中将制作好的过孔的路径指定在封装库路径下,才可以在后面调用已经制作好的过孔。

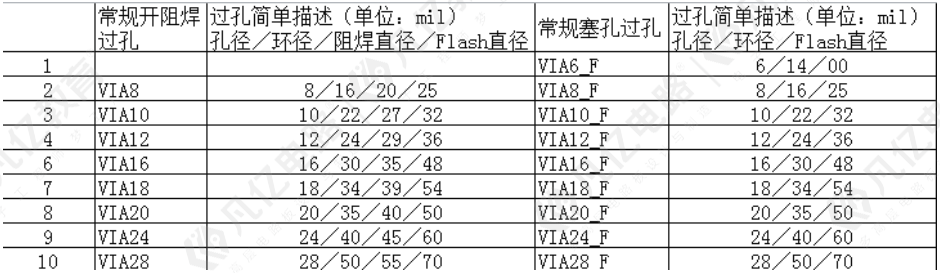

(2)打开规则管理器,执行菜单命令Setup-Constraints-Constraints Manager,进入规则管理器,在左侧边栏中选择Phyical物理规则,点击all layer,然后在右侧Vias这一栏,双击空白处,如图10-66所示。

图10-66 添加过孔示意图

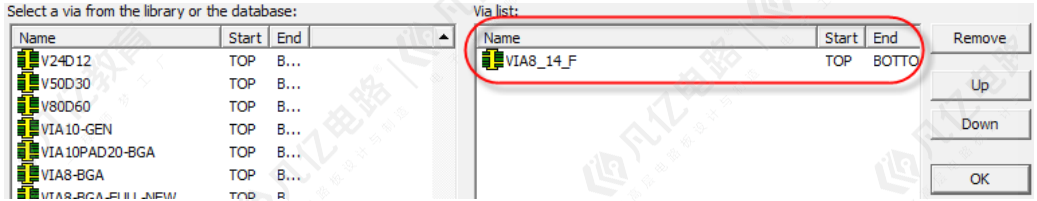

(3)在弹出的过孔列表中,选择过孔到过孔列表中,双击左侧的过孔就可以添加到右侧的PCB过孔列表中,点击OK选项,过孔就添加成功了,如图10-67所示;

图10-67 过孔选取示意图

(4)回到规则管理器中,在Vias哪一栏可以看到刚才选择的过孔已经成功添加了,这样在PCB布线中双击鼠标左键就可以打孔换层了。

10.4.3 BGA类器件扇孔

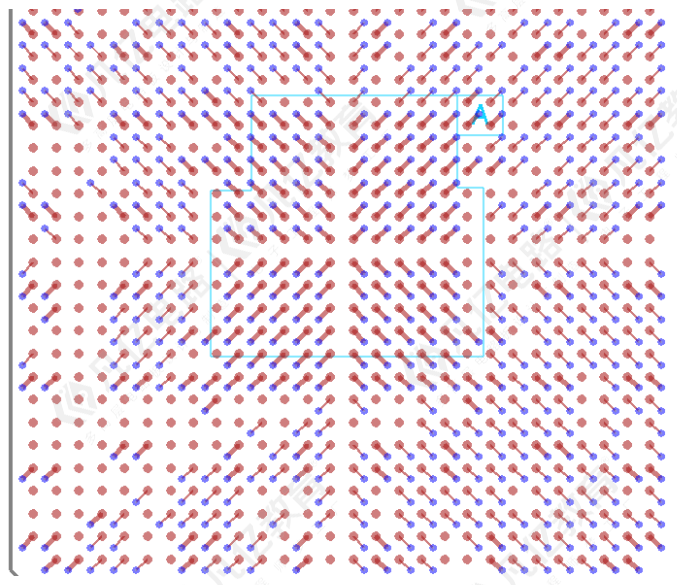

对于BGA扇孔,同样过孔不宜打孔在焊盘上,推荐打孔在两个焊盘的中间位置。很多工程师为了出线方便,随意挪动BGA里面过孔的位置,甚至打在焊盘上面,如图10-68所示,从而造成BGA区域过孔不规则,易造成后期焊接虚焊的问题,同时可能破坏平面完整性。

图10-68 BGA盘中孔示例

对于BGA扇孔,ALLEGRO提供快捷的自动扇出功能。

(1)对BGA扇出之前,根据BGA的Pitch间距(BGA两个焊盘中心间距)和10.2节内容对整体的间距规则、网络线宽规则及过孔规则进行设置。

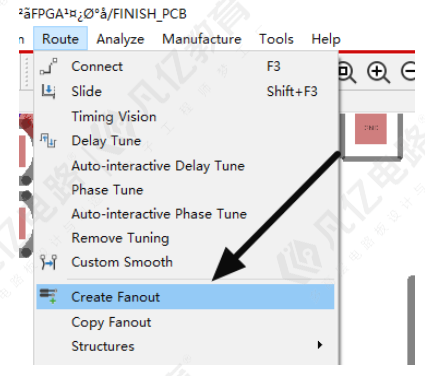

(2)执行菜单命令Route-Create Fanout,对其进行如图10-69、10-70所示的设置。

图10-69 扇出控制规则设置

图10-70 扇出控制规则设置

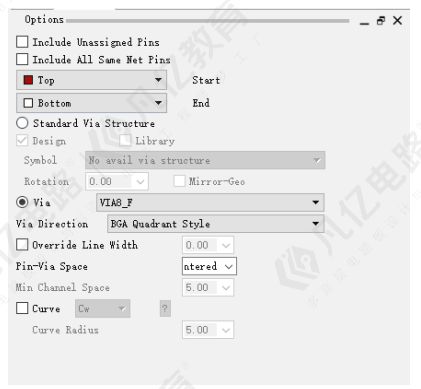

选择好需要配置的选项,对每一个选项释义如下。

l Include Unassigned Pins:含义是扇出的时候,将没有网络的管脚也进行扇出,一般不用勾选,空网络的管脚不用进行扇出;

l Include All Same Net Pins:含义是当单独对某一个管脚进行扇出时,将跟这个管脚网络一致的管脚也进行扇出,一般不用勾选;

l Via:选择扇出所需要用到的过孔,过孔首先需要在物理规则里面添加好,不然这里没有可以选择的过孔;

l Via Direction:过孔的方向朝向,一般选择BGA类型的风格,给BGA器件留出十字通道,方便散热;

l Pin-Via Space:过孔到焊盘的间距,一般选择中心间距,将过孔扇出在周围四个焊盘的中心处。

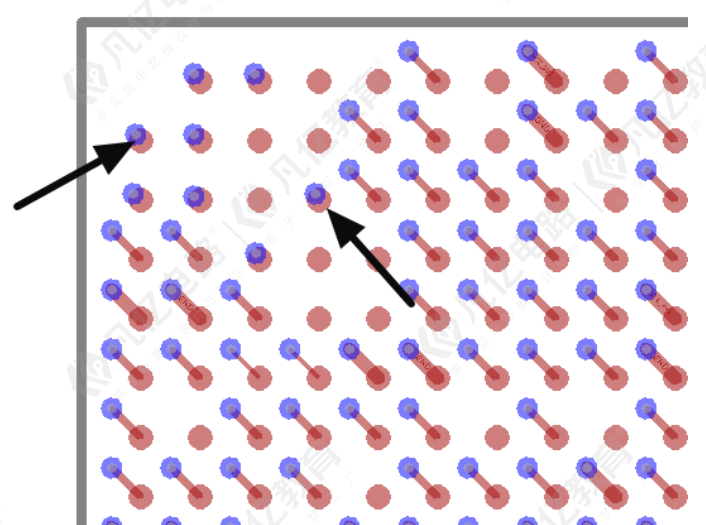

(3)设置完成之后,即激活扇出命令,单击需要进行扇出的BGA元件,软件会自动完成扇出,如图10-71所示

图10-71 BGA扇出示意图

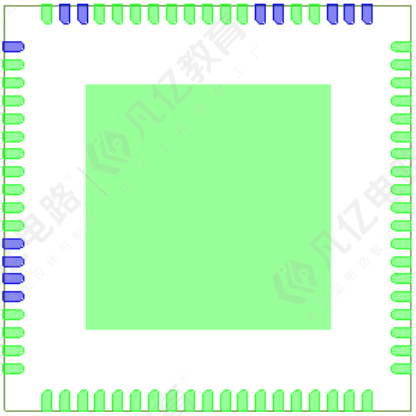

10.4.4 QFN类器件扇孔

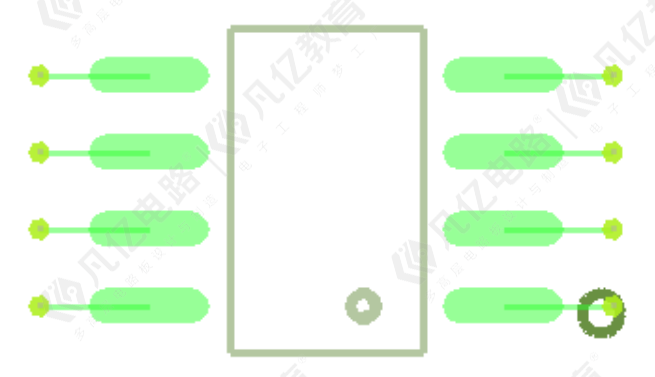

QFN封装(方形扁平无引脚封装),如图10-72所示,具有良好的电和热性能、体积小、重量轻、其应用正在快速增长,采用微型引线框架的QFN封装称为MLF封装(微引线框架)。QFN封装和CSP(芯片尺寸封装)有些相似,但元件底部没有焊球,与PCB的电气和机械连接是通过PCB焊盘上印刷焊膏、过回流焊形成的焊点来实现的。

图10-72 QFN封装示意图

对于QFN类型的封装,通常需要我们手动去进行扇孔。

(1)根据10.2节内容对整体的间距规则、网络线宽规则及过孔规则进行设置。

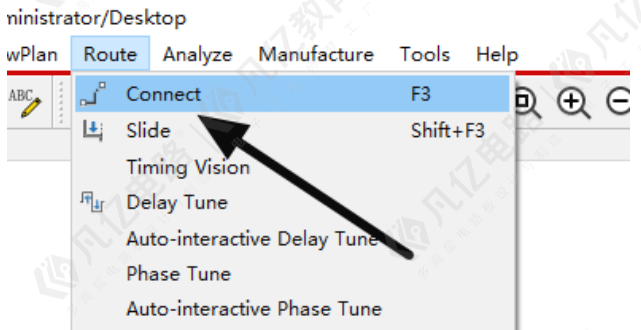

(2)执行菜单命令Route-Connect,如图10-73所示,进行走线,然后在走线命令下鼠标左键双击进行打孔

图10-73 走线命令示意图

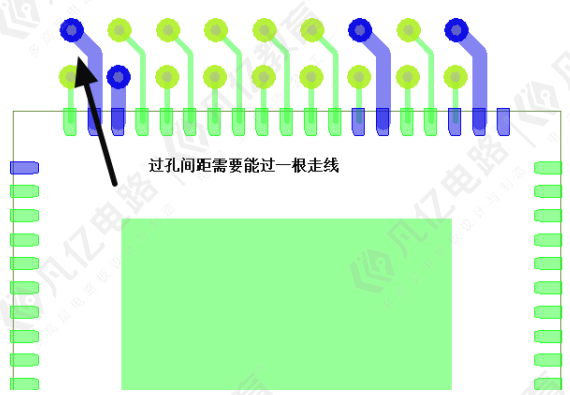

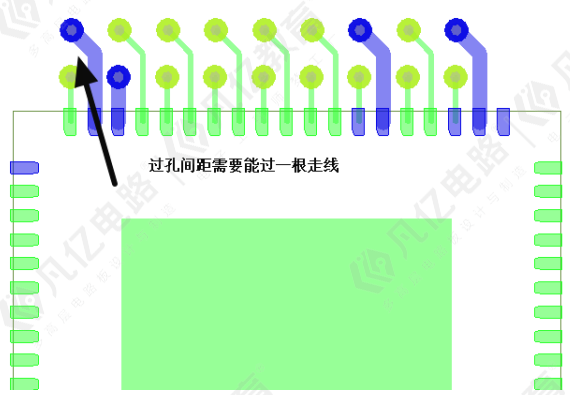

(3)QFN封装扇出示意图如图10-74所示,在相邻两个管脚间扇出的过孔之间需要留出能过一根走线的间距,从而使其他层的走线能从过孔间穿过进行连接

图10-74 QFN封装扇孔示意图

10.4.5 SOP类器件扇孔

SOP封装是一种元件封装形式,如图10-75所示,常见的封装材料有:塑料、陶瓷、玻璃、金属等,现在基本采用塑料封装,主要用在各种集成电路中。SOP封装的应用范围很广,而且以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等在集成电路中都起到了举足轻重的作用。

图10-75 SOP封装示意图

这种封装类型扇孔方式与QFN扇孔方式类似。

(1)根据10.2节内容对整体的间距规则、网络线宽规则及过孔规则进行设置。

(2)执行菜单命令Route-Connect,进行走线,然后在走线命令下鼠标左键双击进行打孔。

(3)根据PIN之间的间距,会有两种扇孔的方式

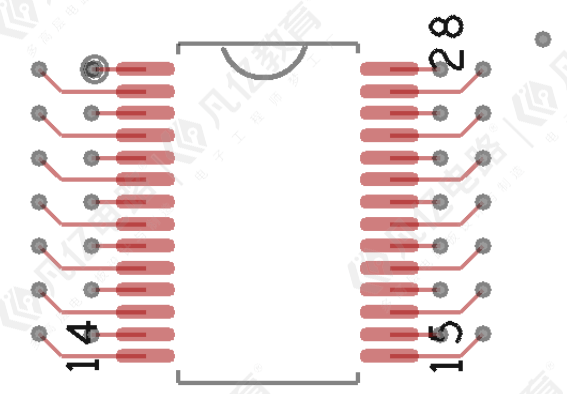

①直接从焊盘引脚善出,且过孔之间能过一根走线不引起DRC报错,如图10-76所示。

图10-76 SOP封装扇孔示意图

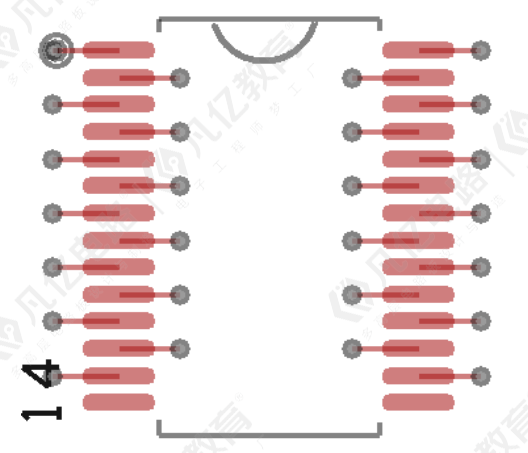

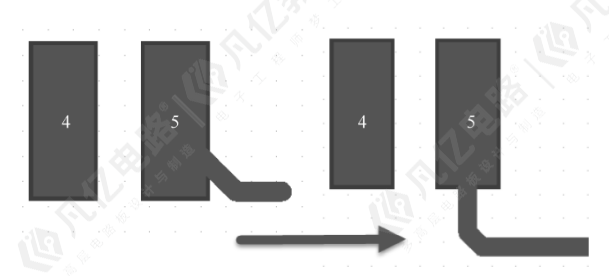

②直接从焊盘引脚善出,过孔间无法通过一根走线,就需要相邻两个管脚的孔善出在同一条线上,且过孔间留有过一根走线的距离,如图10-77所示。

图10-77 SOP封装扇孔示意图

③相邻管脚从不同方向进行扇出,如图10-78所示。

图10-78 SOP封装善孔示意图

10.4.6 扇孔的拉线

扇孔不仅仅打孔,扇孔也会进行短线的拉线处理,所以有必要对扇孔的拉线的一些要求进行说明。

(1)为满足国内制板厂的生产工艺能力要求,常规扇孔拉线线宽大于或等于4mil(0.1016mm)(特殊情况可用3.5mil,即0.0889mm);小于这个值会极大挑战工厂的生产能力,报废率提高。

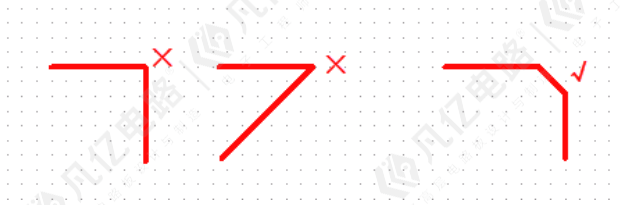

(2)不能出现任意角度走线,任意角度走线会挑战工厂的生产能力,很多在蚀刻铜线时出现问题,推荐45°或135°走线,如图10-79所示。

图10-79 任意角度走线和135°走线

(3)如图10-80所示,同一网络不宜出现直角或锐角走线。直角或锐角走线一般是PCB布线中要求尽量避免的情况,这也几乎成为衡量布线好坏的标准之一。直角走线会使传输线的线宽发生变化,造成阻抗不连续,造成信号的反射,尖端产生EMI影响线路。

图10-80 不宜出现直角或锐角走线

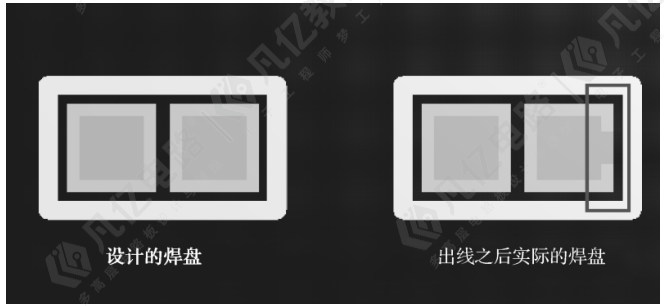

(4)设计的焊盘的形状一般都是规则的,如BGA的焊盘是圆形的,QFP的焊盘是长圆形的,CHIP元件的焊盘是矩形的等。但实际做出的PCB,焊盘却不规则,可以说是奇形怪状。以0402R电阻封装的焊盘为例,如图10-81所示,由于生产时存在工艺偏差,设计的规则焊盘出线之后,实际的焊盘是在原矩形焊盘的基础上加一个小矩形焊盘组成的,不规则,出现了异形焊盘。

图10-81 设计的焊盘和出线之后实际的焊盘

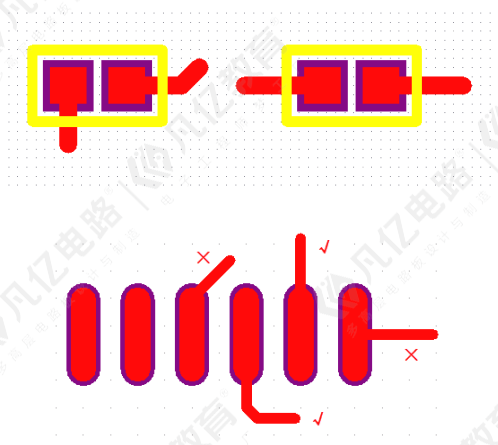

如果在0402R电阻封装的两个焊盘对角分别走线,加上PCB生产精度造成的阻焊偏差(阻焊窗单边比焊盘大0.1mm),会形成如图10-82中左图所示的焊盘。在这样的情况下,电阻焊接时由于焊锡表面张力的作用,会出现如图10-82中右图所示的不良旋转。

图10-82 不良出线造成元件容易旋转

(5)采用合理的布线方式,焊盘连线采用关于长轴对称的扇出方式,可以比较有效地减小CHIP元件贴装后的不良旋转;如果焊盘扇出的线也关于短轴对称,那么还可以减小CHIP元件贴装后的漂移,如图10-83所示。

图10-83 元件的出线

(6)相邻焊盘是同网络的,不能直接连接,需要先连接外焊盘之后再进行连接,如图10-84所示,直连容易在手工焊接的时候造成连焊。

图10-84 相邻同网络焊盘的连接方式

(7)连接器管脚拉线需要从焊盘中心拉出再往外走,不可出现其他的角度,避免在连接器拔插的时候把线撕裂,如图10-85所示。

图10-85 连接器的出线

扫码关注

扫码关注