14.3.1 原理图的检查

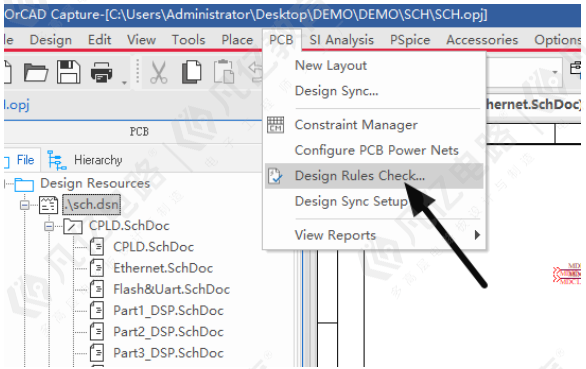

在原理图中选择工程根目录.dsn执行菜单命令PCB-Design Rules Check,进行原理图的检查,如图14-2所示。

图14-2 原理图的检查

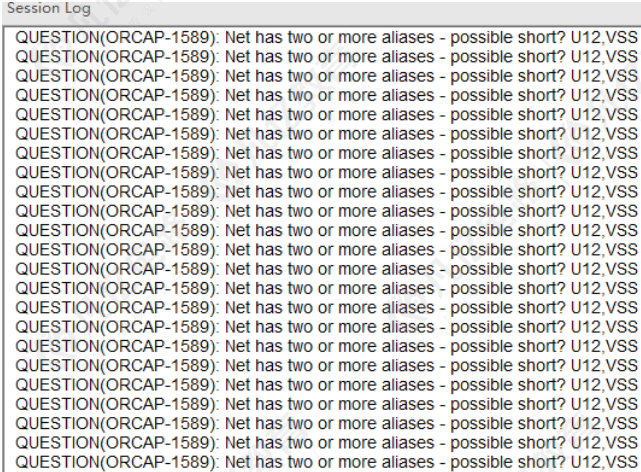

然后会在原理图下面Session Log窗口出现相对应的报错及警告,如图14- 3所示,如没有报错则可以进行忽略。

图14- 3原理图检查报错

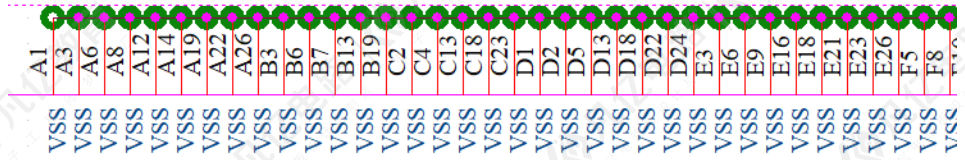

图中所示报错为U12的VSS有两个或者更多的网络标签,然后在原理图中找到该器件,检查其VSS管脚,如图14-4所示,由于该项报错是在设计允许的范围内且不会影响网表的导出,因此可以进行忽略。

图14-4 错误的定位检查

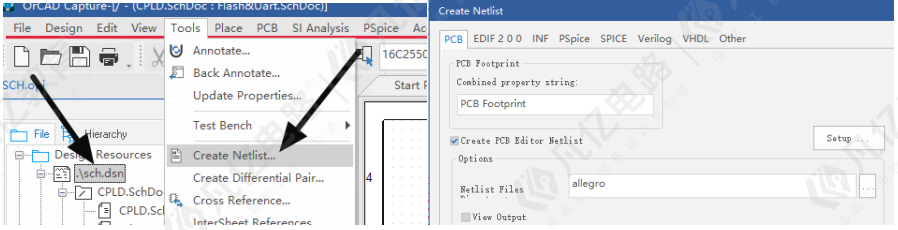

14.3.2 原理图网表的导出

(1)选中根目录的.dsn,执行菜单命令Create Nelist,采用默认设置,点击“确定”导出第一方网表,如图14-5所示。

图14-5 导出第一网网表

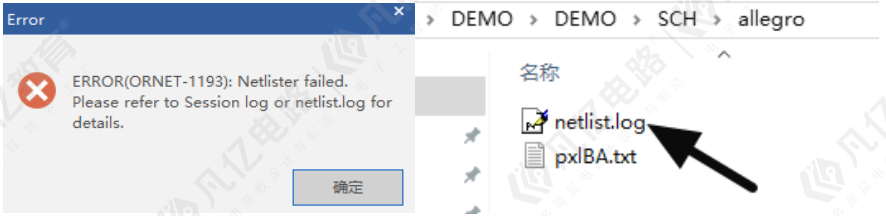

(1)当出现如图14-6所示的提示时,意味着原理图有错误,导出网表不成功,此时需要在路径中找到netlist.log文件,右键使用写字板进行打开,查看错误信息。

图14-6 导出网表报错示意图

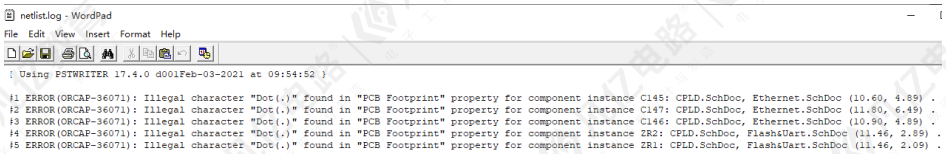

3)如图14-7所示为显示的报错信息,该报错为在C145,C147,C146,ZR2,ZR1的封装名中含有非法字符(dot)的报错。

图14-7 网表报错信息

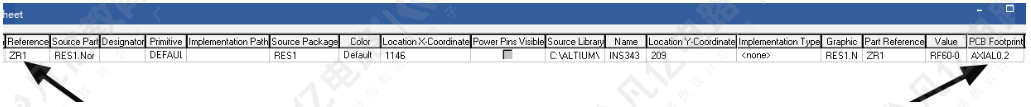

4)因此需要返回至原理图中,对所报错的器件单击右键Edit properties,报错原因为0.2中的这个(.)为非法字符,可以将(.)改为(_),如图14-8所示,其他器件解决方法一样,这里就不在重复操作了。

图14-8 修改封装信息非法字符示意图

5)更改完错误之后,对于网表重新导出,若没有弹出报错提示,则导入成功。

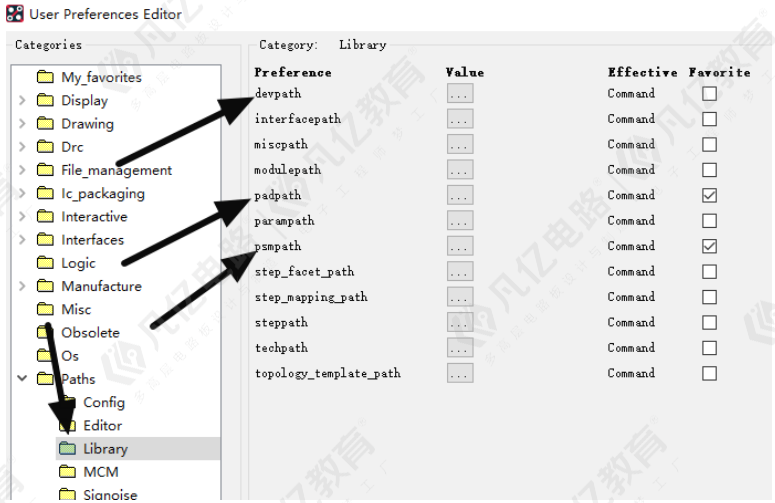

14.3.3 PCB库路径的指定

打开Cadence软件,执行菜单命令File-New,新建一个pcb,然后执行菜单命令Steup-User Preferences Editor,进行如图14-9所示,将devpath,padpath,psmpath指定客户所提供的库文件路径,该示例的封装库由本书配套的素材提供。

图14-9 库路径指定示意图

14.3.4 网表的导入

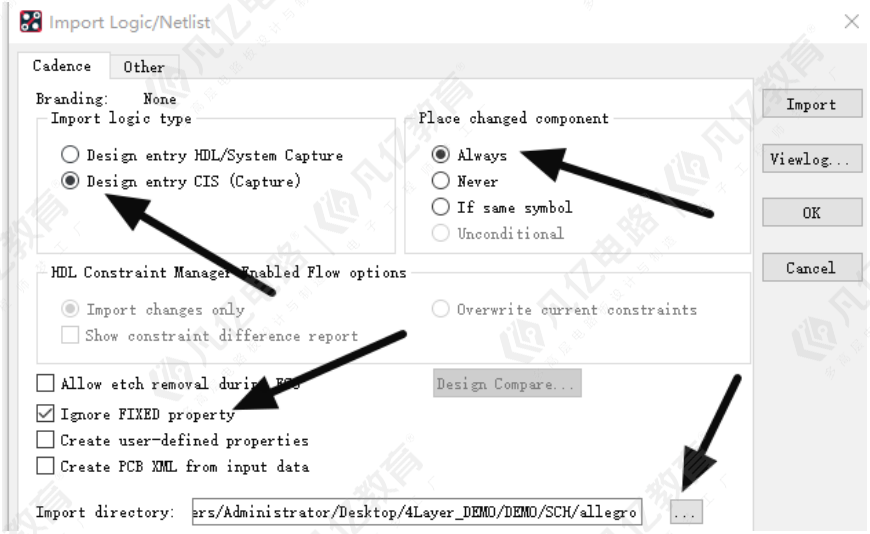

(1)在PCB中执行菜单命令File-Import-Logic,进行如图14-10的设置,将从原理图的第一网表导入至PCB中。

图14-10 网表导入示意图

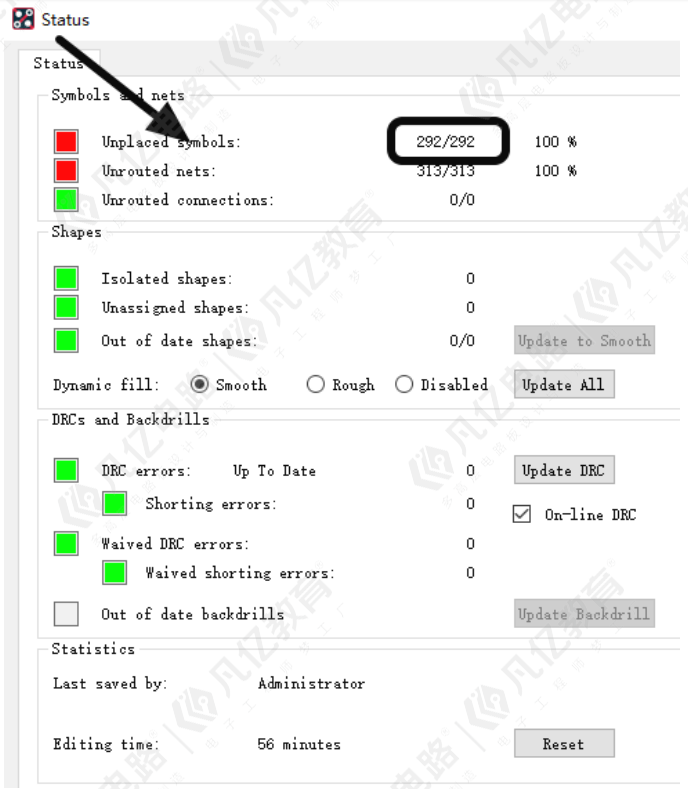

2)执行菜单命令Display-Status,查看器件导入状态,如图14-11所示,则导入成功。

图14-11 查看器件状态示意图

扫码关注

扫码关注