8.3.1 第一方网表导入

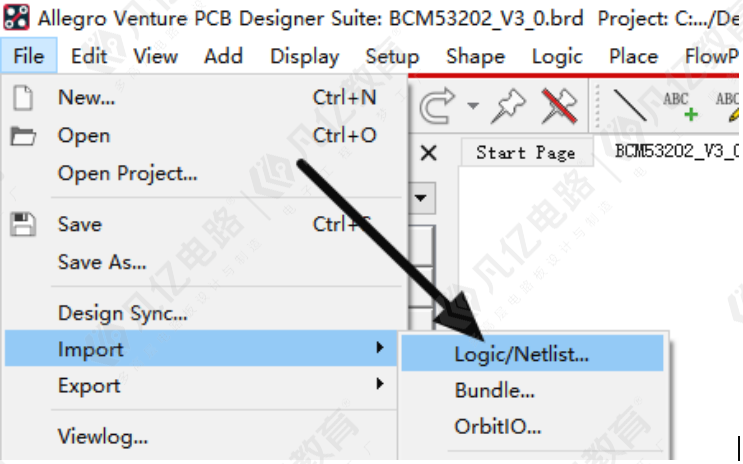

(1)在原理图中网表输出成功以后,然后新建一个新的PCB文件,进行网表的调入,执行操作File-Import导入,在下拉菜单中选择Logic命令,进行网表的调入,如图8-10所示;

图8-10 网表调入Allegro软件示意图

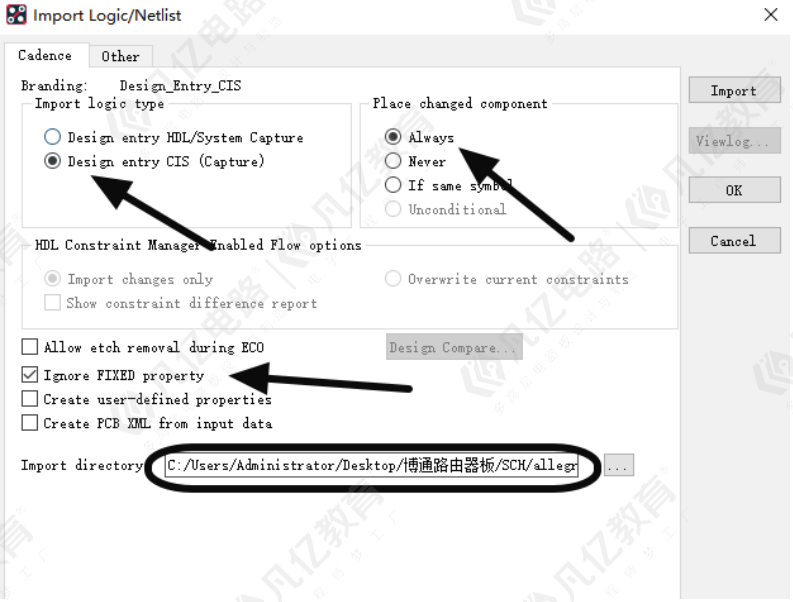

(2)执行上述操作之后,会弹出如图8-11所示的界面,导入Allegro软件的第一方网表需要选择Cadence界面,到入网表的类型选择第二项:Design entry CIS,下面的导入路径,需要选择到文件夹路径,一般网表的存放路径都是Allegro文件夹,这里选择到Allegro文件才可以;

图8-11 网表调入参数设置示意图

(3)按照上述如图8-11所示的参数设置,将网表调入的路径以及参数设置完毕,点击右上角的Import Cadence,就可以将第一方的网表导入到Allegro软件中,导入完毕后会弹出提示对话框,没有错误表示网表已经成功导入,有错误的话,表示导入是有问题的,没有导入成功,需要讲错误解决掉,在重新导入。

对于导入的常见的一些问题解决办法,作者在PCB联盟网论坛的百问百答板块进行了详细的说明,大家可以以问答的方式学习。

8.3.2 第三方网表导入

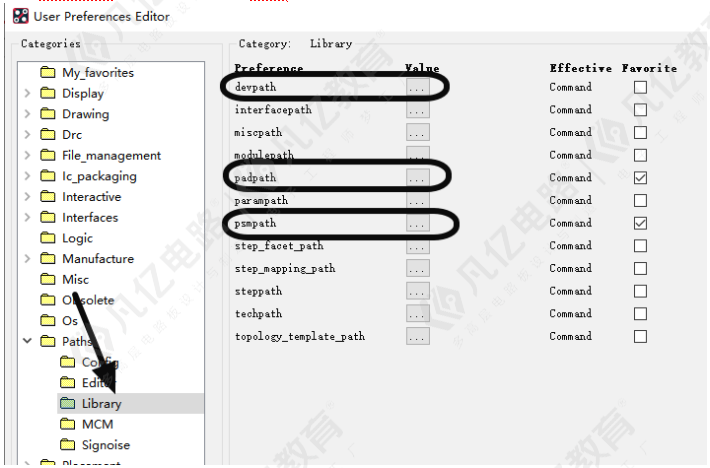

(1)第三方网表输出完成之后,新建一个PCB文件,导入第三方的网表导PCB文件中,在导入之前需要首先指定封装库路径。第一方网表不是必须的,执行菜单命令Setup-User preference,进行参数设置,如图8-12所示,在弹出的界面中,在左侧选择Paths,下面选择到Library,进入到封装库指定,需要指定三个封装库路径:

Ø Devpath:指定封装的device文件;

Ø Padpath:指定封装的焊盘文件;

Ø Psmpath:指定封装的psm文件。

图8-12 封装库路径指定示意图

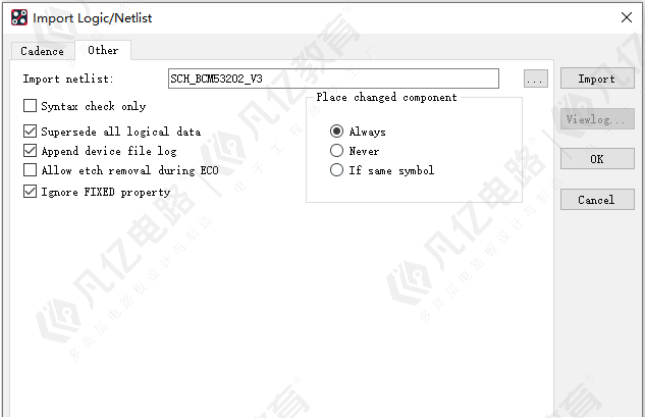

(2)指定好封装库的路径之后呢,就可以导入第三方网表了,同样的操作,File-Import导入,在下拉菜单中选择Logic命令,进行网表的调入,在弹出的界面中选择Other选项,如图8-13所示,左侧的复选框,选择第二、三、五项,其它不用勾选。上面的Import netlist选项,选择第三方的网表文件,是后缀为net的文件,需要注意的是,在存储网表文件的路径下,不要出现类型括号、*号等非法字符即可,设置完参数之后,右侧栏选择Import other选项,进行第三方网表的导入;

(3)导入之后,会有导入的报告显示,报告显示没有错误的话,就是已经导入成功了,显示有错误的话,表示没有导入成功,需要将提示的错误都解决掉之后呢,然后重新导入即可。

图8-13 第三方网表调入示意图

扫码关注

扫码关注