15.5.1 CPU的设计

1.电容的放置

CPU电源布线时都需要一些电容。滤波电容(也作旁路电容)放置在距离电源较近的位置。用于bypass电源位置引入的高频信号,如果不加旁路电容,高频干扰可能从电源部分引入芯片的内部。退耦电容对于在数字电路高速切换时起到缓冲电压变化的作用。一般来说,大电容放置在主控芯片背面(或就近),以保证电源纹波在100mV以内,避免在大负载情况下引起电源纹波偏大。

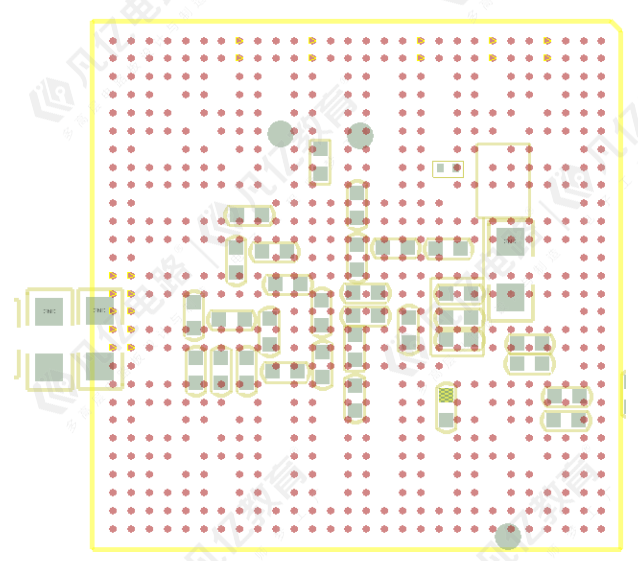

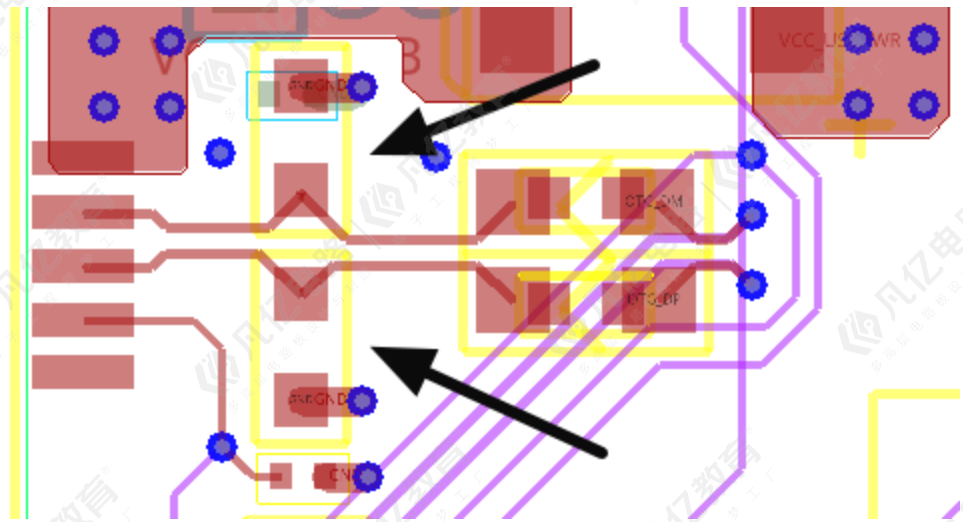

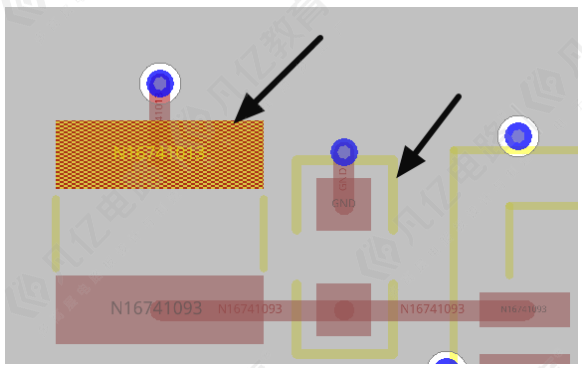

此实例由于结构限制,小电容靠近CPU背面进行放置,大电容就近放置在CPU周围及路径上,如图15-8所示。

图15-8 滤波电容的放置

2.电源供电的设计

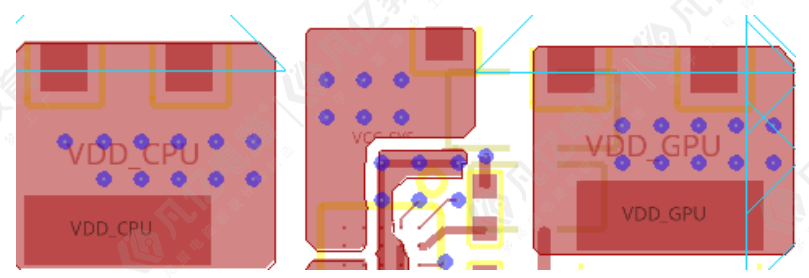

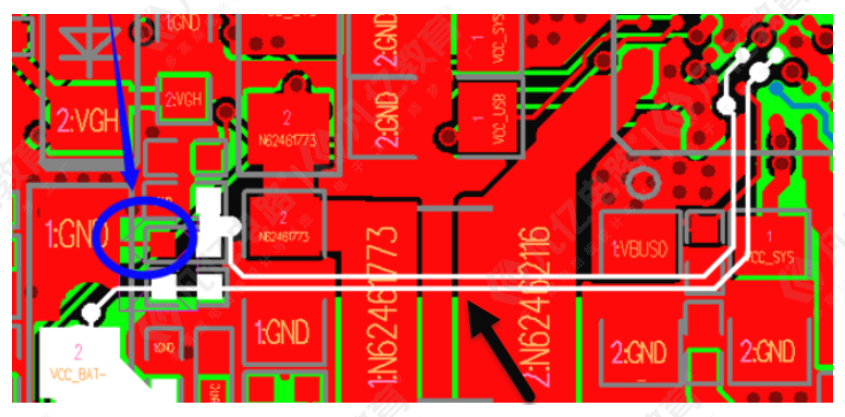

电源供电的设计至关重要,直接影响产品的性能及稳定性,请严格按RK3288电流参数要求进行设计。VDD_CPU、VDD_GPU及VDD_LOG主要为主控供电,峰值电流分别可达3.6A。从PMU的电源输出到主控相应电源管脚之间保证有大面积的电源敷铜,一般过载通道为3~5mm,承载过孔设置为0.3(孔)/0.5mm(盘),数量为8~14个,可提高过电流能力,并降低线路阻抗,如图15-9所示。

图15-9 供电面积及承载过孔

1)走线宽度的计算

PCB走线允许的最大电流的经验计算公式为

I = KT0.44 A0.75

式中,K为修正系数,一般敷铜在外层取0.048,敷铜在内层取0.024;T为允许的最大温升,单位为℃(摄氏度);A为敷铜的截面积,单位为mil2(注意:是mil2,不是mm2);I为允许的最大电流,单位为A(安培)。

以RK3288的VDD_CPU电源为例,峰值电流达到5A,假设电源走内层,铜厚为0.8mil(0.5OZ),允许的最大温升为10℃,那么PCB走线需要315.5mil。如果要进一步降低PCB电源走线的温升,就必须加大敷铜宽度。所以,如果PCB空间足够,建议尽量采用更宽的敷铜,以降低温升。

2)电源换层过孔数量的计算

计算一个过孔能通过多大电流,也可以利用上述公式。过孔的铜皮宽度计算公式为:L=pR。这里的R指过孔的半径。

以0.2mm孔径的过孔为例,铜皮厚度为0.8mil(0.5OZ),允许的最大温升为10℃,那么一个过孔约可通过420mA电流,想通过5A的电流至少需要13个0.2mm孔径的过孔。在面积有限的情况下,增大电源过孔的孔径可减少过孔数量。

3.FB反馈设计

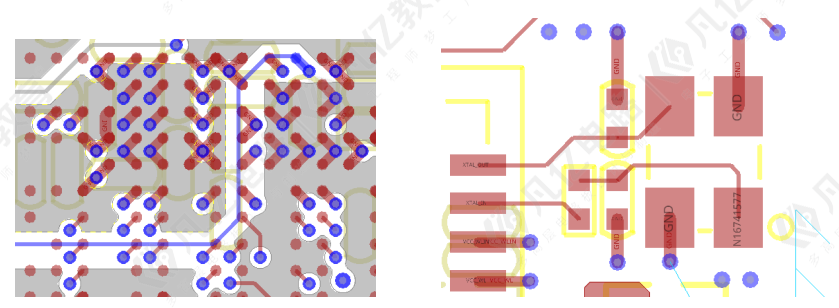

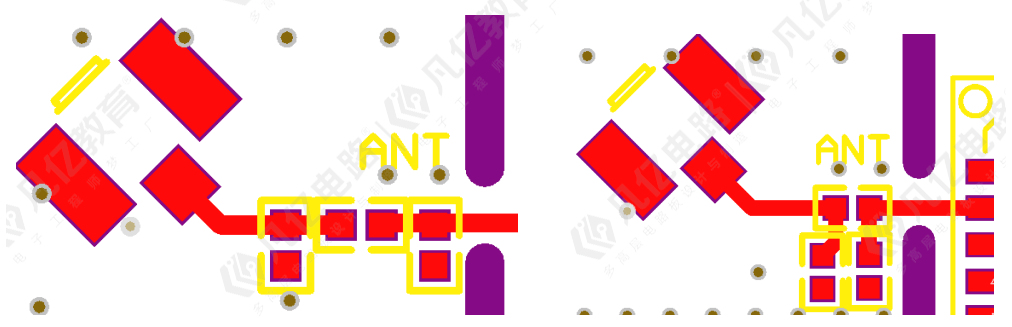

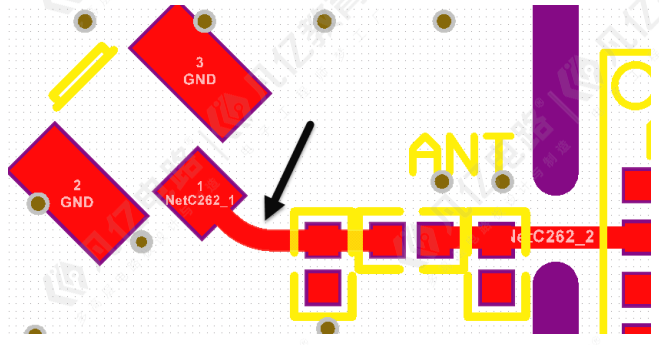

CPU_VDD_COM与GPU_VDD_COM反馈补偿设计,可弥补线路的电压损耗及提高电源动态调整及时性。如图15-10所示,图中点亮的走线即为VDD_GPU反馈补偿线,此补偿线另一端连接到电源输出DC/DC的FB端。走线需与PWR层并行走线,且不能被数据线干扰,否则有可能受其他信号串扰导致电压不稳定及振荡。走线宽度一般没有很大的要求,设置到10~15mil即可,不用太宽。

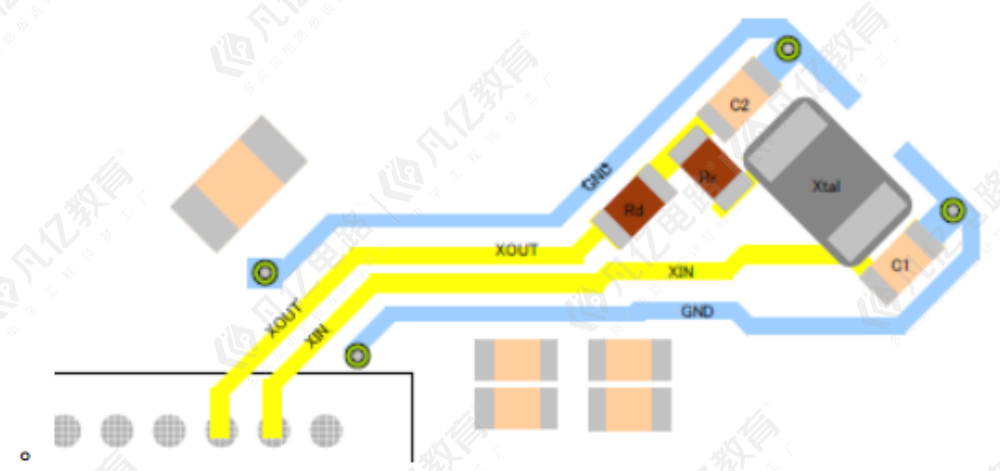

4.晶振的设计

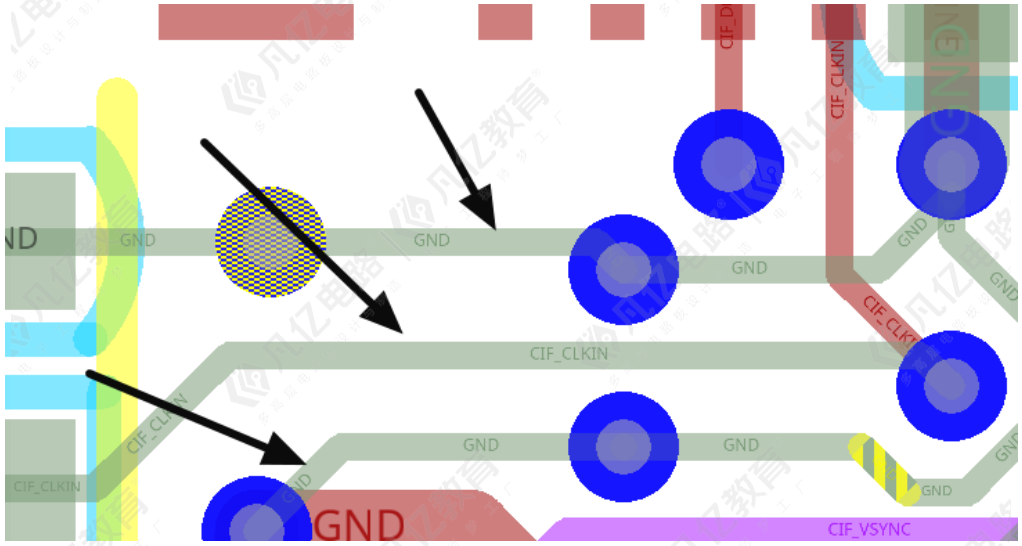

晶振是一个干扰源,本体表层及第二层禁止其他网络走线,并注意在晶振管脚及负载电容处多打地过孔。

晶振走线应尽量短,尽量不要打孔换层,走线和元件同面,并且采用p形滤波方式,如图15-11所示。

图15-10 CPU电源的反馈走线 图15-11 晶振的走线

5.其他设计

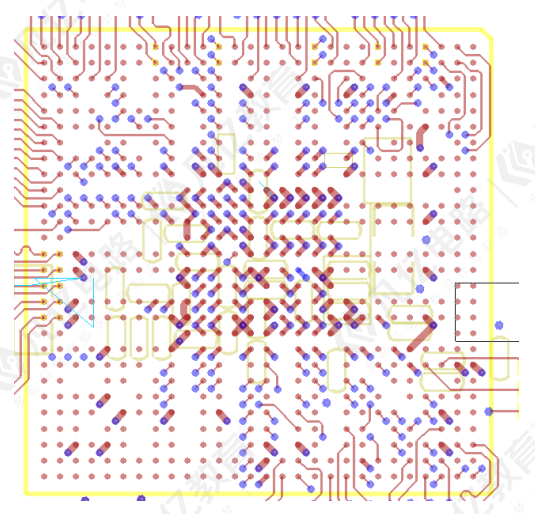

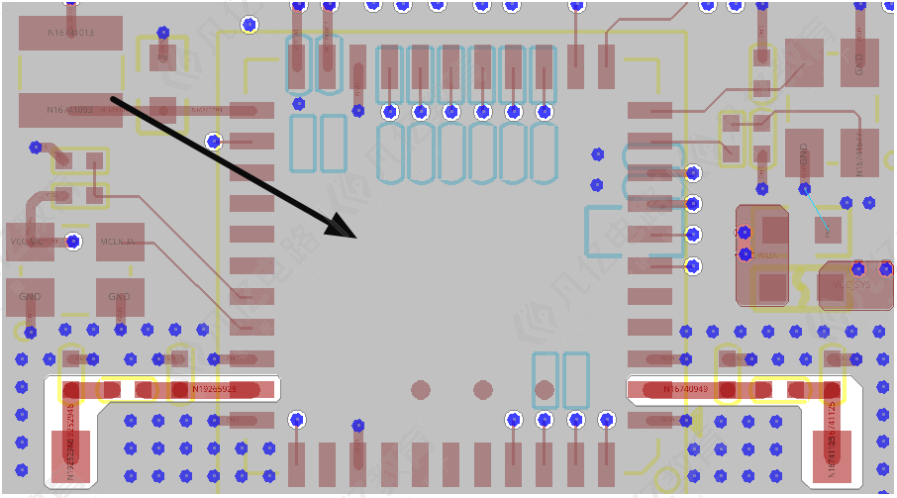

在主控下方的地过孔需要足够多,如图15-12所示,尽可能地多打,均匀放置并交叉连接,以改善电源质量,提高散热性,并提高系统的稳定性。电源信号也可以采用这种方式加大载流及散热。

图15-12 CPU地及电源的连接方式

15.5.2 PMU模块的设计

1.RC5T619电源模块的划分

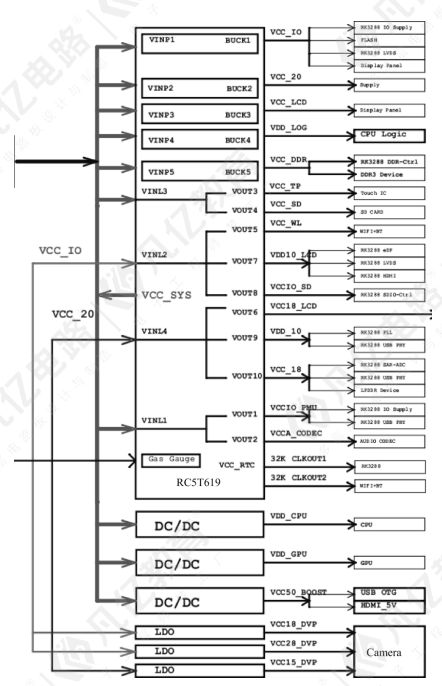

电源管理单元(PMU)是由传统分立的若干DC/DC及LDO组合而成的,这样可实现更高的电源转换效率、更低的功耗及更少的组件数,以适应缩小的板级空间。

设计的时候,可以按照分立的思维把PMU模块化,参考电源二叉树(如图15-13所示),明确输入及输出,对应PCB封装的管脚,这样就可以很清楚地知道哪些是主干道从而需要加粗敷铜来处理;同时,可以根据二叉树的电流参数并结合前文提到的敷铜宽度计算来很好地完成PCB的敷铜操作。

图15-13 PMU的电源二叉树

2.RC5T619的设计

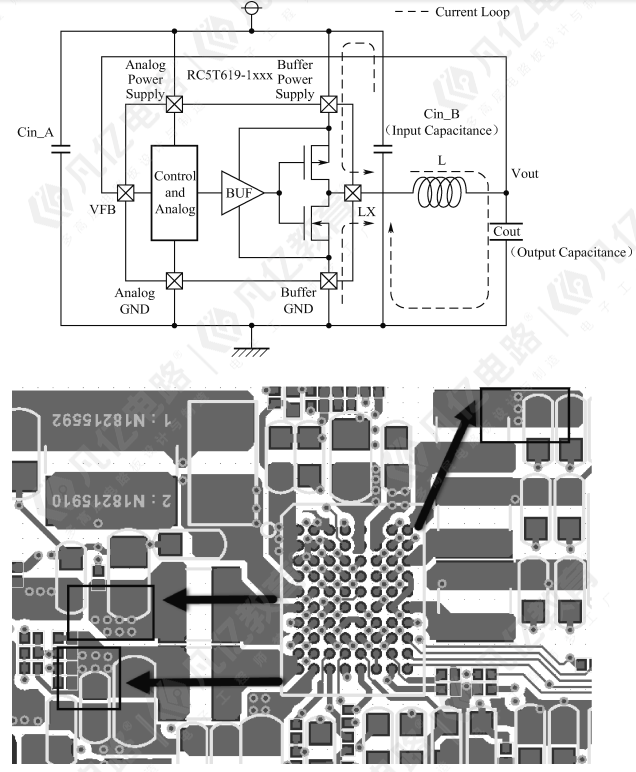

跟所有的DC/DC设计一样,一般进行设计之前,需要找到它的Datasheet,这样可以更方便、更好地设计好电源。

(1)保证输入、输出电容地尽量靠近芯片地,如图15-14所示,输入、输出电容的接地端需要根据供电电流的大小打相对应数量的过孔到主地上。

图15-14 PMU的处理

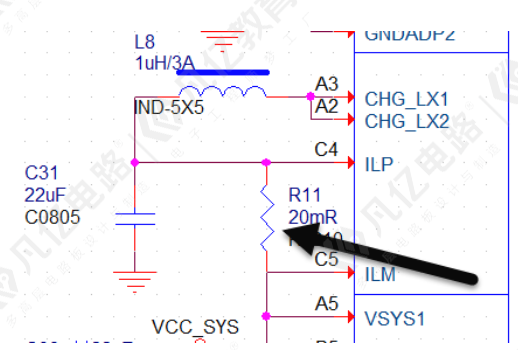

(2)RC5T619中有两个采样电阻。一个采样电阻是充电电流采样电阻R11,如图15-15所示,在PCB走线时需要从采样电阻R11的两端差分走线到C4与C5两个焊盘上,如图15-16中标记线所示,特别注意C5不能直接跟A5接在一起,否则会出现充电电流偏小的现象。

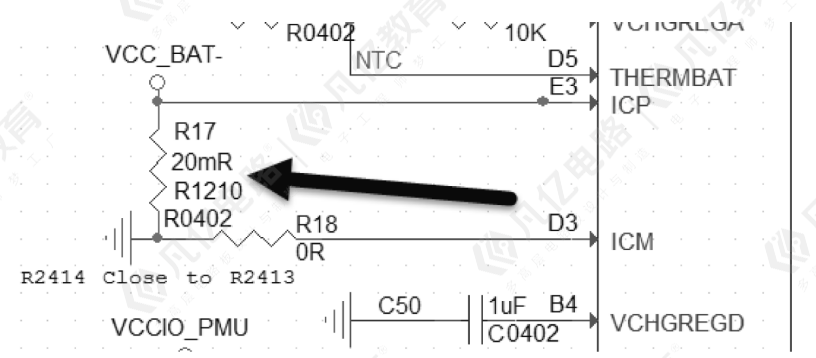

另一个采样电阻是电池端的电流采样电阻R17,如图15-17所示,布线时请务必将R18靠近R17,R18不直接与地连接,用Keepout隔开敷铜后单独拉线到R17焊盘上,ICP、ICM再差分走线到E3、D3两个焊盘上,如图15-18所示。

图15-15 充电电流采样电阻

图15-16 采样电阻R11差分走线

图15-17 电池端的电流采样电阻

图15-18 采样电阻R17差分走线

(3)进行32.768kHz晶振包地处理,第二层参考地平面,本体下尽量不要走其他数据线,以免对时钟造成干扰,并且走线越短越好,如图15-19所示。

图15-19 32.768kHz晶振包地处理

15.5.3 存储器LPDDR2的设计

LPDDR2(Low Power Double Data Rate2)的含义为低电压的DDR二代内存。在工作电压仅为1.2V的环境下,LPDDR2(1066)与DDR3(1066)具有同等的带宽,而DDR3的工作电压为1.5V,所以LPDDR2可以在更低的电压下达到DDR3的性能,相比DDR3可以降低50%以上的功耗,提高待机能力。

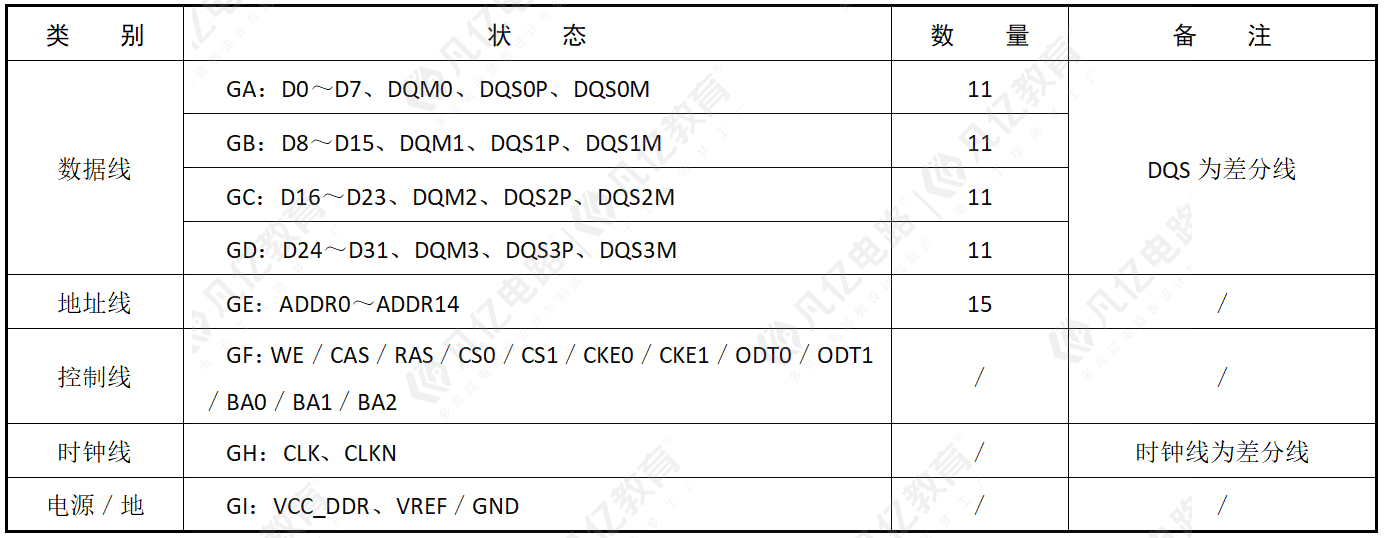

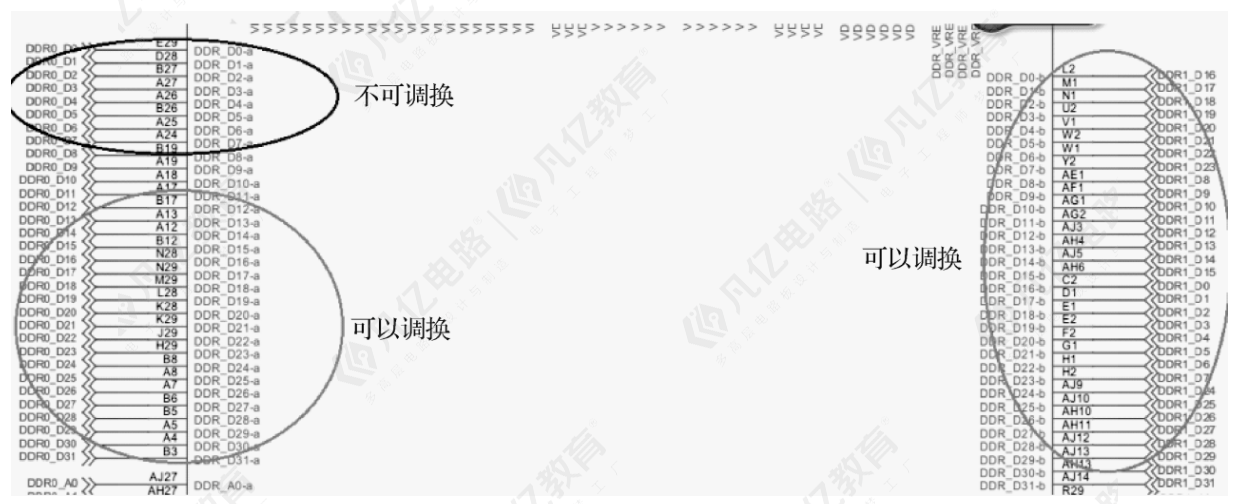

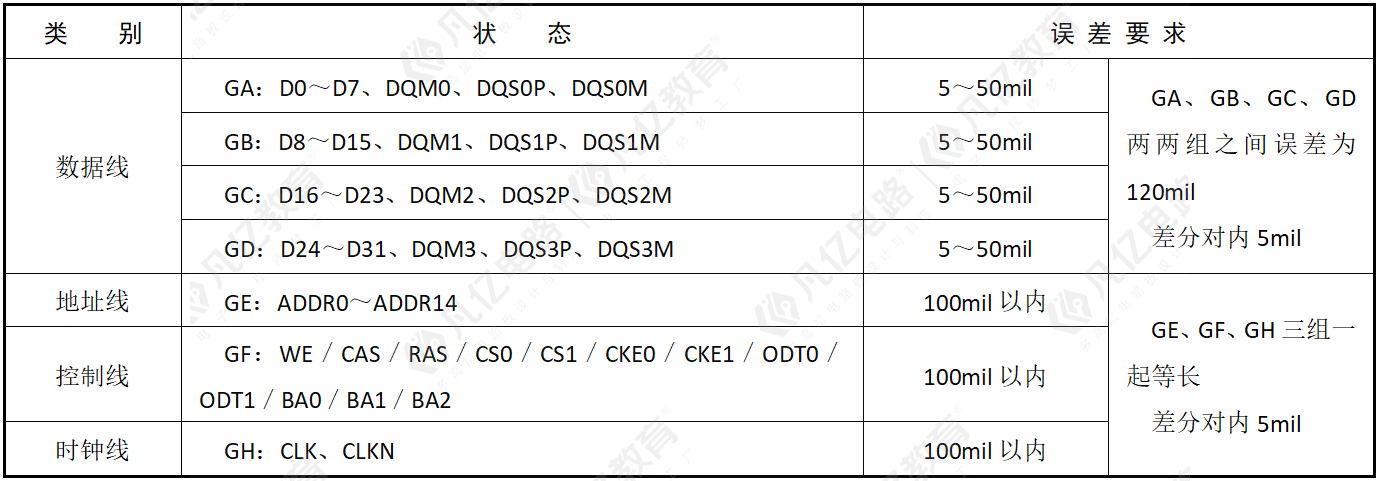

1.信号分类

可以对此实例的双通道LPDDR2的信号进行大致分类,如表15-4所示。

表15-4 LPDDR2的信号分类

(1)地址线、控制线与时钟线归为一组,是因为地址线和控制线在CLK的下降沿由DDR控制器输出,DDR颗粒在CLK的上升沿锁存地址线、控制线总线上的状态,所以需要严格控制CLK与地址线、控制线之间的时序关系,确保DDR颗粒能够获得足够的、最佳的建立/保持时间。

(2)地址线、控制线不允许相互之间进行调换。

(3)LPDDR2通道0的GA不能进行组内调换及组间调换,要求一一对应连接到颗粒的A或B通道的D0~D7,其余数据线(GB、GC、GD)可以进行组内调换(如DDR0_D8~D15随意调换顺序),或者进行组间调换(如GB与GC整组进行调换);通道1的所有组可以根据实际需要进行组内调换或组间调换,如图15-20所示。

图15-20 LPDDR2的信号调换情况说明

2.阻抗控制要求

数据线、地址线及控制线,单端走线控制50欧姆阻抗,DQS差分线和时钟差分线需要控制100欧姆差分阻抗。具体的走线线宽与间距可以参考阻抗叠层章节。

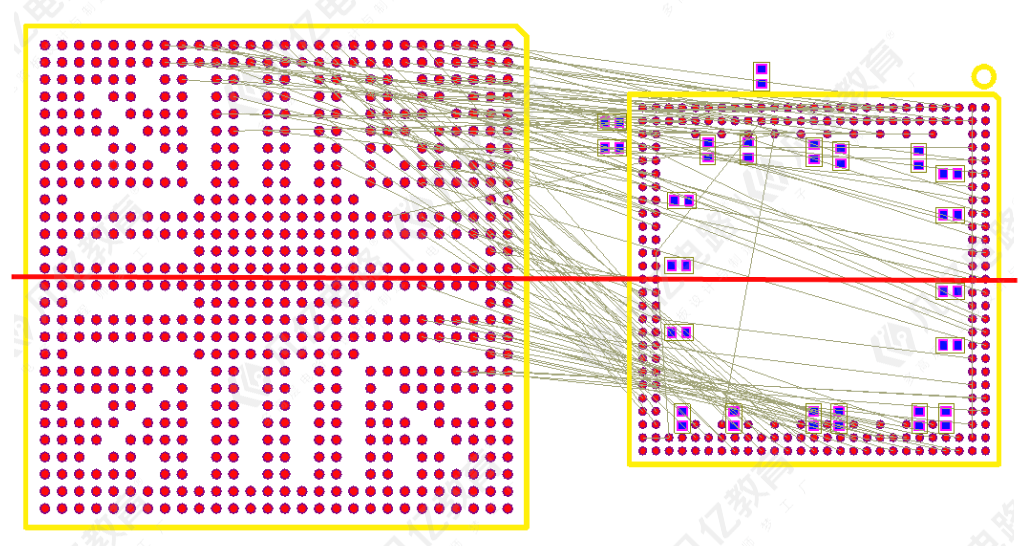

3.LPDDR2的布局

本实例中DDR为双通道LPDDR2,不存在T点或Fly-by拓扑结构,直接采用点对点的布局方式,并预留有等长的空间,不宜过近或过远,关于CPU中心对齐。LPDDR2滤波电容要靠近IC管脚摆放,可以考虑放到IC背面。RK3288和DDR颗粒的每个VCC_DDR管脚尽量在芯片背面放置一个退耦电容,而且过孔应该紧挨着管脚放置,以避免增大导线的电感。LPDDR2的布局如图15-21所示。

图15-21 LPDDR2的布局

4.LPDDR2的布线

(1)同组同层:为了尽量保证信号的一致性,数据线尽量做到同组同层,如GA组11条信号线走在同一层,GB组11条信号线走在同一层;地址线、控制线没有这个要求。

(2)3W原则:为了尽量减少串扰的产生,信号线之间满足3W原则,特别是数据线之间;组与组之间满足3W及以上间距;差分线与信号线间距满足3W及以上间距;差分Gap间距满足3W及以上间距,同时振幅不要超过180mil。

(3)平面分割:为了不使阻抗突变,所有属于DDR的信号线不允许有跨分割的现象,即不允许信号线穿越不同的电源平面。

(4)等长要求:有关要求如下。

① GA~GD组中数据线及DQSP、DQSM之间的线长误差控制在5~50mil(速率越高,要求越严格);每个组内的DQSP、DQSM差分对内误差控制在5mil以内;组与组的数据线不一定要求严格等长,但是尽量靠近,控制在120mil以内。

② GE、GF、GH组的信号线的线长误差控制在100mil以内,时钟差分需要控制对内误差5mil。

LPDDR2的等长要求如表15-5所示。

表15-5 LPDDR2的等长要求 (5)VREF的处理:VREF尽量靠近芯片;VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰);VREF只需要提供非常小的电流(输入电流大概为3mA);每一个VREF管脚都要靠近管脚加1nF旁路电容(每路电容数量不超过5个,以免影响电源跟随特性);线宽建议不小于10mil。

(5)VREF的处理:VREF尽量靠近芯片;VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰);VREF只需要提供非常小的电流(输入电流大概为3mA);每一个VREF管脚都要靠近管脚加1nF旁路电容(每路电容数量不超过5个,以免影响电源跟随特性);线宽建议不小于10mil。

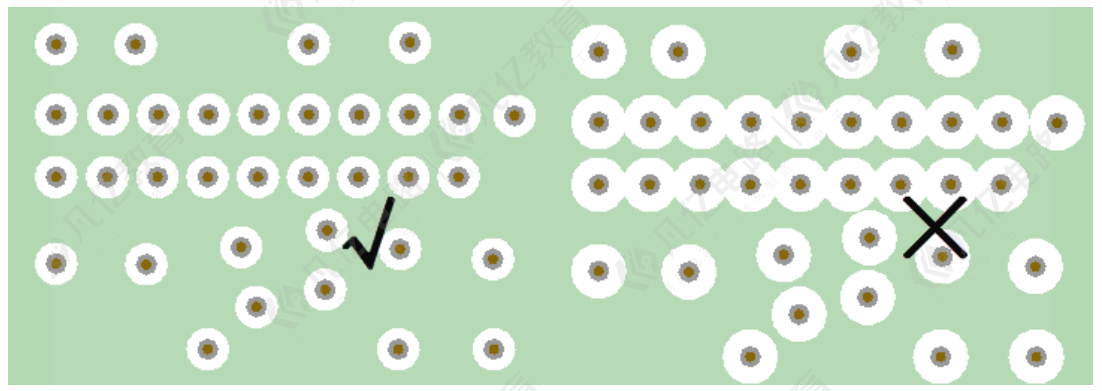

(6)保证平面完整性:DDR部分的平面完整性会直接影响DDR性能及DDR兼容性;在设计PCB的时候,注意过孔不能太近,以免造成平面割裂,一般推荐两孔中心间距大于32mil,两孔之间可以穿插铜线,如图15-22所示。

图15-22 LPDDR2的平面完整性

15.5.4 存储器NAND Flash/EMMC的设计

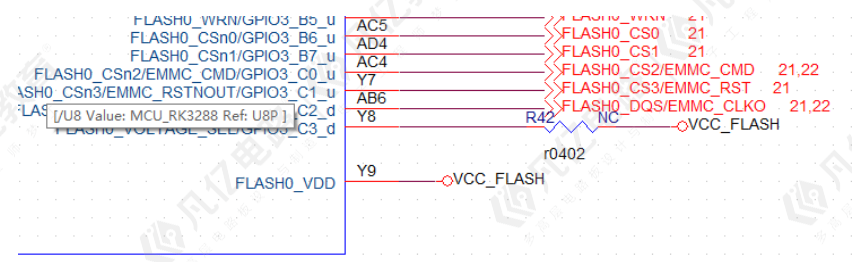

1.原理图

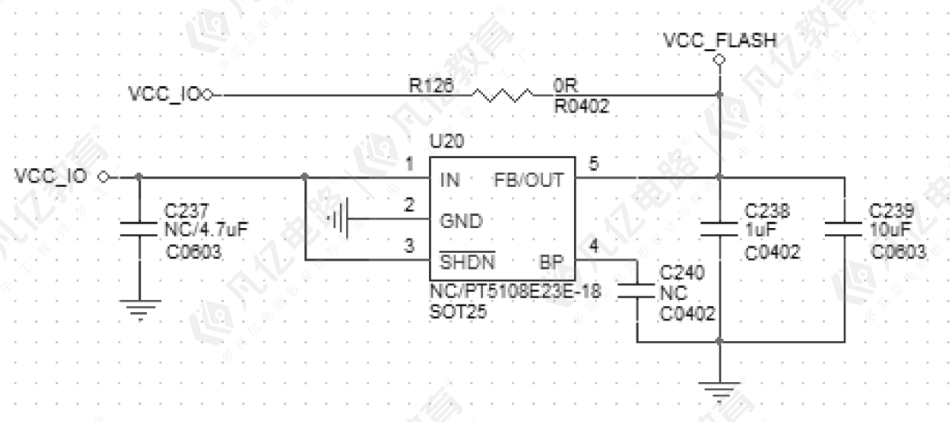

RK3288支持NAND Flash、EMMC等Flash存储设备。使用NAND Flash时,控制器及颗粒供电VCC_FLASH为3.3V。而不同版本的EMMC,控制器及颗粒供电VCC_FLASH可能为1.8V(EMMC4.1以上)或者3.3V,设计时根据Datasheet调整并修改。FLASH0_VOLTAGE_SEL默认3.3V时下拉到GND,1.8V时上拉到VCC_FLASH,如图15-23所示。

图15-23 FLASH0_VOLTAGE_SEL上拉状态

(1)EMMC在使用中,建议VCC_FLASH 使用1.8V供电,才能稳定跑高速。

(2)FLASH1通道不支持EMMC Flash。

(3)Boot默认由FLASH0通道引导,不可修改。

EMMC默认为1.8V LDO供电,如图15-24所示,可兼容EMMC4.1以下颗粒,可以使产品备料范围更广。

图15-24 EMMC供电兼容

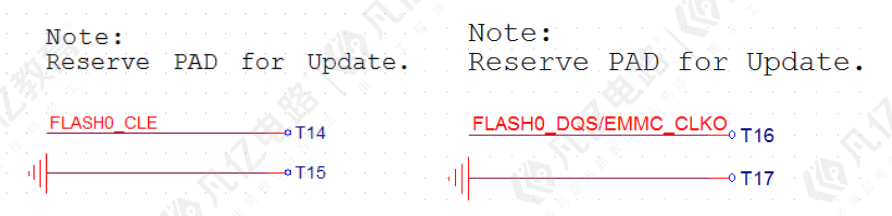

为了方便在开发阶段进入Mask Rom固件烧写模式(需要更新Loader),在使用NAND Flash时FLASH_CLE需预留测试点,而在使用EMM时EMMC_CLKO要预留测试点,如图15-25所示。

图15-25 测试点的添加

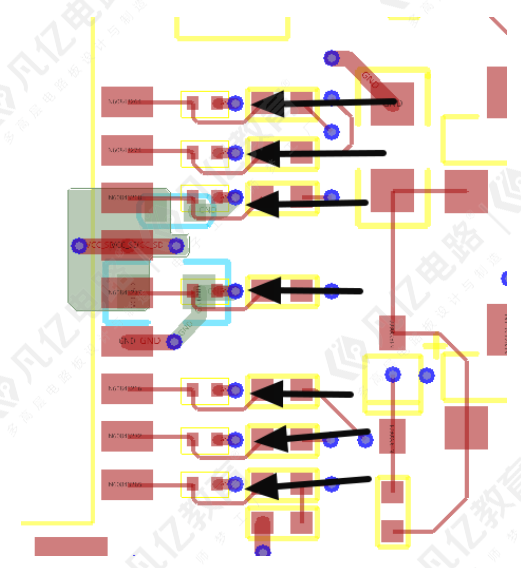

2.PCB部分

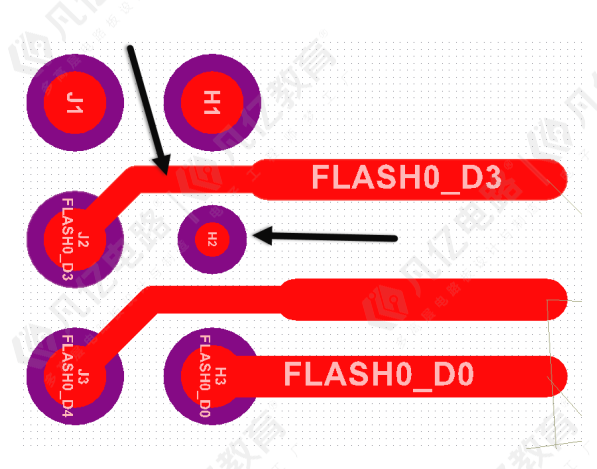

图15-26 EMMC的出线方式

(1)NAND Flash与EMMC一般通过双布线兼容设计,如图15-26所示。EMMC芯片下方在敷铜时,焊盘部分需要增加敷铜禁布框,避免铜皮分布不均匀影响散热,导致贴片时出现虚焊现象。

(2)走线尽量走在一起,并包地处理,空间准许的情况下可以等长处理,误差不要超过±100mil,以提高EMMC的稳定性和兼容性。

(3)EMMC处为BGA为0.5mm的Pitch间距,为了避免局部使用较小的线宽和间距提高整体生产难度及成本,无用的焊盘可以通过改小的办法出线,如图15-26所示。

15.5.5 CIF Camera/MIPI Camera的设计

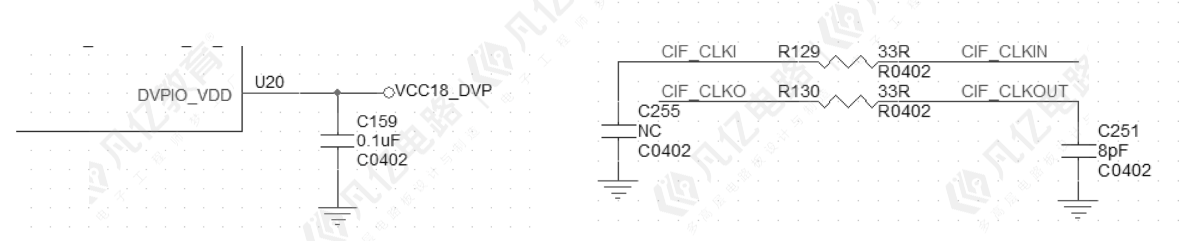

DVP接口电源域为DVPIO_VDD供电,实际产品设计中,需要根据产品Camera的实际IO供电要求,选择对应的供电电路(1.8V或2.8V),同时I2C上拉电平必须与其保持一致,否则会造成Camera工作异常或无法工作,如图15-27所示。

为了避免在实际产品中因Camera走线过长而造成时序问题,引起数据采集异常,需要增加如图15-28所示的RC延迟电路,同时在布线时走线尽量短。注意时钟信号的流向,对应的元件靠近信号输出端放置,PCLK上的电容靠近主控,电阻靠近Camera,MCLK上的电容靠近Camera,电阻靠近主控。

图15-27 DVPIO_VDD供电 图15-28 RC延迟电路

Camera信号走线CIF_D2~D9需按3W原则要求走线;为抑制电磁辐射,建议于PCB内层走线,并保证走线参考面连续完整;走线尽量少换层,因为过孔会造成线路阻抗的不连续;并做好整组包地。

CIF_CLKI、CIF_CLKO时钟走线,单独包地处理,包地线每隔50~100mil放置地过孔,并远离其他高速信号线,如图15-29所示。

数据线和MCLK、PCLK、HSYNC、VSYNC 的走线需等长,误差越小越好。

图15-29 Camera的包地处理

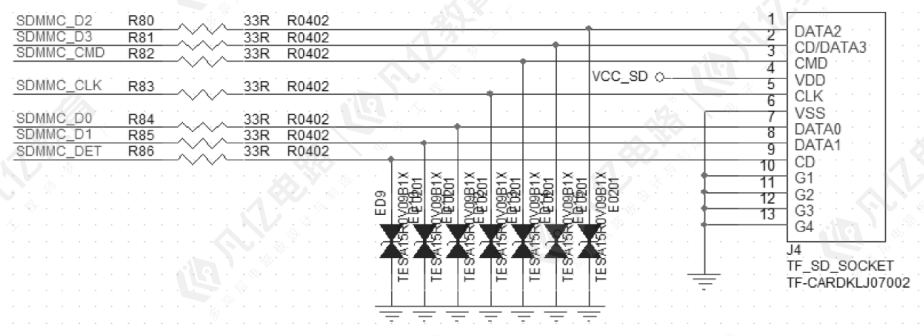

15.5.6 TF/SD Card的设计

TF Card电路兼容SD2.0/3.0,模块供电为输出可调的VCCIO_SD,默认为3.3V供电。TF为经常插拔的接口,建议增加ESD元件,如图15-30所示。

图15-30 TF的ESD元件

TF卡座VCC_SD电容C193、C194布局时靠近卡座管脚放置。走线尽量与高频信号隔开,尽量整组包地处理。如果有空间的话,CLK建议单独包地。TF Card走线要求信号组内任意两条信号线的长度误差控制在400mil以内,否则会导致SD3.0高速模式下频率跑不高。

RK3288平台上,TF Card的PCB布线长度尽量控制在15.4in以内,在结构设计及布局上要考虑这一点,以提高SDIO的稳定性和兼容性。

布局布线时,注意信号线要先经过ESD元件之后再进行引出,如图15-31所示。

图15-31 TF ESD元件的处理

15.5.7 USB OTG的设计

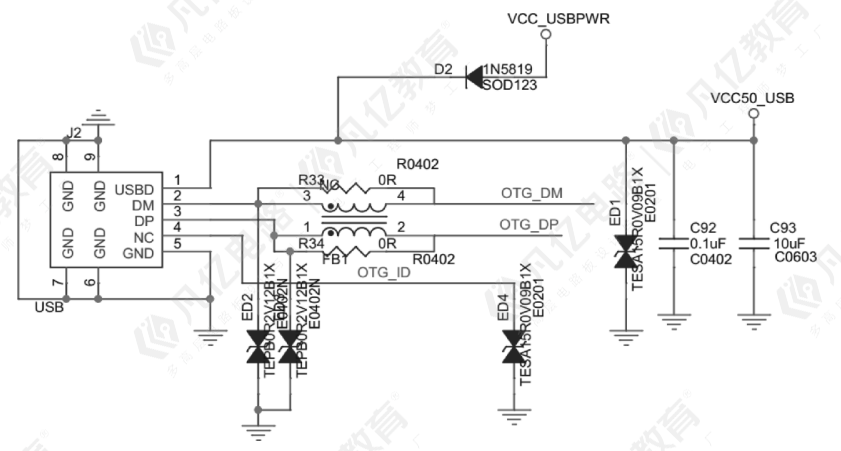

RK3288共有3组USB接口,其中一个为USB OTG,两个为USB HOST。USB OTG可以通过检测USB_VBUS、USB_ID信号,配置为Host或者Device功能,支持USB2.0/1.1规范。此实例支持一个USB OTG。

USB 控制器参考电阻R60、R61请选用1%精度的电阻,参考电阻关系到USB眼图的好坏。USB 具有高达480Mbps的传输速率,所以差分信号对线路上的寄生电容非常敏感,因此要选择低结电容的ESD保护元件,结电容要小于1pF。同时,为抑制电磁辐射,可以考虑在信号线上预留共模电感,在调试过程中根据实际情况选择使用电阻或者共模电感,如图15-32所示。

图15-32 USB OTG的设计

布线注意事项如下。

(1)USB差分走线越短越好,综合布局及结构进行调整。

(2)DP/DM 90欧姆差分走线,严格遵循差分走线规则,对内误差满足5mil。

(3)为抑制电磁辐射,USB建议在内层走线,并保证走线参考面是一个连续完整的参考面,不被分割,否则会造成差分线阻抗的不连续,并增加外部噪声对差分线的影响。空间充足的情况下进行包地处理。同时,尽量减少换层过孔,因为过孔会造成线路阻抗的不连续,实在需要的时候建议在打孔换层处放置地过孔。

(4)ESD保护元件、共模电感和大电容在布局时应尽可能靠近USB接口摆放,走线先经过ESD元件及共模电感之后再进入接口,如图15-33所示。

图15-33 USB OTG ESD元件的处理

(5)USB2.0规范定义的电流为500mA,但是USB_VBUS走线最好能承受1A的电流,以防过流。如果是在使用USB充电的情况下,USB_VBUS走线要能承受2.5A的电流。

15.5.8 G-sensor/Gyroscope的设计

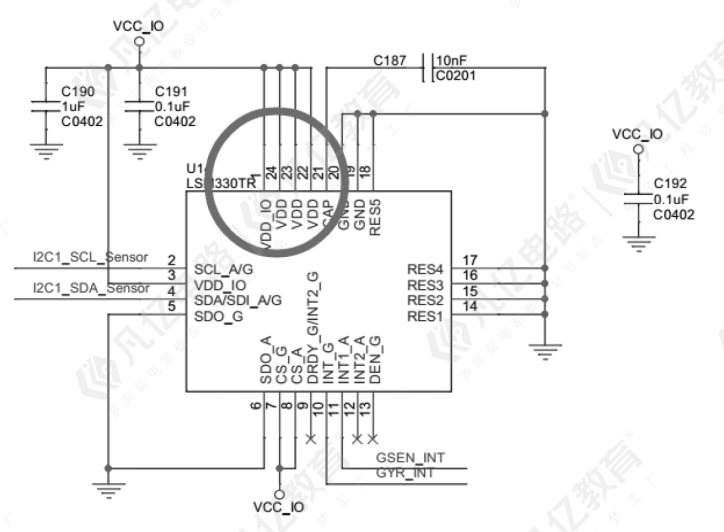

G-sensor/Gyroscope的VCC Supply和VCCIO Supply的电源域可能不一样,请确保I2C1总线上拉电源与G-sensor/Gyroscope的VCCIO Supply一致,否则需要进行电平匹配处理,如图15-34所示。

图15-34 G-sensor/Gyroscope电平

G-sensor/Gyroscope一般放置在板子的偏中心位置,不要太靠边,不然会影响其灵敏性。

G-sensor/Gyroscope在布局的时候,第1脚方向一般有一定的要求,如都朝左上角放置,这主要是看公司的习惯,建议与RK提供的SDK保持一致,方便软件调试。

15.5.9 Audio/MIC/Earphone/Speaker的设计

1.Audio(音频)的设计

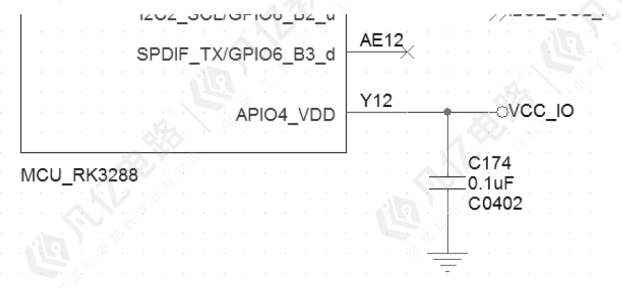

Codec I2S接口电源域为APIO4_VDD供电,实际产品设计中,需要根据Codec的实际IO供电要求,选择对应的供电电路(1.8V或3.3V),同时I2SC上拉电平必须与其保持一致,否则会造成Codec工作异常或无法工作,此实例选择3.3V(VCC_IO),如图15-35所示。

图15-35 APIO4_VDD供电

PCB设计注意事项如下。

(1)Codec布局时应靠近连接座放置,走线尽可能短。

(2)为了保证供电充足,Codec各路电源走线线宽要求大于15mil,VCC_SPK走线线宽要求大于30mil。

图15-36 MIC耦合电容的放置

(3)Codec各输入、输出信号包括HP OUT、LINE IN、LINE OUT、MIC IN、SPDIF、SPEAKER OUT等信号,为避免信号间串扰引起的输出失真及噪声,均需要进行包地处理(包地处理应包括同层包地与邻层包地),并与其他数字信号隔离。

(4)音频走线为模拟线,HP OUT信号线宽建议大于15mil,LINE IN/OUT信号线宽建议大于10mil。

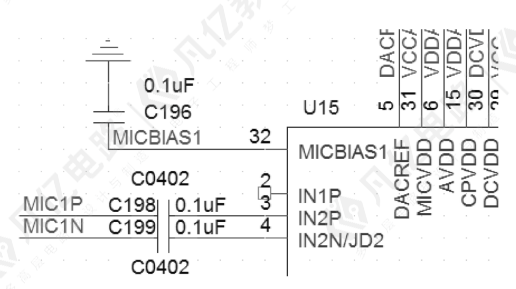

(5)MIC IN信号比较敏感,为避免引入噪声,MIC的耦合电容要靠近Codec端放置,如图15-36所示。

2.MIC(咪头)的设计

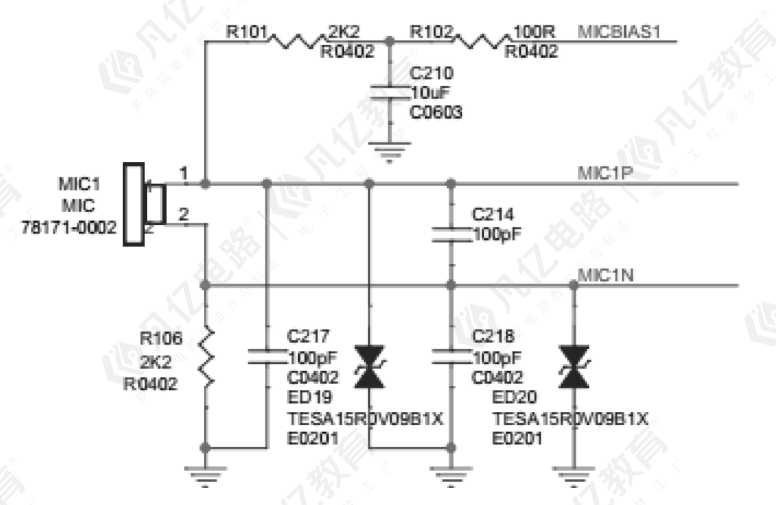

MIC根据所选型的驻极体麦克风规格,选择合适的分压电阻R101、R106,如图15-37所示。

图15-37 MIC分压电阻的选择

布线时,MIC1P与MIC1N差分走线加粗到10~12mil,并且尽量立体包地处理,尽量远离高速线,减少对其的干扰。

3.E(耳机)的设计

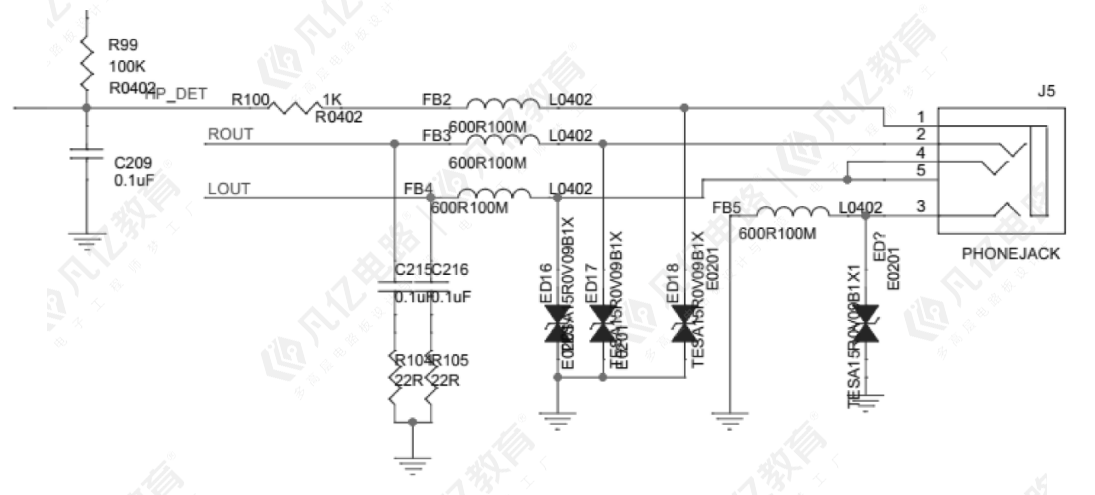

耳机的设计如图15-38所示。

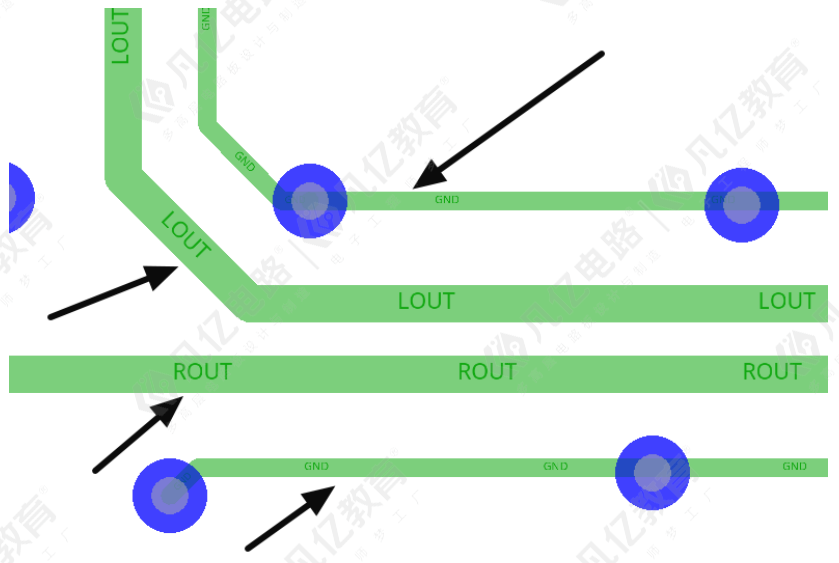

耳机信号走线同样属于音频信号,LOUT、ROUT左、右声道走线需要加粗处理,类似于差分走线,并且立体包地,尽可能地避免其他走线对其的干扰,如图15-39所示。

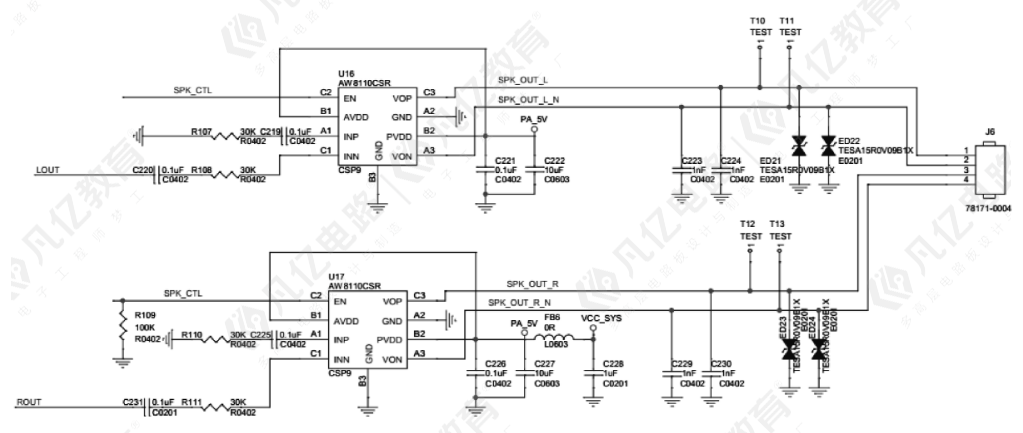

4.Speaker(喇叭)的设计

为抑制功放电磁辐射,需把功放到喇叭的走线缩短,并加粗,尽量少走弯角。为避免噪声干扰,建议差分走线,线宽大于20mil,线距小于10mil,并在靠近喇叭输出端预留LC滤波电路,如图15-40所示。

图15-38 耳机的设计

图15-39 耳机信号走线

图15-40 Speaker的设计

15.5.10 WIFI/BT的设计

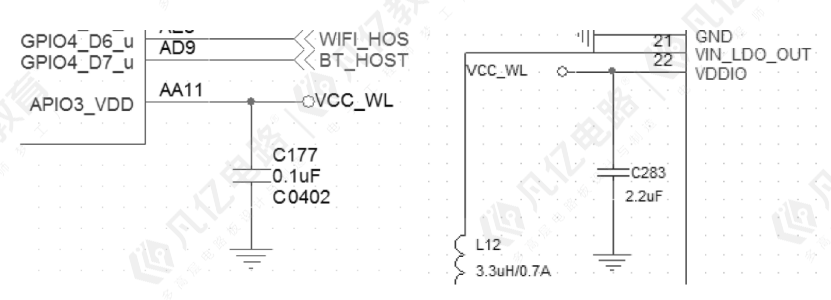

(1)RK3288支持SDIO3.0接口的WIFI/BT模块,采用SDIO、UART接口的WIFI/BT模块时,需要注意RK3288 SDIO、UART控制器的供电APIO3_VDD要与模块VCCIO Supply一致,如图15-41所示。

图15-41 APIO3_VDD供电

在SDIO3.0情况下,APIO3_VDD 供电必须为1.8V。

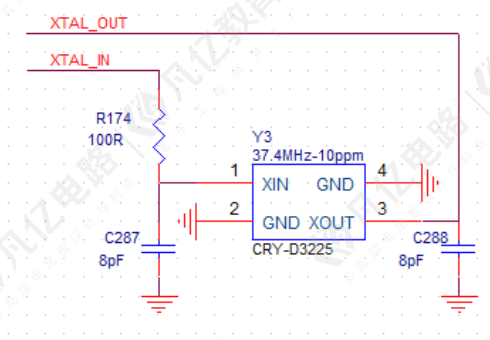

(2)请注意WIFI需选择ESR小于60ohm、频偏误差小于20ppm的晶振。对于晶振的匹配电容,请根据晶振规格选择合适的电容值,避免频偏太大而出现的工作异常(如热点数较少等),如图15-42所示。

(3)预留SDIO上拉电阻,当WIFI使用SDIO3.0时,上拉电阻(图15-43所示)贴片可提高信号质量。

图15-42 晶振的选择 图15-43 SDIO上拉电阻

(4)AP6×××的VBAT供电电压范围为3.0~4.8V,供电电流最小为400mA,布线时要注意。

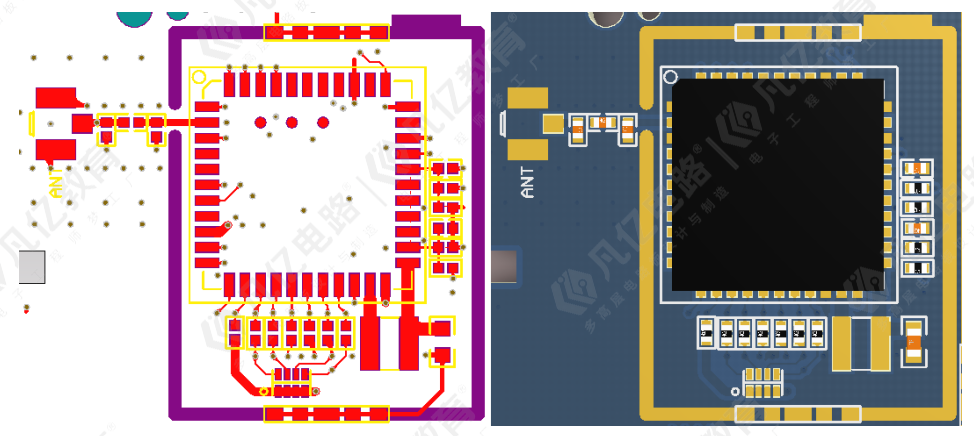

(5)WIFI/BT模块属于易受干扰的模块,PCB布线时注意远离电源、DDR等模块,在空间充足的情况下,建议添加屏蔽罩,如图15-44所示。

图15-44 WIFI/BT模块的屏蔽罩

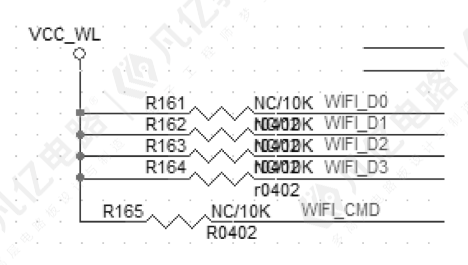

(6)模块的VBAT和VDDIO的电源脚4.7mF去耦电容C272、C283需靠近模块放置,并尽可能与模块摆放于同一平面。模块内部电源的电感L12和电容C286需靠近模块放置,走线线宽大于15mil,如图15-45所示。

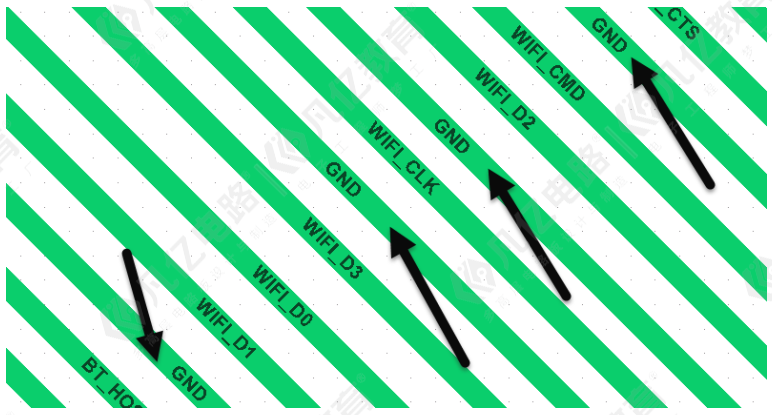

图15-45 电感与电容的放置

(7)SDIO走线作为数据传输走线,需尽可能平行,并进行整组包地处理。如果有空间的话,CLK建议单独包地。需避免靠近电源或高速信号布线。同时,信号组内任意两条信号线的长度误差控制在400mil以内,尽量等长,否则会导致SDIO3.0,高速模式下频率跑不高。SDIO走线处理如图15-46所示。

图15-46 SDIO走线处理

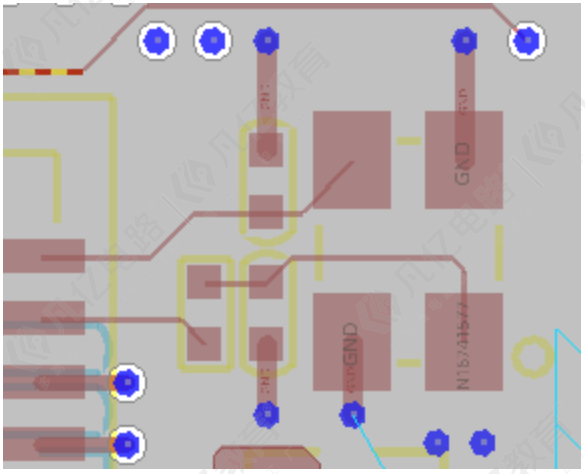

(8)如图15-47所示,同样是为了避免干扰,模块下方第一层保持完整的地,不要有其他信号走线,其他信号走线尽量走在内层。

图15-47 WIFI/BT模块的地平面处理

(9)晶振本体下方保持完整的地,不要有其他信号走线,晶振管脚要有足够的地过孔进行回流,如图15-48所示。

图15-48 晶振的处理

(10)天线及微带线宽度设计需考虑到阻抗,阻抗严格为(50±10)ohm。走线下方需有完整的参考平面作为RF(射频)信号的参考地,天线布线越长,能量损耗越大,因此在设计时,天线路径越短越好,不能有分支出现,不能打过孔。图15-49所示为WIFI/BT天线错误的走线方法。天线走线需转向时,不可以用转角的方法,需用弧形走线。图15-50所示为WIFI/BT天线正确的走线方法。

图15-49 WIFI/BT天线错误的走线方法

图15-50 WIFI/BT天线正确的走线方法

扫码关注

扫码关注