规则设置是PCB设计中至关重要的一个环节,可以通过PCB规则设置,保证PCB符合电气要求和机械加工(精度)要求,为布局、布线提供依据,也为DRC提供依据。

对于PCB设计,这些设计规则包括电气、元件放置、布线、元件移动和信号完整性等规则。对于常规的电子设计,不需要用到全部的规则,为了使读者能直观地快速上手,这里只对最常用的规则设置进行介绍说明。按照下面的方法设置好这些规则之后,其他规则可以忽略设置。

10.2.1 规则设置界面

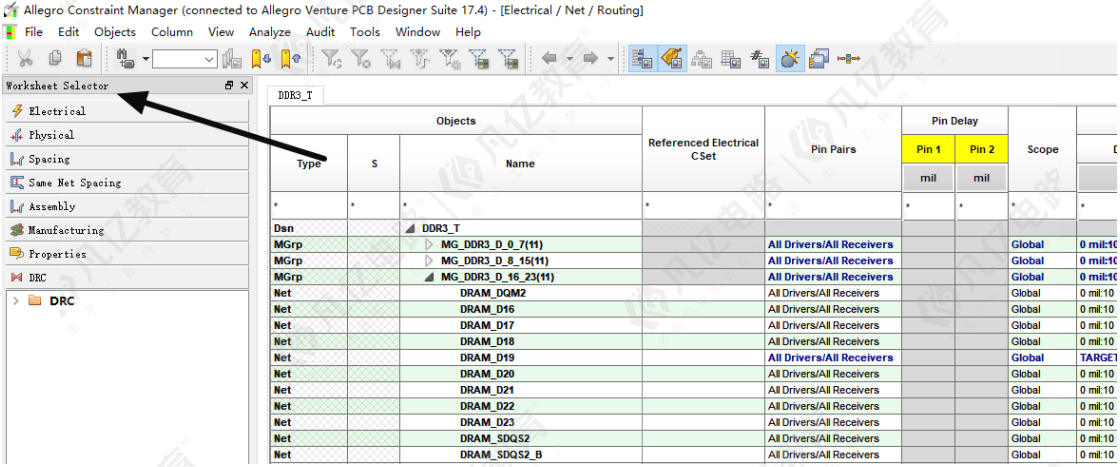

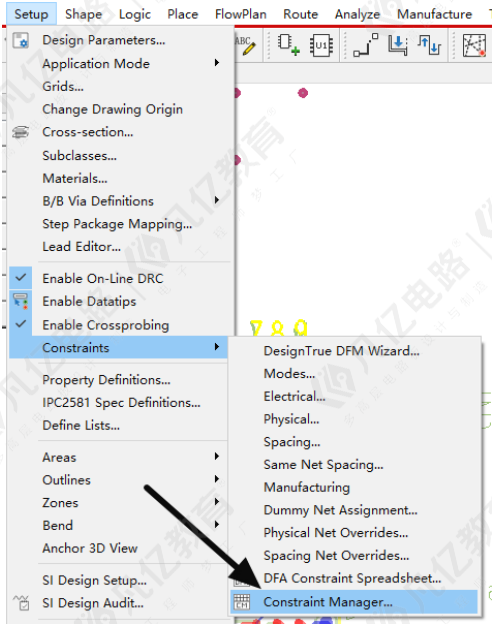

执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器,在左边Worksheet Selector里面的选项中进行常用规则的设置,如图10-18所示。

图10-18 规则设置界面

10.2.2 线宽规则设置

我们布局完成之后,计算好阻抗线宽之后呢,就要开始进行布线操作,在布线之前,我们需要添加走线的规则,这样走出来的线宽才是阻抗线宽,具体添加阻抗线宽的详细步骤如下所示:

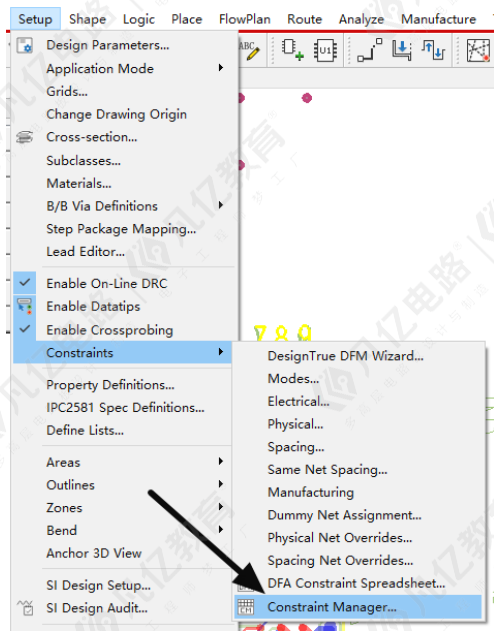

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器,如图10-19所示。

图10-19 规则管理器示意图

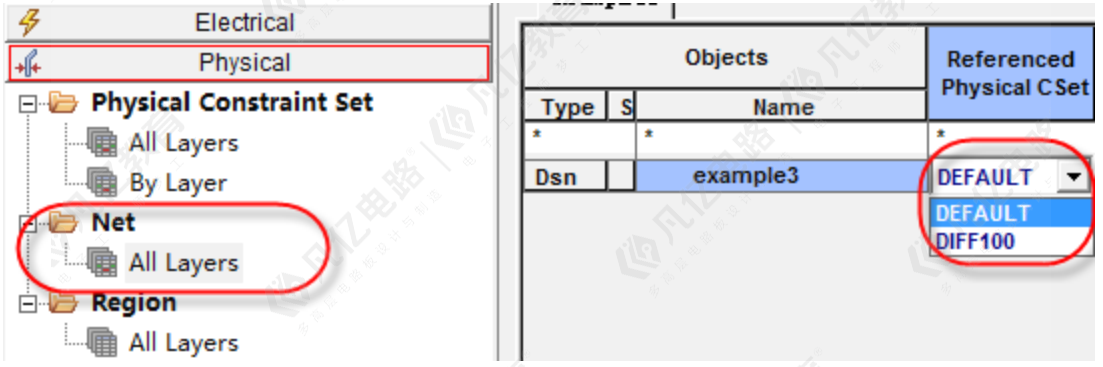

(2)进入规则管理器之后,点击左侧侧边栏,点击Physical,这是设置物理规则,主要是管控信号走线的线宽以及差分信号线宽线距,如图10-20所示

图10-20 物理走线线宽设置示意图

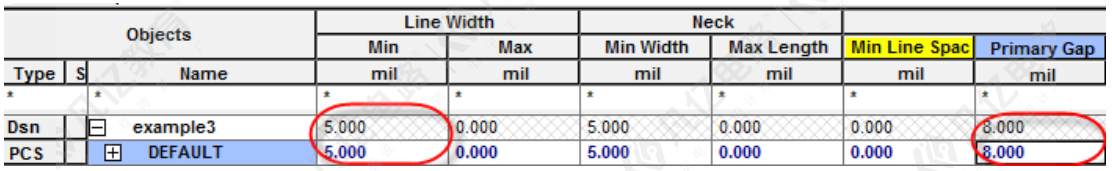

(3)我们现在需要添加走线的阻抗线宽,单端阻抗是走6mil,差分阻抗是走5mil,线距控制8mil,我们按照这个添加一下,单端直接使用默认的Default规则进行添加,在Line Width中的Min栏中输入6mil即可,Max表示的含义是PCB允许走的最大的线宽;

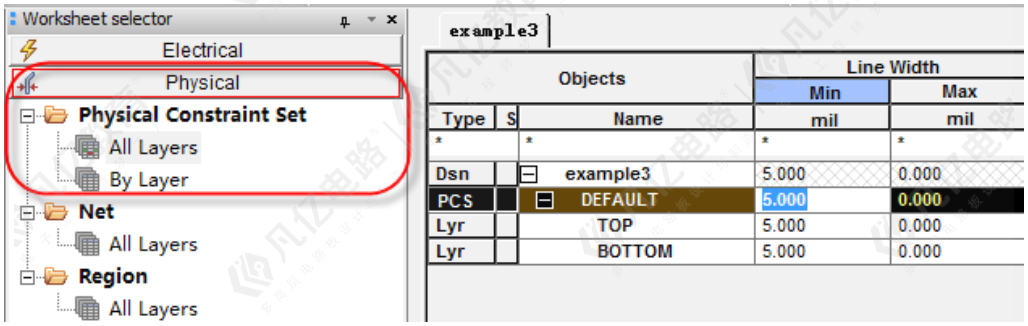

(4)差分线宽的添加,新建一个规则,点击默认的规则,点击鼠标右键,执行命令Create-Physical CSet,如图10-21所示,然后在弹出的对话框中输入物理规则的名称,例如DIFF100,然后在定义差分的规则即可;

图10-21 创建新的物理规则示意图

(5)差分规则的定义与单端的规则定义是一致的,Line Width中的Min栏中输入5mil表示差分走线的线宽,在Primary Gap间距中输入8mil表示差分走线的间距,如图10-22所示;

图10-22 差分走线规则设置示意图

(6)在上述规则添加中,我们只是对走线规则进行了设定,但是软件系统并不知晓哪些网络需要走50欧姆阻抗,哪些网络需要走100欧姆阻抗,所以呢,我们还需要对网络进行驱动,在左侧边栏选取Net,然后右侧会显示所有整个PCB板的网络,根据走线的具体需求,在规则设置栏选择对应的驱动规则即可,如图10-23所示

图10-23 走线规则驱动示意图

10.2.3 间距规则设置

添加完成走线的阻抗线宽之后,这样PCB板上信号走线就会按照所设置的物理走线线宽进行。除了添加走线的线宽之外,还需要添加间距规则,来规范不同元素之间的间距,满足生产的需求,添加间距的操作步骤如下所示:

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器,如图10-24所示

图10-24 规则管理器示意图

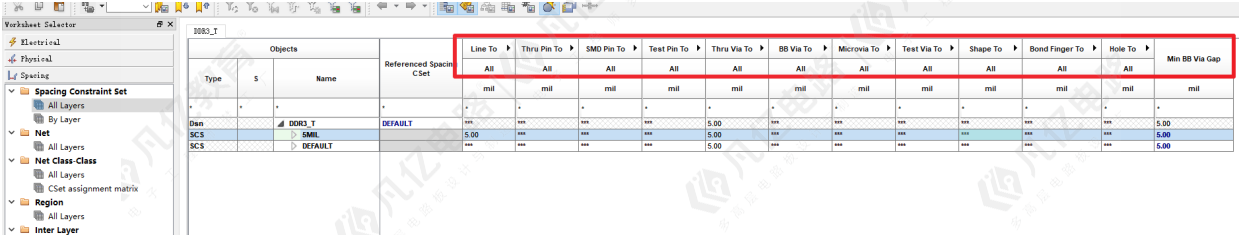

(2)进入到规则管理器设置界面以后,在左侧边栏选择Spacing间距规则设定,如图10-25所示,点击打开All Layer,可以看到PCB板上所有需要设置间距规则的元素都会显示,然后在下方设置间距大小。

图10-25 间距规则设定示意图

图10-25 间距规则设定示意图

(3)一般推荐设置间距规则时,规则设置大一些,例如走线到过孔、焊盘等元素的规则设置为6mil,铜皮到其它元素之间的间距设置为15mil,定位孔到其它元素之间的间距设置为20mil。

10.2.4 多种间距规则设置

在PCB设计中,往往在某些地方需要设置特殊的间距规则,因此我们需要添加多个间距规则,以方便后面设置区域规则中进行驱动。

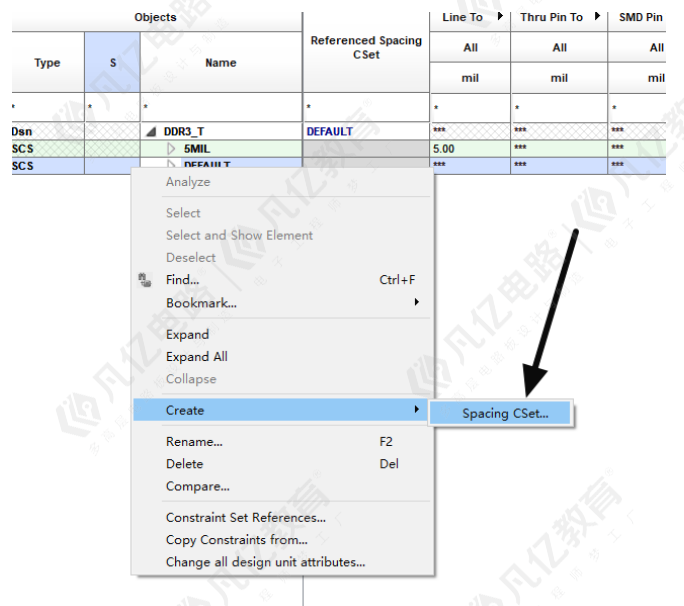

(1)在间距规则设置界面的SCS栏处单击右键,创建一个新的间距规则,如图10-26所示。

图10-26 创建间距规则

(2)在弹出的窗口对新建的规则进行命名,如图10-27所示。

图10-27 新规则命名

(3)然后对新建的规则设置各种元素之间的间距大小,具体数值根据实际设计进行设置。

10.2.5 相同网络间距规则规则设置

ALLEGRO软件提供了相同网络的间距规则设置,以满足在PCB设计中的一些特殊情况。

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器。

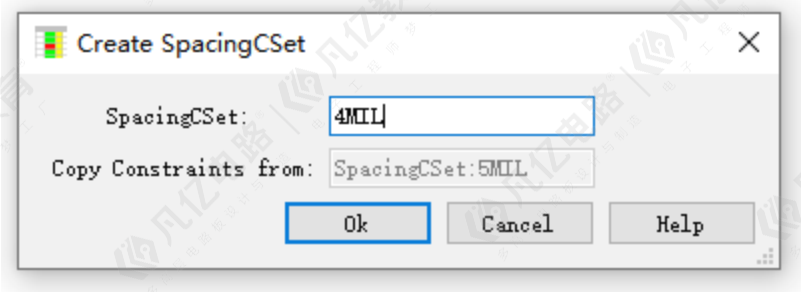

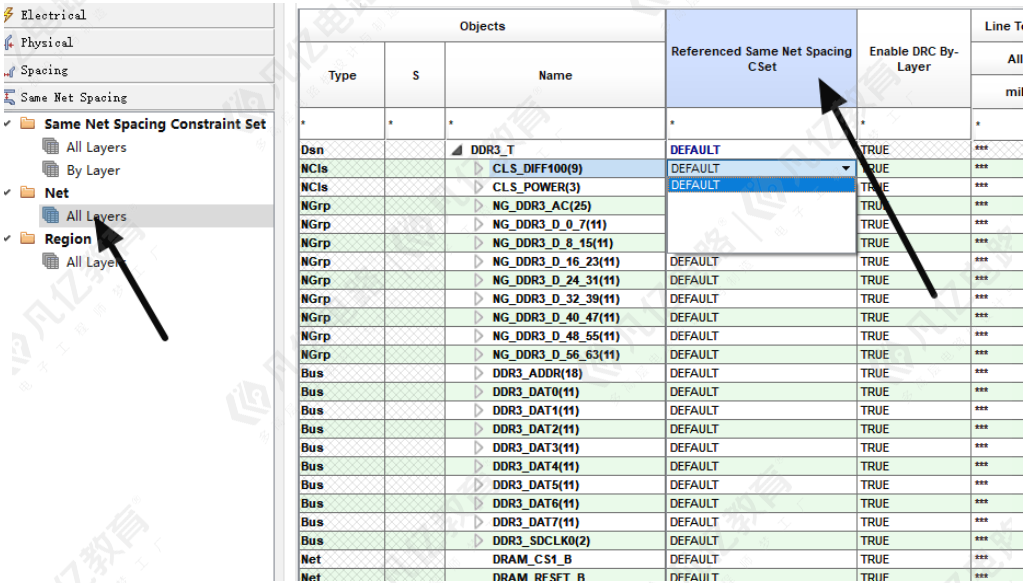

(2)进入到规则管理器设置界面以后,在左侧边栏选择Same Net Spacing间距规则设定,如图10-28所示,点击打开All Layer,可以看到PCB板上所有需要设置间距规则的元素都会显示,然后在下方设置间距大小。

图10-28 相同网络间距规则设定示意图

图10-28 相同网络间距规则设定示意图

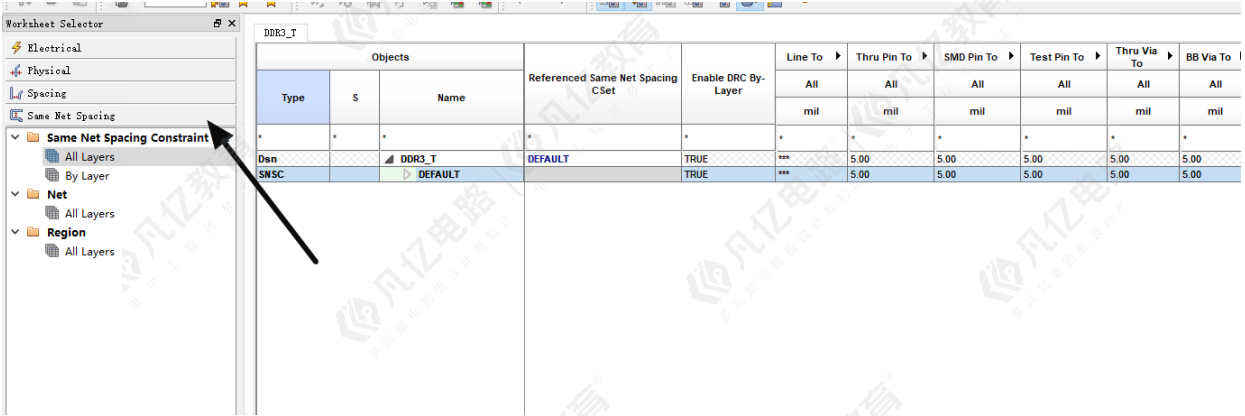

(3)设置完成之后,在Net选项中选择相应的网络进行规则驱动,如图10-29所示。

图10-29 间距规则驱动示意图

10.2.6 特殊区域规则设置

区域规则就是在整个PCB板的规则都添加好了,有一块区域单独拉出来,服从另一个规则,在这块区域所应用的这个规则呢,我们就称之为区域规则,一般多用于BGA器件区域,下面我们讲解一下,如何添加区域规则,具体的操作步骤如下:

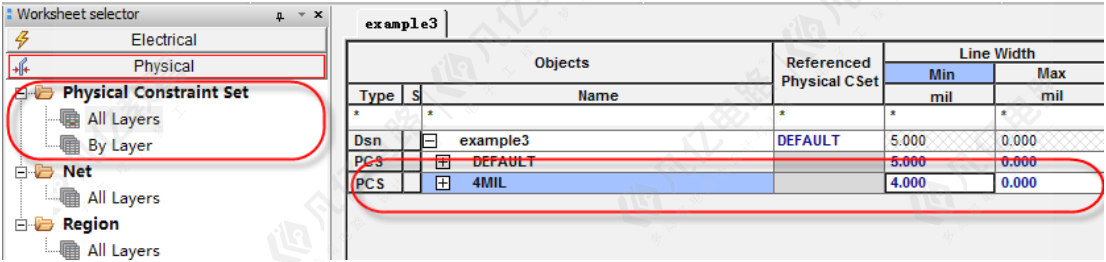

(1)需要设置区域规则的内容,物理走线与间距都是可以添加区域规则的,我们以走线为例,讲解下如何去添加,如图10-30所示,默认的规则走线是5mil,我们定义区域内的走线是4mil,点击右键新建一个物理规则,设置走线的宽度为4mil,如图10-29所示。

图10-30 定义4mil走线的物理规则示意图

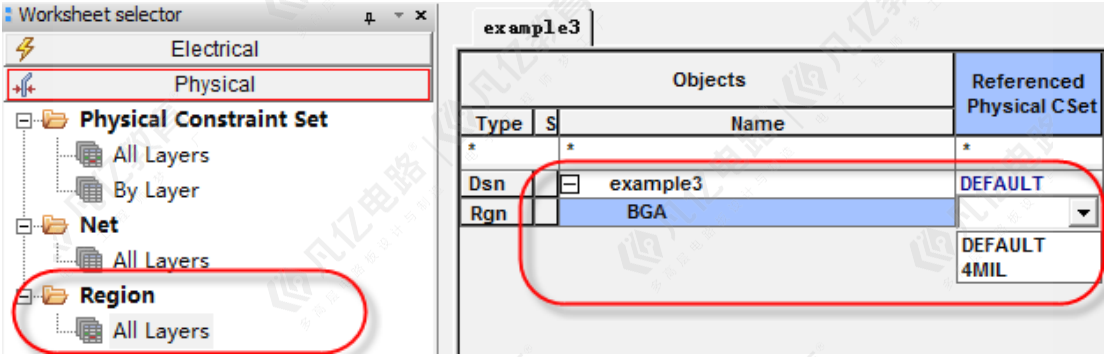

(2)定义好4mil走线的物理规则以后,我们还需要去定义一个区域,在这个区域内满足的规则就是4mil,在CM左侧侧边栏中选择Region,在右侧中点击鼠标右键,执行菜单命令Create-Region,如图10-31所示,然后在弹出的对话框中输入名称,比如BGA,说明这是BGA区域所使用的规则。

图10-31 定义规则应用区域示意图

(3)定义好区域以后,我们要对这个区域的规则进行指定,在规则驱动栏中选择我们之前添加好的4mil规则,这样BGA区域就符合4mil的规则要求了,在这个区域内走出来的线宽就是4mil,如图10-32所示。

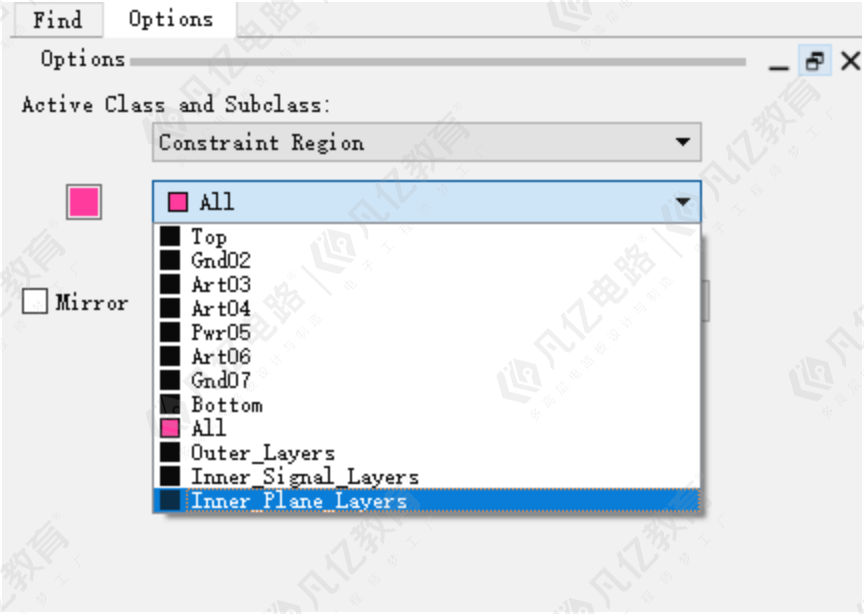

图10-32 规则驱动示意图

(4)区域规则设定完毕之后,我们直接在PCB上添加区域框即可,在需要添加区域规则的位置,使用铜皮去添加即可,需要注意的是,我们绘制的铜皮的层必须是Constraint Region层,subclass层的选择,根据需要选择即可,在所有层生效就选择All,如果只在对应的层生效,那只要选择对应的层即可,如图10-33所示。

图10-33 绘制区域框示意图

5)绘制完成区域框之后,还需要指定名称,选中刚才绘制好的区域框,单击鼠标右键,选择Assign Region命令,在Options面板中选择在规则管理器中添加好的BGA即可,这样,在所绘制的这个区域就满足BGA区域的规则了。

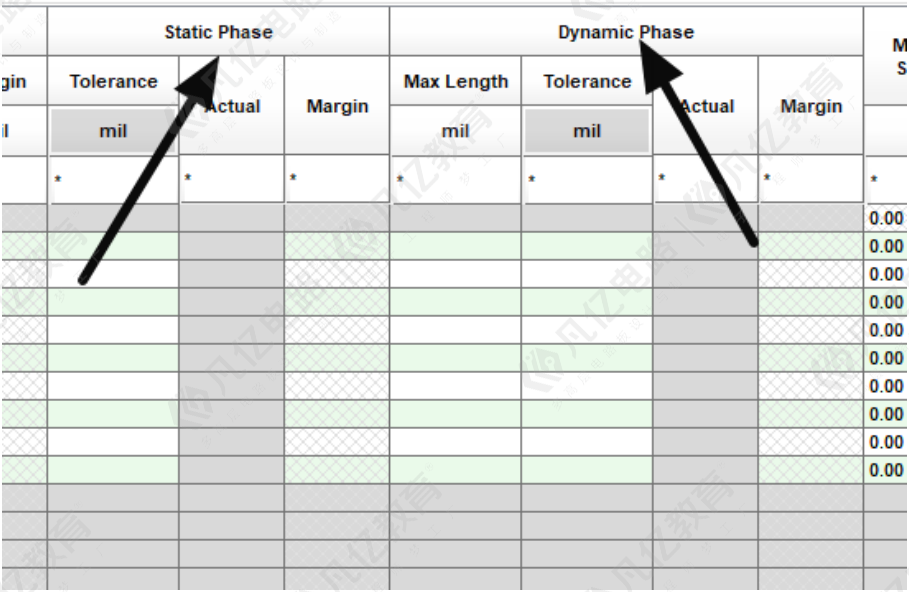

10.2.7 差分动态和静态等长规则设置

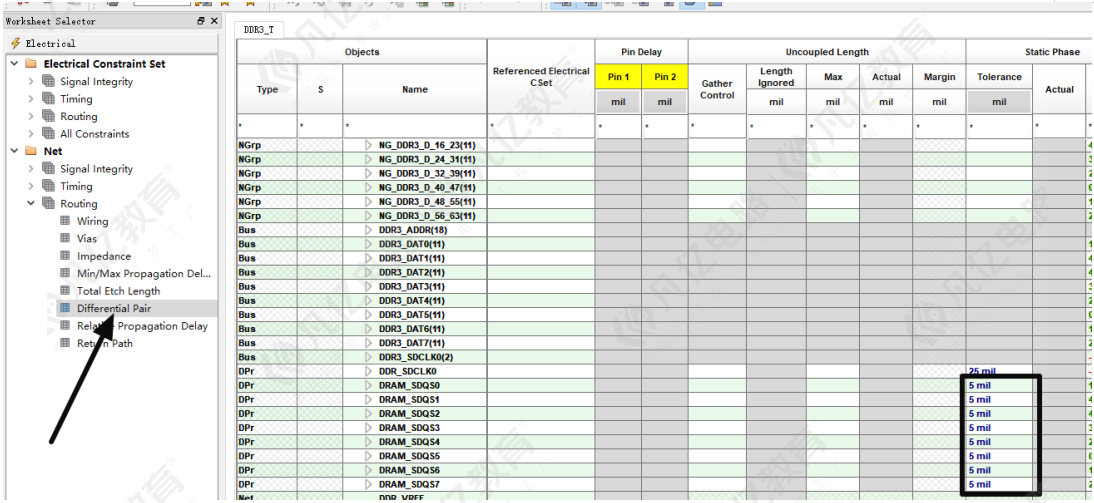

对于差分对来说,用来约束差分对内等长,它有两个设置项:Static Phase(静态等长),Dynamic Phase(动态等长),如图10-34所示。

图10-34 差分等长设置项

因为差分接收端所接收的信号是两根信号的差值,必须保证相位的高度同步,所以它们的对内等长要求一般都是通用的,差分对内等长要求总结如下:

1.差分对内整体控制等长<=5mil;

2.如果有换层,每一层的走线差分对内控制等长<=5mil(考虑不同层传输延时的差别);

3.大于5G的高速串行总线,考虑实时等长,也就是当走线的偏差大于25mil的时候,必须在600mil以内进行补偿,可以反向拐角来补偿,也可以按照3W规则小波浪绕线补偿;

4.Break out区域,偏差可以放大到30mil,不等长的范围可以增加到800mil,如果换层,每层走线之间的不等长偏差也从<=5mil加大到<=10mil。

第1点可以直接通过Static Phase来进行约束,实际上我们平常所处理的差分对内等长设的都是静态规则,只要保证整体等长即可,至于是绕大波浪还是小波浪,在哪儿绕波浪,这些都还是有讲究的。

第2点,这项要求我们无法通过约束来设置相应的规则,但是可以设置一个静态规则的同时在处理等长时候需要有一个动态思维:因为动态等长就是我们所说的实时等长,它与静态等长所不同的是差分对的两个信号无论在哪个位置都是满足5mil的等长误差。我们在处理静态等长的时候就需要有这种思维:两根线的长度是在哪里引起的误差,就需要在哪里补偿回来,保证实时等长。

第3.4点就是真正意义上的动态等长,当信号速率比较高的时候,我们就必须设置Dynamic Phase,通过这项约束来保证两根信号的实时等长。

差分等长规则设置具体步骤如下:

执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器。

在Electrical选项中先将Static Phase的精度设置为5mil,如图10-35所示。

图10-35 静态等长规则设置

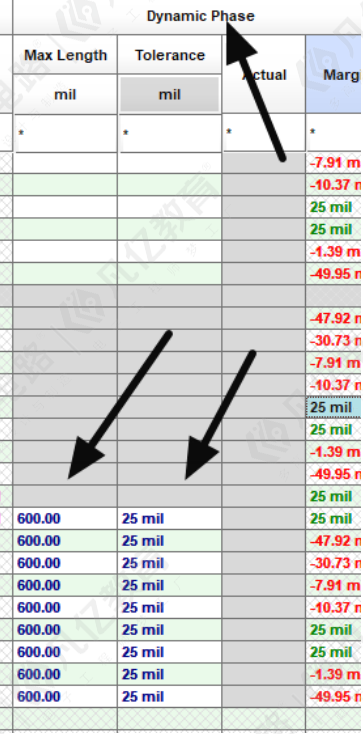

当走线的偏差大于25mil的时候,必须在600mil以内进行补偿,其用Dynamic Phase进行约束,如图10-36所示。

图10-36 动态等长规则设置

10.2.8 点到点源同步信号相对延迟等长规则设置

相对传输延迟,设置一个相对误差,组内线以某一根目标线为基准,正负偏差在设置的误差范围内即可,不用满足最大最小的限制。经常使用于源同步的时序总线,这种规则的好处在于长度是动态的,如果设计过程中基准线的长度发生变坏了,只需要更改其他信号的信号线长度即可。

点到点源同步信号,就是一根网络只有两个端点,中间没有添加负载,对于其设置相对延迟等长规则设置具体步骤如下:

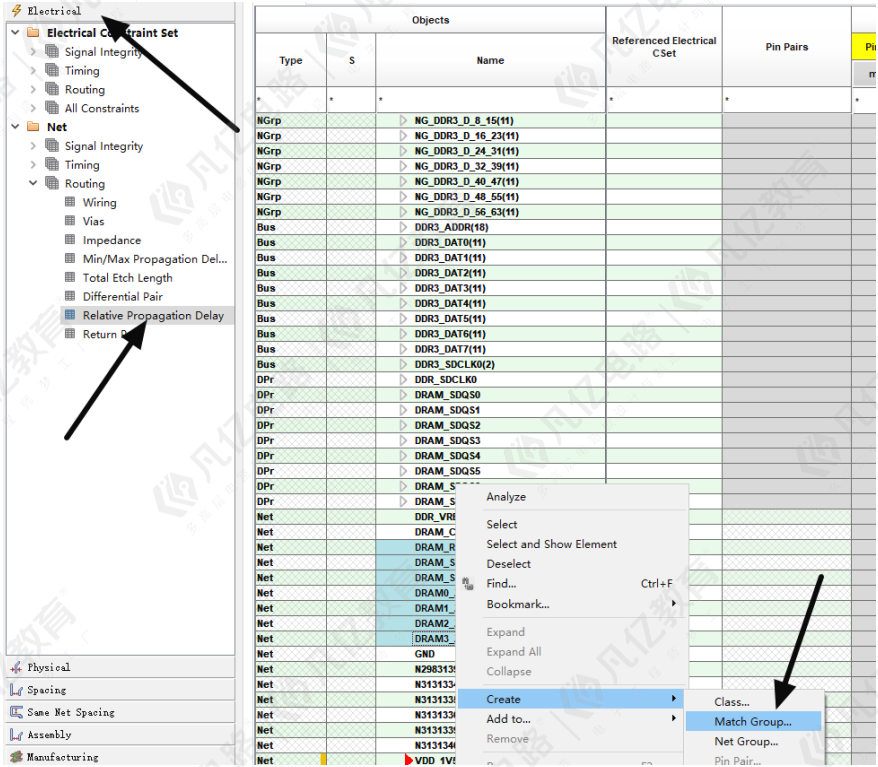

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器。

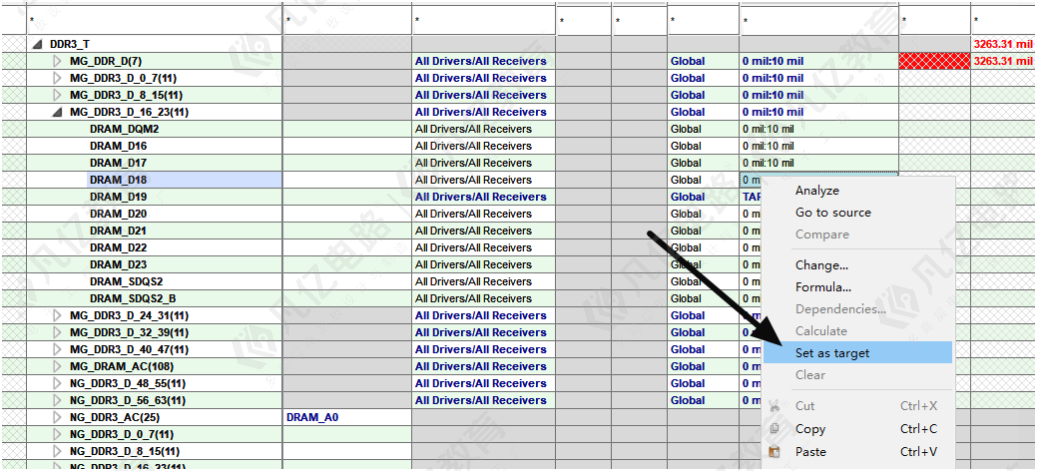

(2)在左侧选择Electrical-Net-Relative Propagation Delay选项中,选择所需要等长的网络单击右键创建一个Match Group等长组,如图10-37所示。

图10-37 Match Group的创建

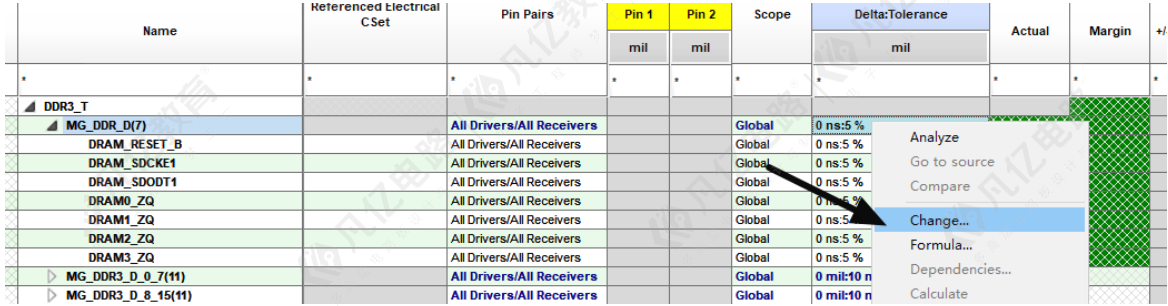

(3)在弹出的界面中,输入需要创建的等长集合的名称,见名知意,如:“MG_DDR_D”,取好名称之后,点击按钮,则等长的集合就创建完毕了,创建好之后,在误差那一栏,选中最上面的根目录,点击鼠标右键,点击Change命令,对所设置的等长集合的误差进行修改即可,如图10-38所示。

图10-38 误差设置示意图

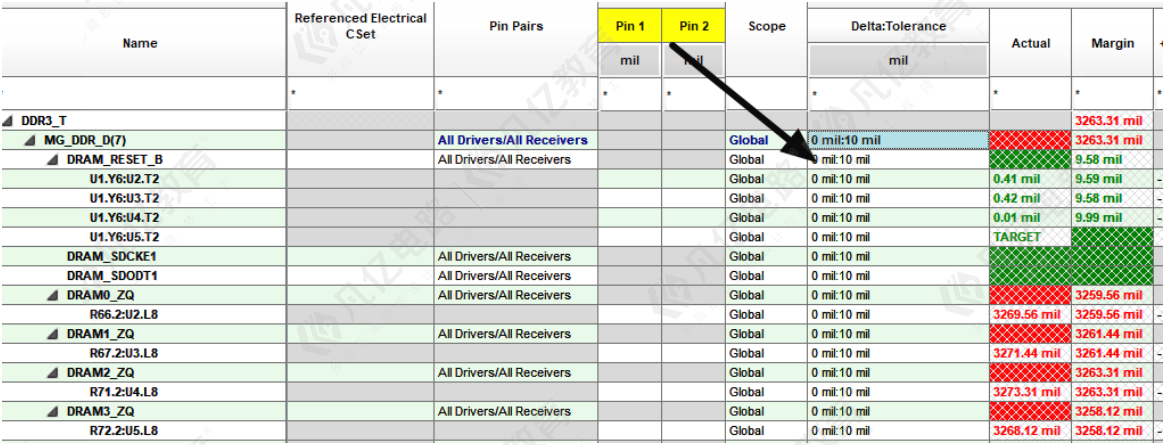

(4)设置好误差之后,比如±10mil,点击OK按钮,则这一组需要做等长的信号线的规则就添加好了,如图10-39所示。

图10-39 等长示意图

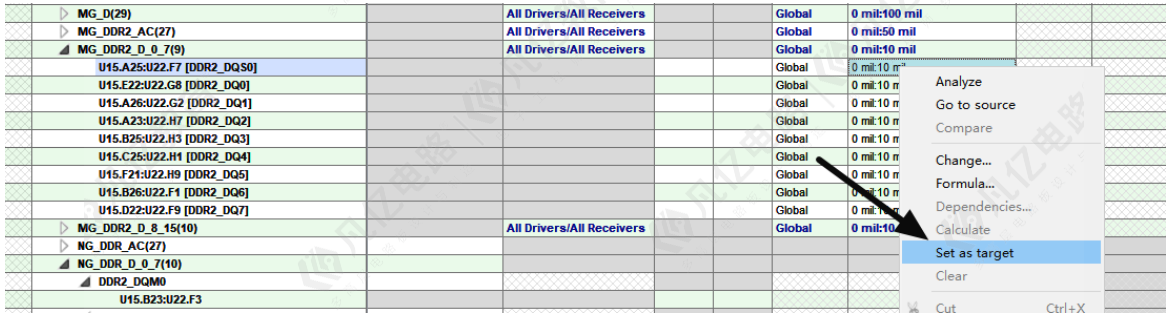

(5)等长添加好以后,选择一根合适的信号线,点击右键,设置为目标线,则所有的信号线就按照这个线为基准,在误差范围进行等长即可,如图10-40所示。

图10-40 设置目标长度示意图

上述操作完成之后,即可在PCB中去根据长度进行蛇形等长操作。

10.2.9 多负载源同步信号相对延迟等长规则设置

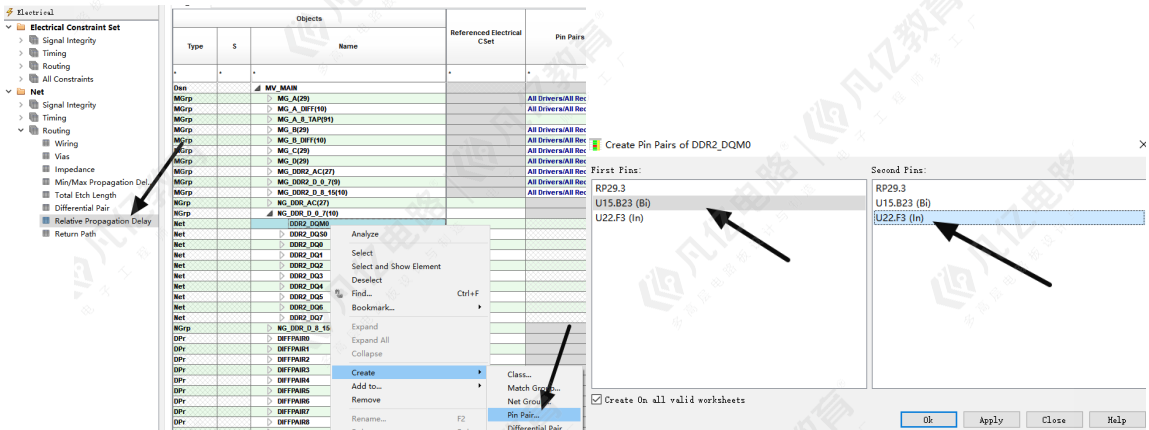

多负载源同步信号是多个器件中都有相同的网络进行连接,即一根网络具有多个端点,这种情况下做相对延迟等长需要利用到Pin Pair功能,具体步骤如下:

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器。

(2)在左侧选择Electrical-Net-Relative Propagation Delay选项中,选择所需要等长的网络单击右键创建一个Pin Pair,可以在弹出的窗口进行首尾端点的选择,如图10-41所示,是DDR2_DQM0信号从器件U15到器件U22进行等长,且对要等长的一组网络依次进行Pin Pair的创建。

图10-41 Pin Pair的创建

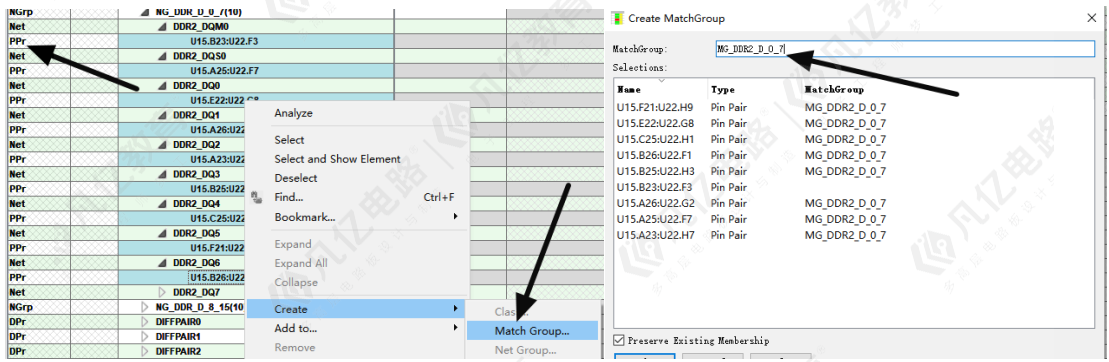

(3)选中该组网络所有创建好的Pin Pair 创建等长组Match Group,且对创建的Match Group进行命名,如图10-42所示。

图10-42 Match Group的创建

(4)设置好误差之后,比如±10mil,点击OK按钮,则这一组需要做等长的信号线的规则就添加好了,如图10-43所示。

图10-43 等长误差设置示意图

(5)等长添加好以后,选择一根合适的信号线,点击右键,设置为目标线,则所有的信号线就按照这个线为基准,在误差范围进行等长即可,如图10-43所示。

图10-44 设置目标长度示意图

上述操作完成之后,即可在PCB中去根据长度进行蛇形等长操作。

10.2.10 绝对延迟等长规则设置

绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

(1)执行菜单命令Setup-Constraints-Constraint Manager进入规则管理器。

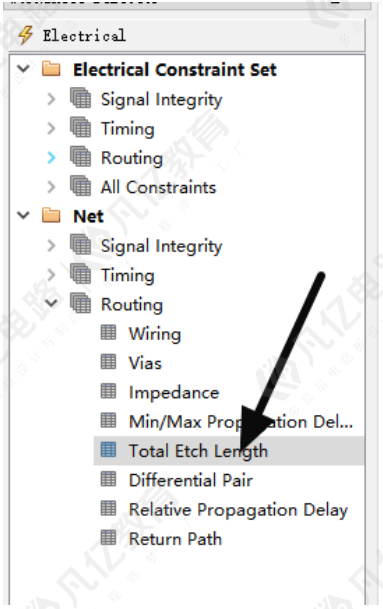

(2)进入规则管理器以后,在CM左侧的目录栏中选择Net,在Routing中选择Total Etch Length,如图10-45所示,设置信号的线的总长度。

图10-45 设置绝对长度示意图

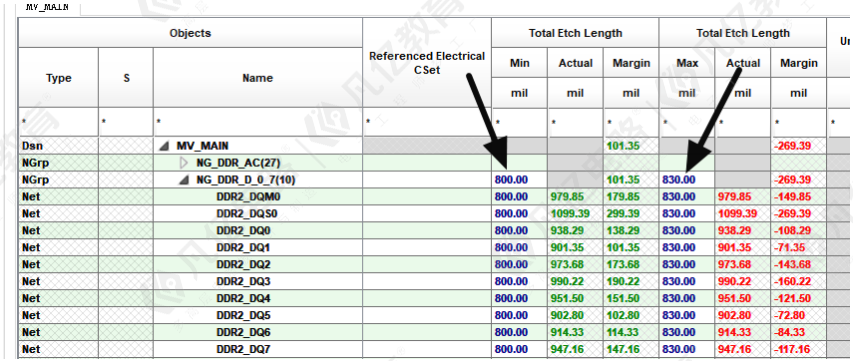

(3)进入到右边栏,对需要做等长的信号线,创建好Net Group,在Total Etch Length中输入最小值、最大值即可,如图10-46所示,每一组的信号线都会跟这个对比产生相对应的误差,按这个误差做等长即可。

图10-46设置绝对长度最大值最小值示意图

上述操作完成之后,即可在PCB中去根据长度进行蛇形等长操作。

10.2.11 元器件管脚长度导入

我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

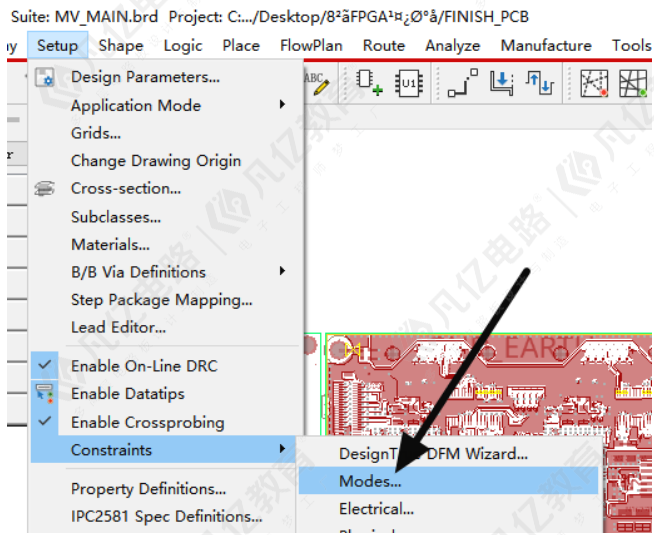

(1)需要将约束封装引脚长度信息的约束开关打开,执行菜单命令Setup-Constraints-Modes,如图10-47所示。

图10-47约束开关设置示意图

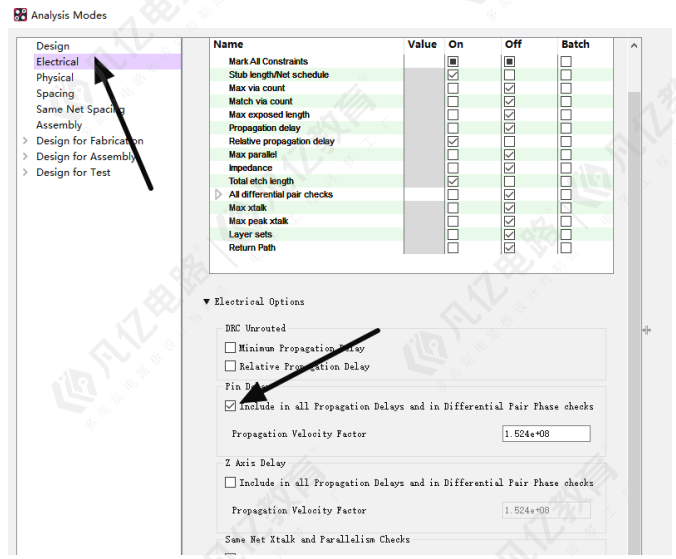

(2)进入约束开关管理器界面之后,在左侧边栏选择Electrical Options选项,在右侧勾选上Pin Delay的选项,如图10-48所示,这样在等长约束规则中Pin Delay数据行才会被激活,才会应用到等长列表当中。

图10-48打开Pin Delay示意图

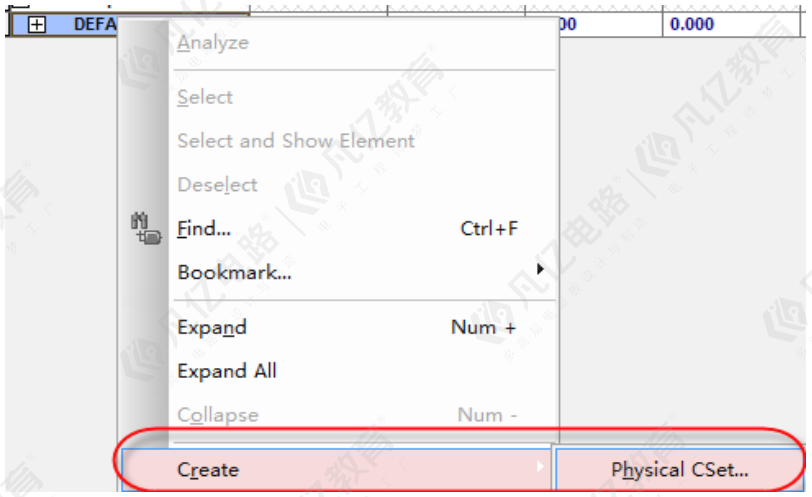

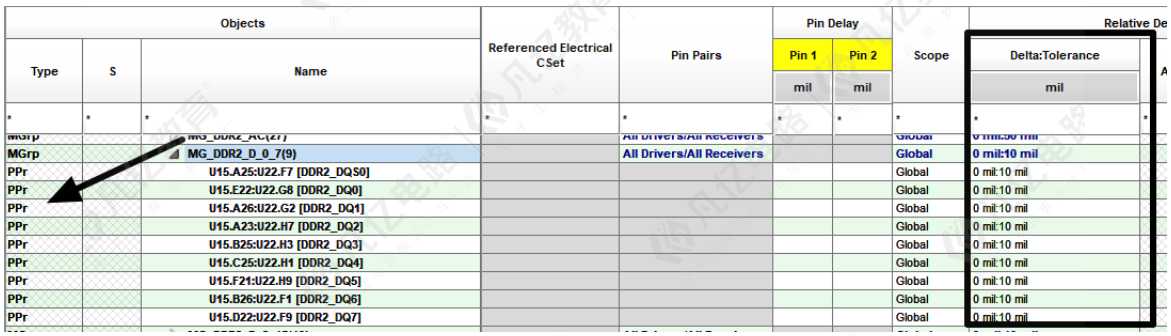

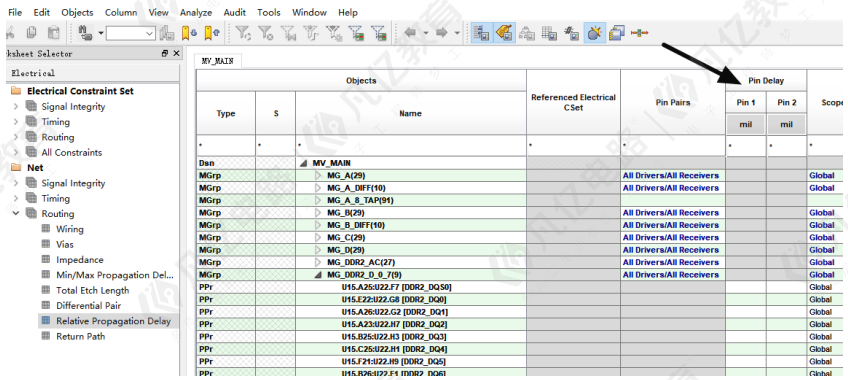

(3)设置完上述的参数之后,回到规则管理器面板中,在加好的等长规则中,会发现Pin Delay才是可以编辑的状态,在Pin Delay界面,如图10-49所示,有Pin1和Pin2两个输入栏,代表的是该信号连接的两个IC,如果两个IC都有引脚长度的话,分别输入即可,这个数据是可以手动进行输入的,但是这样的工作量比较大,也非常容易出错,我们可以通过导入Excel表格的方式进行导入。

图10-49 Pin Delay输入栏示意图

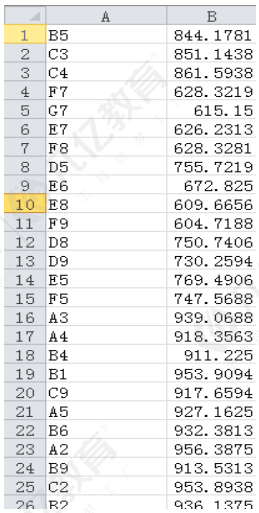

(4)根据芯片厂家提供的参数,将Pin Delay的数据输入到Excel表格中,格式如图10-50所示,一行是芯片的管脚列表,一行是芯片引脚长度信息,然后保存,存为后缀为CSV的文件,Allegro软件才能识别。

图10-50 Pin Delay格式示意图

图10-51导入 Pin Delay示意图

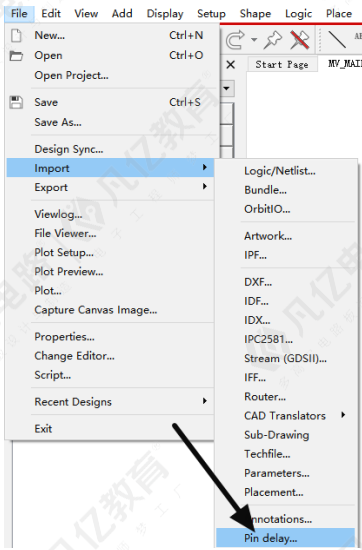

(5)设置好Pin Delay的格式以后呢,点击执行菜单命令File-Import,导入选项中选择Pin Delay,如图10-51所示。

(6)进入导入界面,选择刚刚处理好的csv文件,然后用鼠标去选择需要导入芯片封装引脚长度的元器件,进行导入即可。

(7)导入成功后,在Pin Delay栏就可以相对应的数据,分别对应的是哪个芯片,这样可以大大提高效率,并且不会出错。

10.2.12 规则的导入与导出

我们使用Allegro软件进行PCB设计,其中的PCB布局布线都可以进行复用,那么它所设置的规则,比如物理规则、间距规则,是否也可以进行复用呢,当然是可以的,具体复用操作的步骤如下所示。

(1)打开已经设置好规则的PCB文件,执行菜单命令Setup-Constraints-Constraint Manager,进入到规则管理器中。

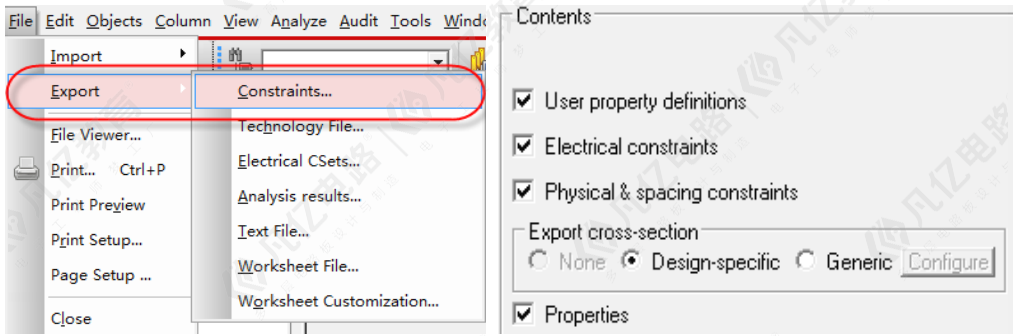

(2)点击菜单命令File-Export,在下拉菜单中选择Constraints,导出规则,如图10-52所示,在弹出的保存界面的左下角,可以进行需要导出的规则以及属性的选择,根据设计需要进行选择即可。

图10-52 导出PCB设计规则示意图

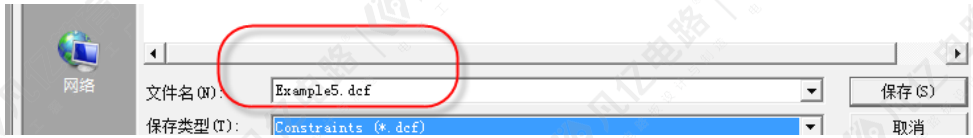

(3)将导出的文件进行保存,如图10-52所示,保存的文件类型是dcf的文件。

图10-53 保存导出的设计规则文件示意图

(4)打开需要复用规则的PCB文件,执行菜单命令Setup-Constraints-Constraint Manager,进入到规则管理器中。

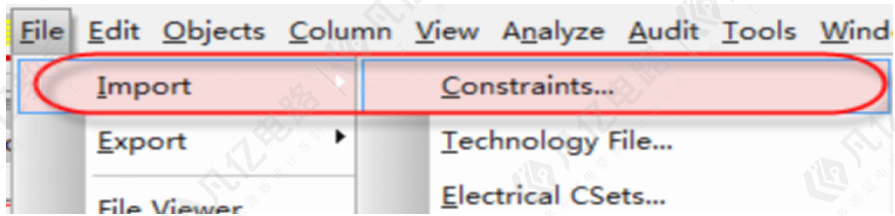

(5)点击菜单命令File-Import,在下拉菜单中选择Constraints,导出规则,如图10-53所示。

图10-54 导入设计规则示意图

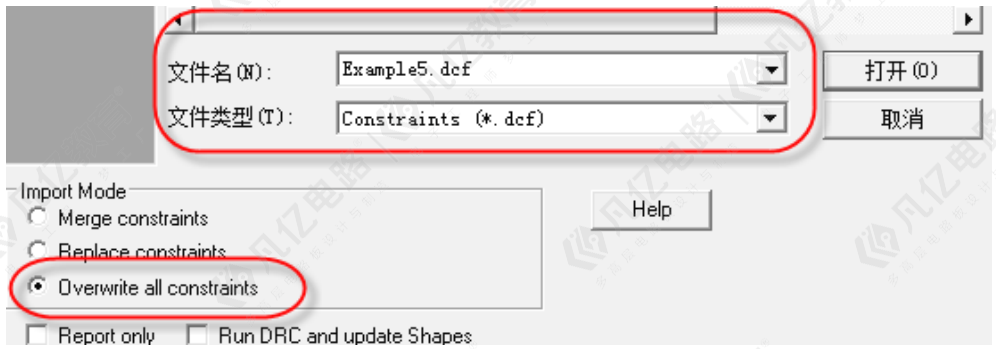

(6)在弹出的界面中,选择刚导出的dcf规则文件,在左小角可以对导入的模型规则进行选择,一般选择Overwrite all Constraints,导入所有的规则,如图10-55所示,点击打开,对规则进行导入即可。

图10-55 导入设计规则设置示意图

扫码关注

扫码关注