对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB叠层进行添加,以满足设计的要求。

8.6.1 正片层与负片层

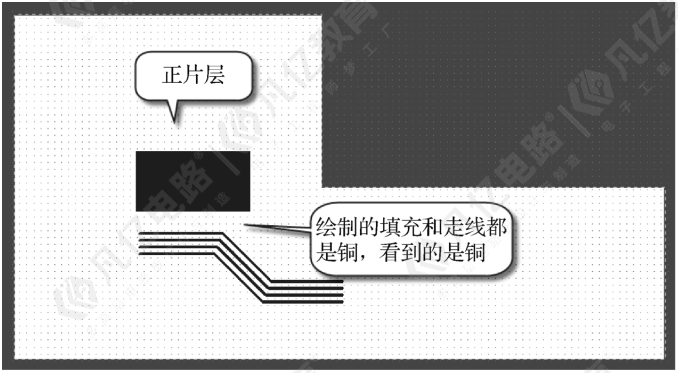

正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”、“铜皮”等进行大块敷铜与填充操作,如图8-29所示。

图8-29 正片层

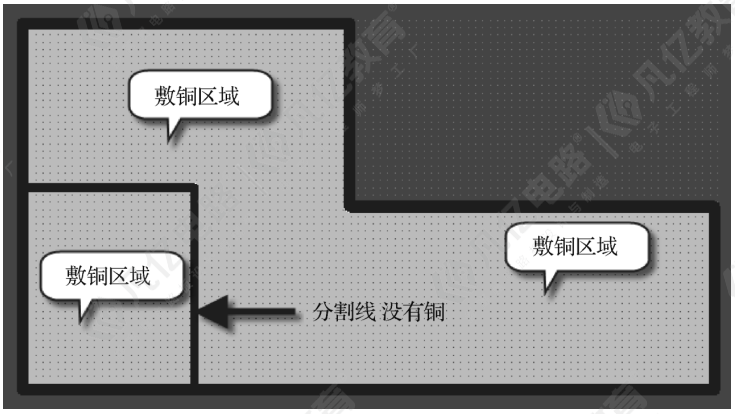

负片层则正好相反,即默认敷铜,就是生成一个负片层之后整一层就已经被敷铜了,走线的地方是分割线,没有铜存在。要做的事情就是分割敷铜,再设置分割后的敷铜的网络即可,如图8-30所示。

图8-30 负片层

8.6.2 内电层的分割实现

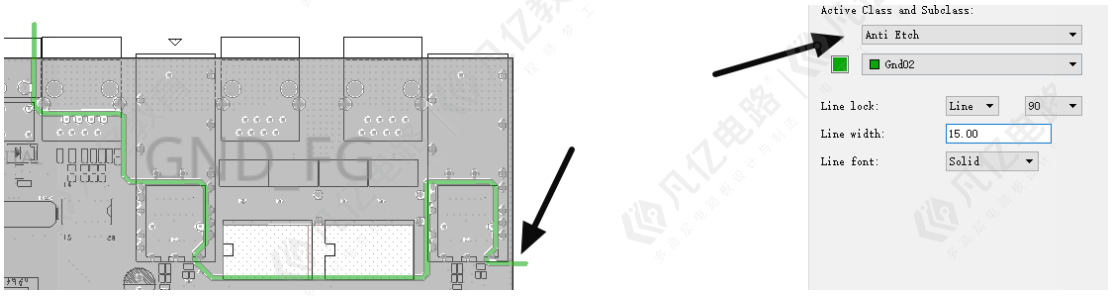

(1)在ALLEGRO中,用线条在Anti Ecth层来进行分割。分割线不宜太细,可以选择15mil及以上,如图8-31所示。

图8-31 铜皮分割示意图

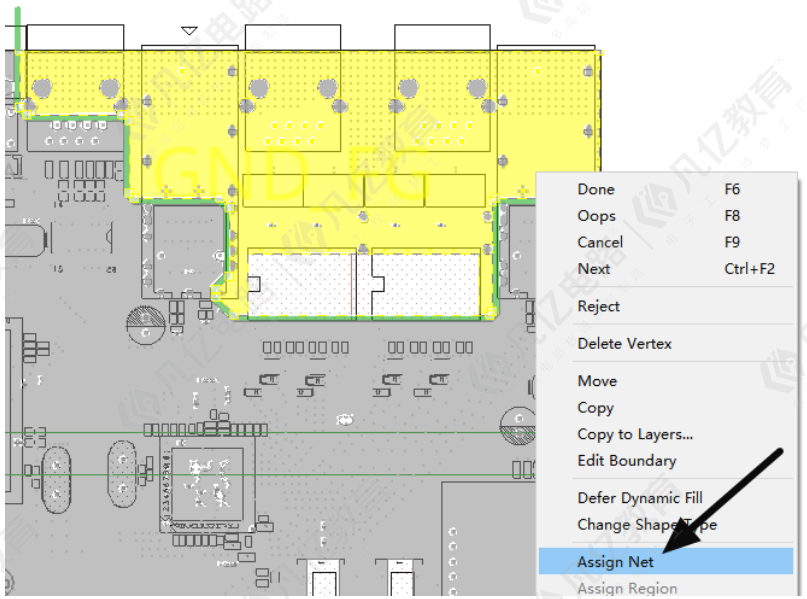

(2)铜皮分割完成之后可以通过选中铜皮右键进行网络的分配,如图8-32所示。

图8-32 铜皮分配网络示意图

正、负片都可以用于内电层,正片通过走线和敷铜也可以实现。负片的好处在于默认大块敷铜填充,再进行添加过孔、改变敷铜大小等操作都不需要重新“Rebuild”,这样省去了重新敷铜计算的时间。中间层用电源层和GND层(也称地层、地线层、接地层)时,层面上大多是大块敷铜,这样用负片的优势就很明显。

8.6.3 PCB叠层的认识

随着高速电路的不断涌现,PCB的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在设计多层PCB之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层、6层,还是更多层数的电路板。这就是设计多层板的一个简单概念。

确定层数之后,再确定内电层的放置位置及如何在这些层上分布不同的信号。这就是多层PCB叠层结构的选择问题。叠层结构是影响PCB的EMC性能的一个重要因素,一个好的叠层设计方案将会大大减小电磁干扰(EMI)及串扰的影响。

板的层数不是越多越好,也不是越少越好,确定多层PCB的叠层结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对生产厂家来说,叠层结构对称与否是PCB制造时需要关注的焦点。所以,层数的选择需要考虑各方面的需求,以达到最佳的平衡。

对有经验的设计人员来说,在完成元件的预布局后,会对PCB的布线瓶颈处进行重点分析,再综合有特殊布线要求的信号线(如差分线、敏感信号线等)的数量和种类来确定信号层的层数,然后根据电源的种类、隔离和抗干扰的要求来确定内电层的层数。这样,整个电路板的层数就基本确定了。

1.常见的PCB叠层

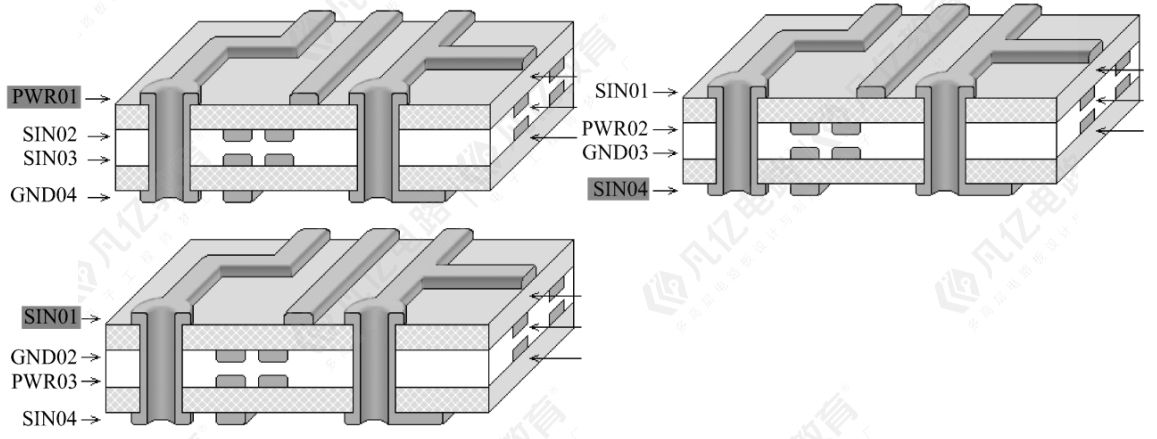

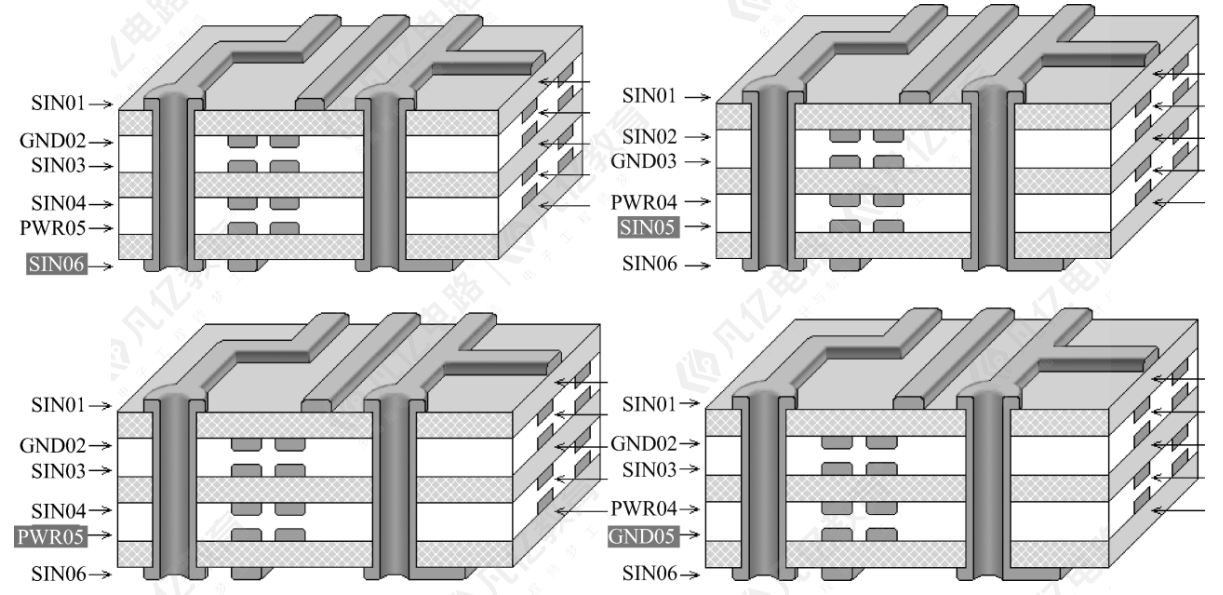

确定了电路板的层数后,接下来的工作便是合理地排列各层电路的放置顺序。图8-33和图8-34 分别列出了常见的4层板和6层板的叠层结构。

图8-33 常见的4层板的叠层结构

图8-34 常见的6层板的叠层结构

2.叠层分析

怎么叠层?哪样叠层更好?一般遵循以下几点基本原则。

① 元件面、焊接面为完整的地平面(屏蔽)。

② 尽可能无相邻平行布线层。

③ 所有信号层尽可能与地平面相邻。

④ 关键信号与地层相邻,不跨分割区。

可以根据以上原则,对如图8-30和图8-31所示的常见的叠层方案进行分析,分析情况如下。

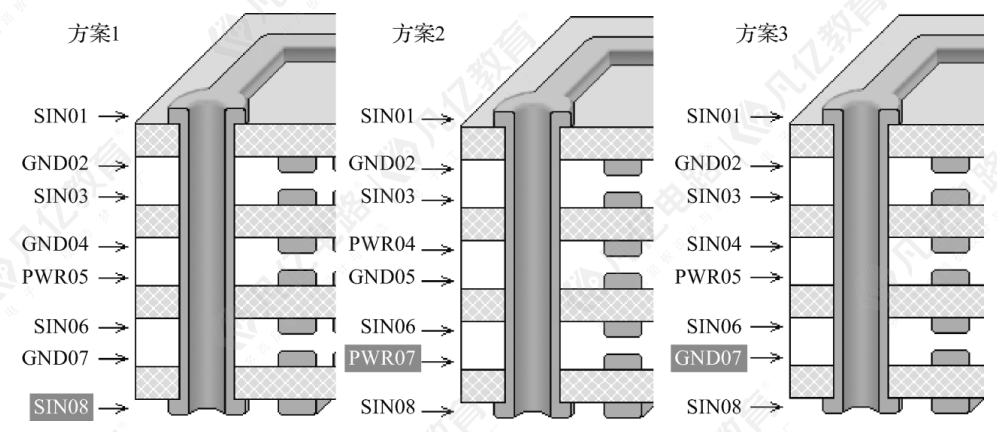

(1)3种常见的4层板的叠层方案优缺点对比如表8-1所示。

表8-1 常见的4层板的叠层方案分析

通过方案1到方案3的对比发现,对于4层板的叠层,通常选择方案2或者方案3,请结合板子的实际情况和叠层原则来正确选择。

(2)4种常见的6层板的叠层方案优缺点对比如表8-2所示。

表8-2 常见的6层板的叠层方案分析

通过方案1到方案4的对比发现,在优先考虑信号的情况下,选择方案3和方案4会明显优于前面两种方案。但是在实际设计中,产品都是比较在乎成本的,然后又因为布线密度大,通常会选择方案1来做叠层结构,所以在布线的时候一定要注意相邻两个信号层的信号交叉布线,尽量让串扰降到最低。

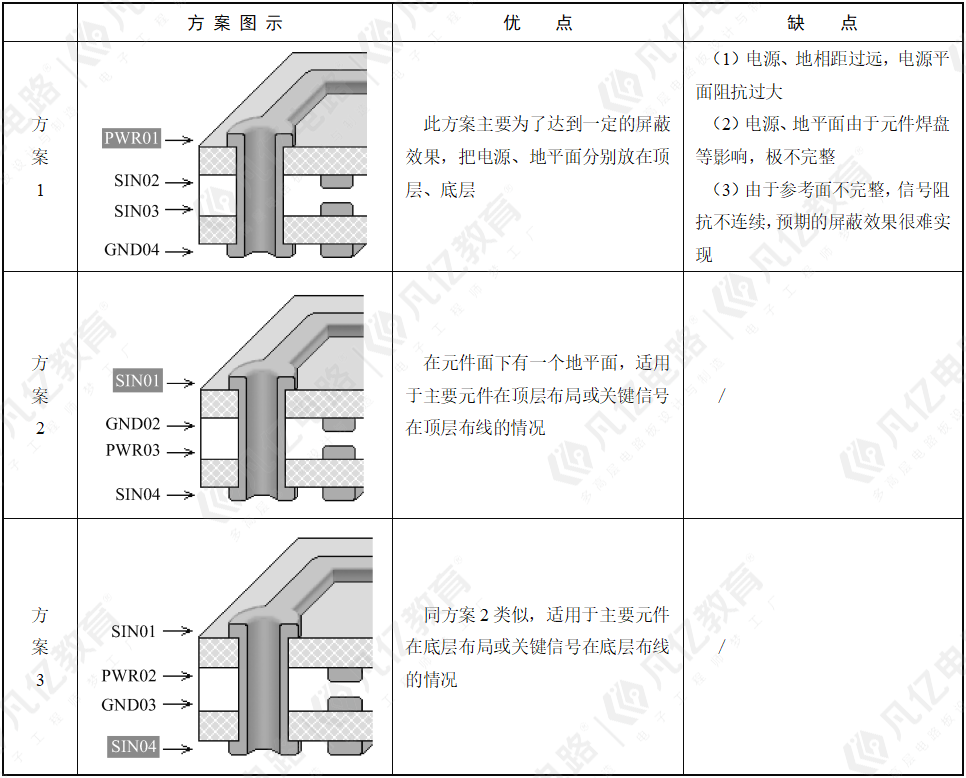

(3)常见的8层板的叠层推荐方案如图8-35所示,优选方案1和方案2,可用方案3。

图8-35 常见的8层板的叠层推荐方案

8.6.4 层的添加及编辑

确认叠层方案之后,如何在ALLEGRO当中进行层的添加操作呢?下面简单举例说明如下。

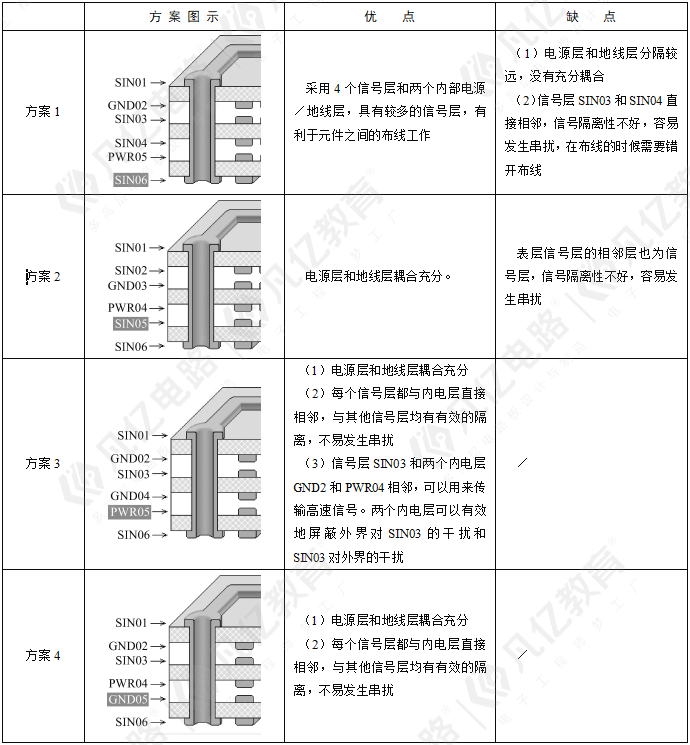

(1)执行菜单命令Setup-Cross section,进入如图8-36所示的叠层管理器,进行相关参数设置。

图8-36 叠层管理器

图8-36 叠层管理器

(2)右击“Add Layer”按钮,可以进行添加层操作。

(3)双击相应的Name,可以更改名称,一般可以改为TOP、GND02、SIN03、SIN04、PWR05、BOTTOM这样,即采用“字母+层序号”,这样方便读取识别。

(4)根据叠层结构设置板层厚度。

扫码关注

扫码关注