8.2.1 网表

网表,顾名思义,就是网络连接和联系的表示,其内容主要是电路图中各个元件类型、封装信息、连接流水序号等数据信息。在使用ALLEGRO进行PCB设计时,可以通过导入网络连接关系进行PCB的导入,在ALLEGRO软件中使用到的有第一方网表及第三方网表。

Allegro的第一方网表与第三方网表有以下几个区别点;

Ø 与Allegro实现交互式操作的是第一方网表,第三方网表时不可以实现交互式操作;

Ø 第三方网表不能将器件的Value属性导入到PCB中,输出时以封装属性来代替Value属性,第一方网表是可以的;

Ø 网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生Device文件,才可以将网表导入到PCB中,第一方网表则可以直接导入。

8.2.2 第一方网表的生成

orcad产生Cadence Allegro的网表的操作步骤如下;

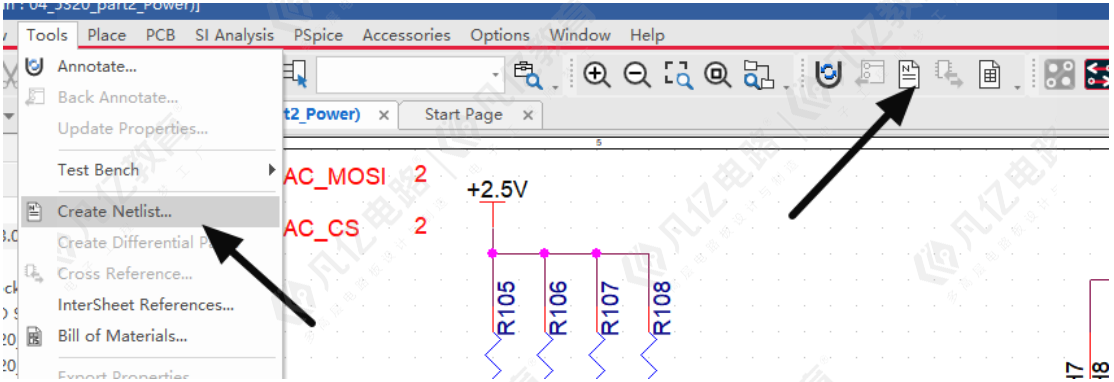

(1)选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的![]() 图标,调出产生网表的界面,如图8-5所示;

图标,调出产生网表的界面,如图8-5所示;

图8-5 产生网表示意图

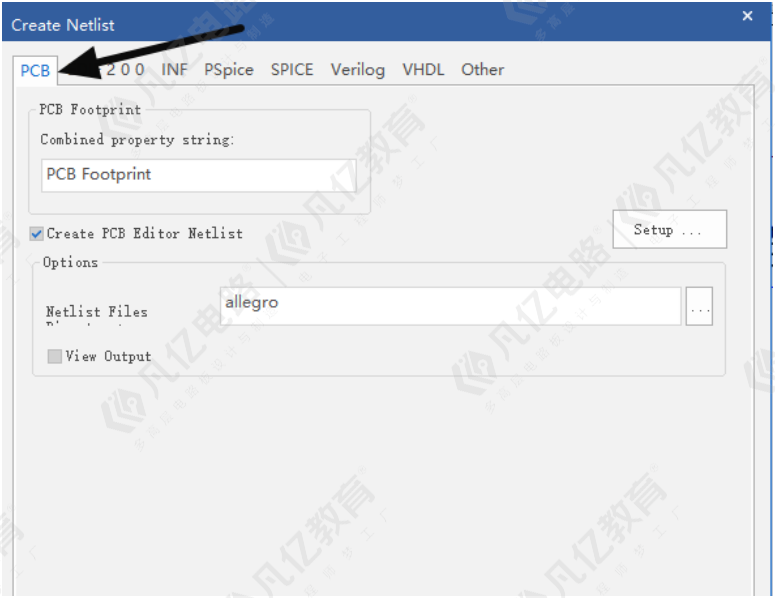

(2)弹出的Creat Netlist界面中,选择的是PCB,产生Allegro的第一方网表,如图8-6所示;

图8-6 Allegro第一方网表参数设置示意图

(3)输入Allegro第一方网表需要注意下面几个地方:

① 需要勾选Creat PCB Editor Netlist,才会生成网表;

② 下面的Netlist Files是输出网表的存储路径,不进行更改的话,是在当前原理图目录下,会自动产生allegro的文件夹,里面就是输出的网表;

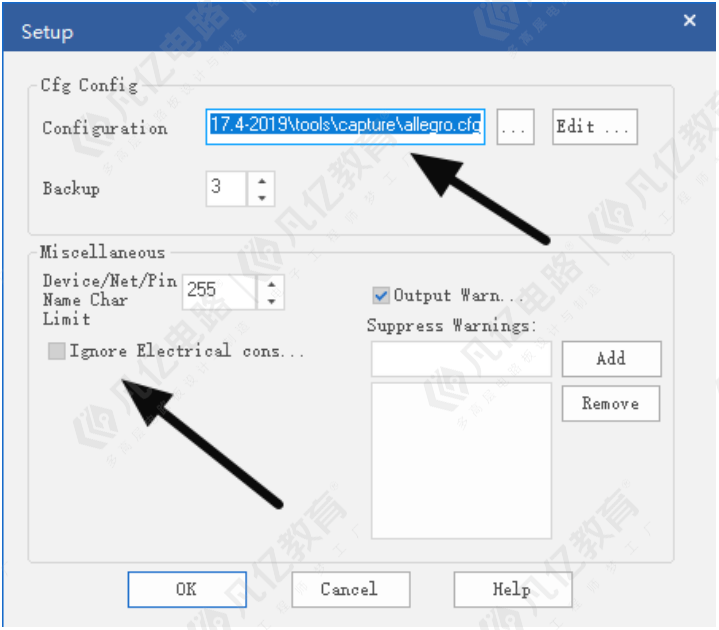

③ 点击右侧的Setup设置按钮,如图8-7所示,勾选Ignore Electrical constraints选项,则忽略掉原理图中所添加的规则。

图8-7 输出网表设置示意图

8.2.3 第三方网表的生成

orcad产生Cadence Allegro第三方网表的操作步骤如下;

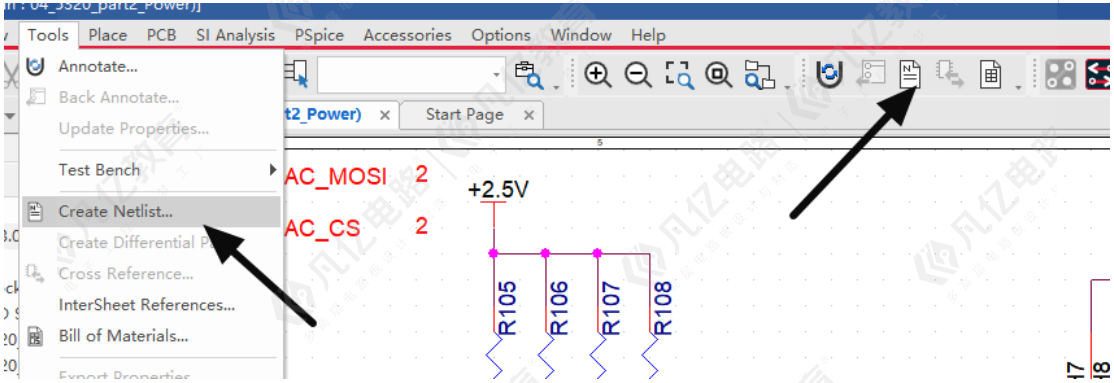

(1)选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的![]() 图标,调出产生网表的界面,如图8-8所示;

图标,调出产生网表的界面,如图8-8所示;

图8-8 输出网表示意图

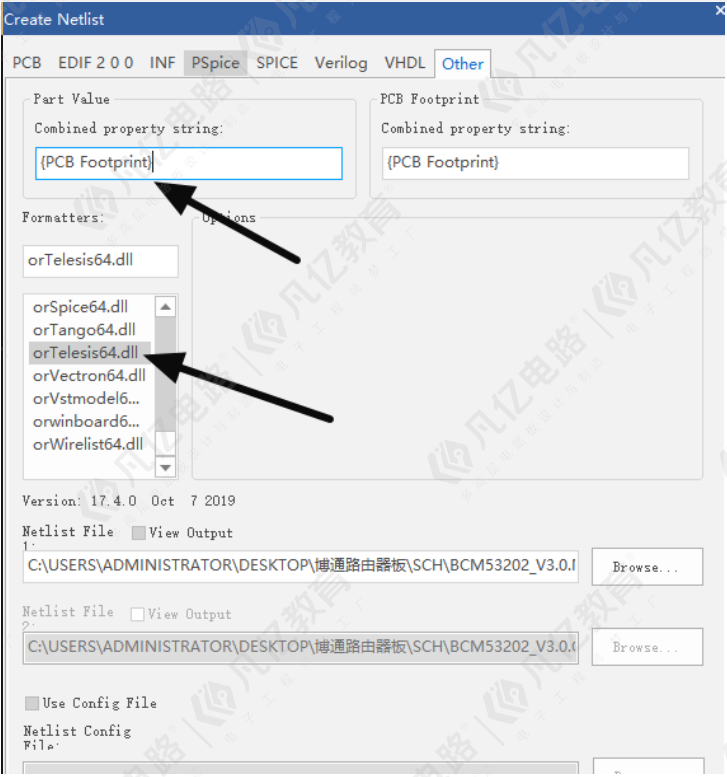

(2)弹出的输出网表界面中选择Other选项,来输出第三方网表,如图8-9所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

图8-9 输出第三方网表设置示意图

(3)按第二步所说的设置好参数以后,在下方的路径中可以选择网表存储的路径,如图3-75所示,默认路径是当前原理图所处的路径。点击确定按钮,即可输出第三方的网表文件,后缀是.NET的文件就是网表文件。

扫码关注

扫码关注