- 首页

- 技术学院

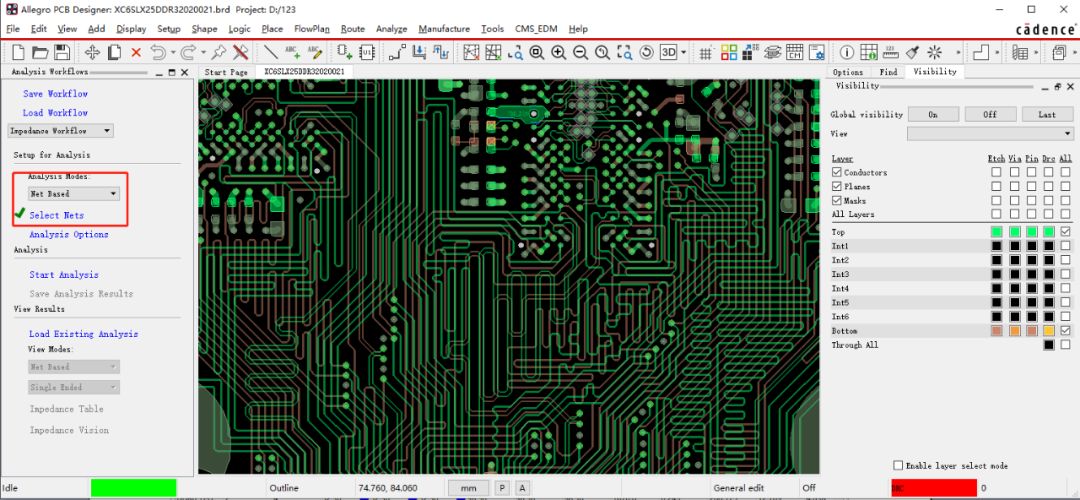

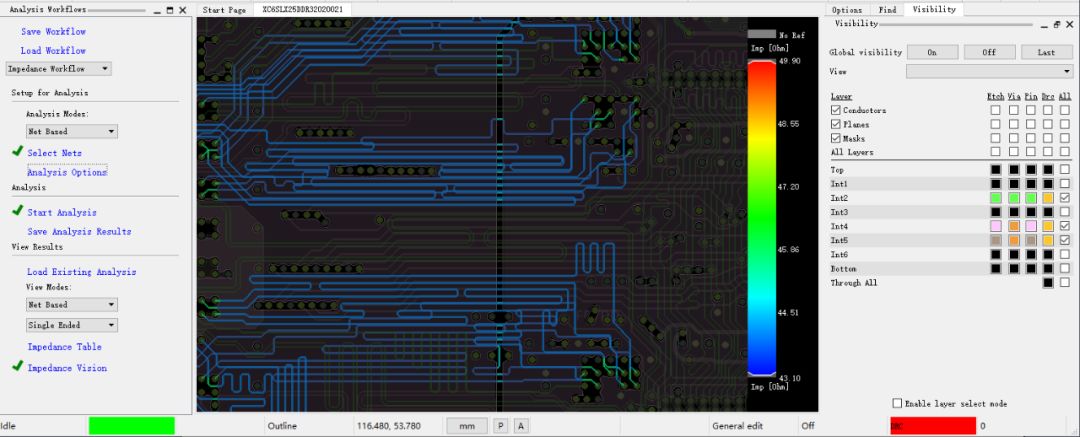

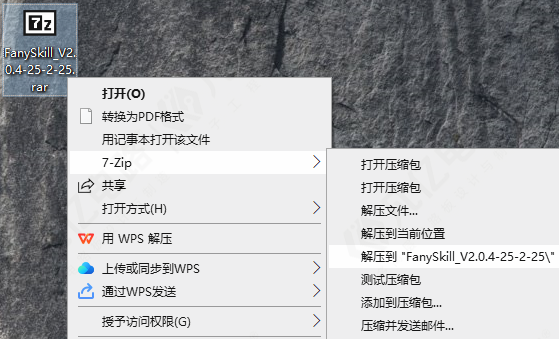

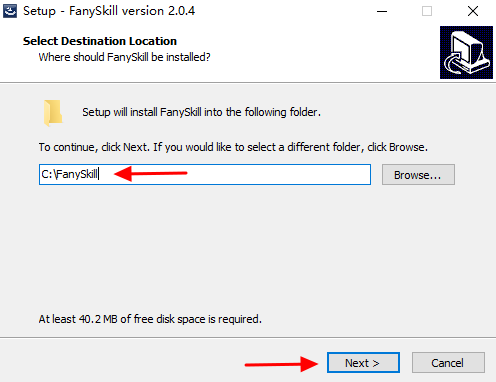

- 直播 Allegro 6层实战直播 RK3576主板全流程解析时间:2025年04月11日 20:00立即报名手机20W PD快充Layout全流程解析时间:2025年03月21日 20:00立即报名400W开关电源PCB LAYOUT原理图解析与设计要点时间:2025年03月15日 20:00立即报名恒流源电路之三极管恒流源原理时间:2025年02月28日 20:00立即报名凡亿Allegro新版本Skill功能与应用线上直播发布会时间:2025年02月14日 20:00立即报名从原理到实战--典型充电器故障与修复全解析时间:2025年01月10日 20:00立即报名

- 培训中心

- 认证考试

- 在线工具

- 资源中心

- 关于我们

版权所有© 2022 湖南凡亿智邦电子科技有限公司湘ICP备18024493号-1

扫码关注

扫码关注