- 全部

- 默认排序

51单片机因其结构简单,没有时序、中断等复杂配置,价格低廉,是小白初入单片机领域的首选单片机,但部分小白经常听到MCS-51和8051单片机,就很好奇它们是否同一个单片机,有什么关系,今天将为小伙伴们解答问题。一般来说,MCS是指Intel

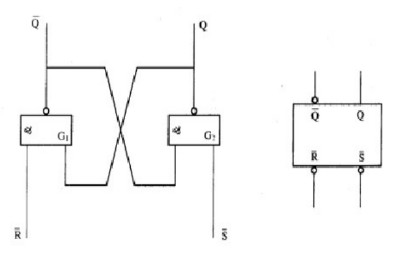

对于数字电路,人们更为熟悉的是逻辑运算门电路,但对于时序电路却鲜为人知,它们的区别在于:前者在某一时刻的输出状态只取决于当时的输入状态;而后者的输出状态不仅与当时的输入有关,还取决于电路原来的状态,其中之一是RS触发器。1、基本RS触发器如

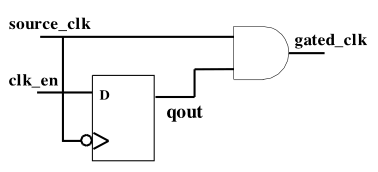

一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。1、全局时钟全局时钟即同步时钟,它是通过FPGA

小白在设计数字电路,如同步/异步时序电路时常常会碰到毛刺或者亚稳态的问题,但很多小白对亚稳态问题措手不及,经常搞错电路导致系统崩溃,所以本文将归纳总结,分析数字电路中的亚稳态。在同步电路或异步电路中,如果触发器的setup时间或hold时间

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

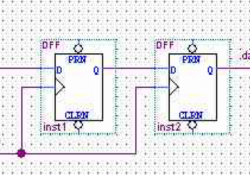

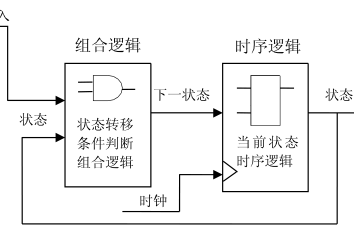

在FPGA设计里,状态机的设计是最为重要的环节之一。很多FPGA系统里的运行成功基本上和状态机设计相关,毫不夸张地说,FPGA系统的成功,其中一半归于状态机。所以我们该如何做好状态机?一般来说,工程师在状态机的设计中基本采用两段式写法(2个

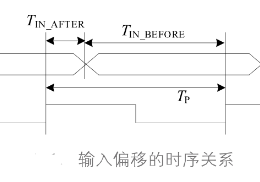

FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信

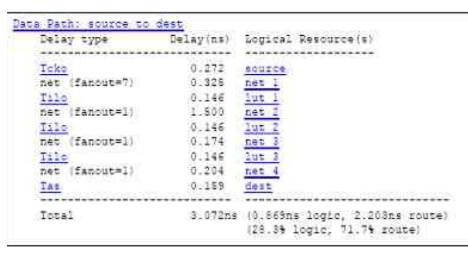

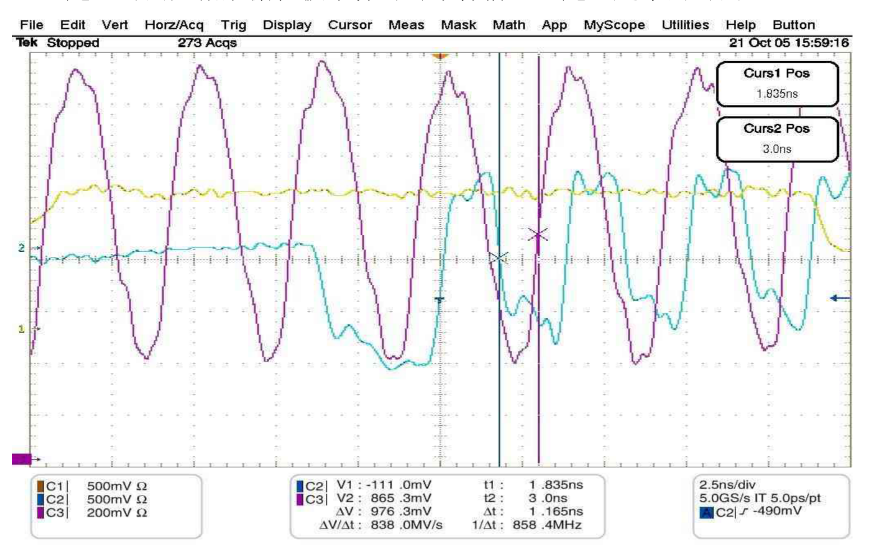

时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多1、布局太差如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.02

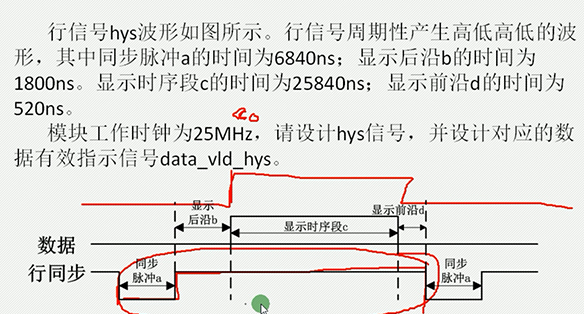

信号时序测试方法是硬件测试中的SI方法之一,也是测试工程师需要重点了解并运用的测试方法之一,但有很多小白不清楚信号时序测试方法,加上看不懂示波器等信号变化,所以本文将详谈信号时序测试方法,希望对小伙伴们有所帮助。一般来说,衡量时序的参数主要

FPGA和CPLD都属于可编程逻辑器件,有着很多共同特点,但由于FPGA和CPLD的结构差异,所以它们的区别也很大,所以本文将详谈FPGA和CPLD的区别及联系。1、CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。换句话说

扫码关注

扫码关注