- 全部

- 默认排序

本课程介绍了FPGA SDRAM文档的阅读和理解、SDRAM的功能汇总、SDRAM的实现架构、SDRAM接口的模块划分、SDRAM的时序分析和约束。

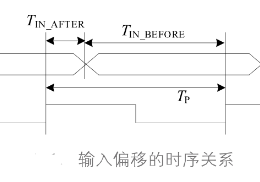

FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信

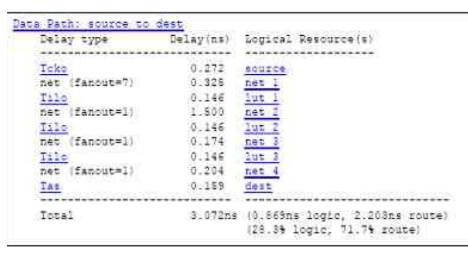

时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多1、布局太差如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.02

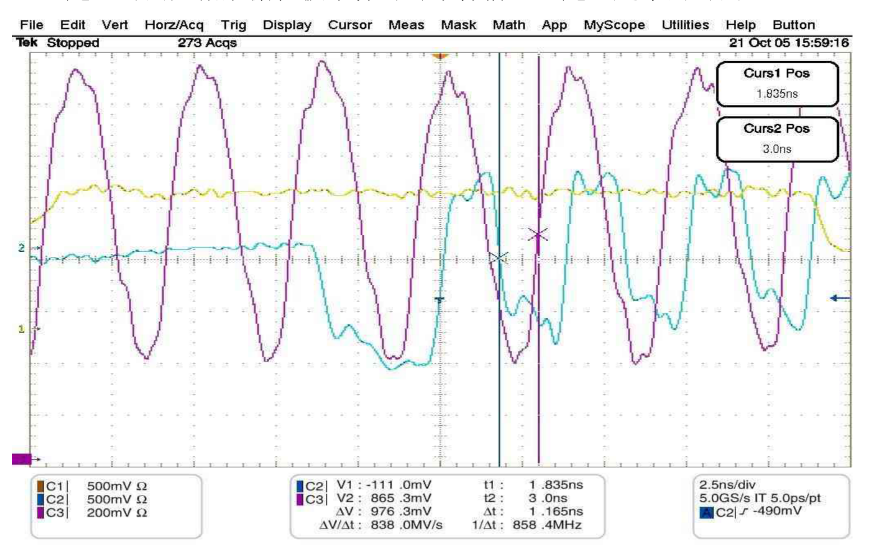

信号时序测试方法是硬件测试中的SI方法之一,也是测试工程师需要重点了解并运用的测试方法之一,但有很多小白不清楚信号时序测试方法,加上看不懂示波器等信号变化,所以本文将详谈信号时序测试方法,希望对小伙伴们有所帮助。一般来说,衡量时序的参数主要

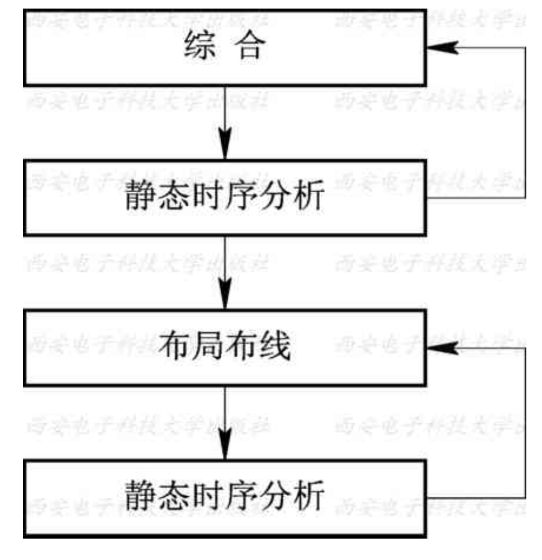

要想成为一个优秀的电子工程师,熟练掌握IC设计是基本技能之一,IC设计可分为多个环节,其中之一是静态时序分析,要想做好IC设计的静态时序分析,该如何做?首先,静态时序分析是检查IC系统时序是否满足要求的主要方法,静态时序分析工具根据往表中各

FPGA是一种功能强大的可编程逻辑器件,广泛应用在数字电路设计、信号处理、无线通信等多领域,自然也就成为电子工程师的关键技能之一,若是不合理使用FPGA,极有可能导致FPGA设计不稳定、延迟大、时序崩溃等问题,所以下面将聊聊FPGA设计中的

现阶段许多公司仍然是让硬件工程师来进行PCB设计和方案开发,除开这些,硬件工程师还要做更多的专业工作,这样势必会使产品上市的时间大大延长。而且现在随着高速数字电子技术的发展,对高速PCB设计的要求也越高:信号完整性仿真分析、时序分析,单板和

现阶段许多公司仍然是让硬件工程师来进行PCB设计和方案开发,除开这些,硬件工程师还要做更多的专业工作,这样势必会使产品上市的时间大大延长。而且现在随着高速数字电子技术的发展,对高速PCB设计的要求也越高:信号完整性仿真分析、 时序分析, 单

时序分析的基本概念(1)

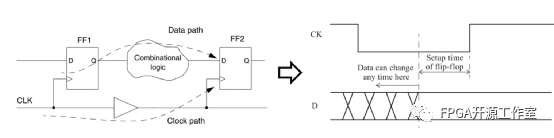

1 setup timeSetup time (建立时间)是数据信号(D)在时钟事件(这里以时钟上升沿为例)发生之前保持稳定的最小时间。以便时钟可靠地对数据进行采样。适用于同步电路,如触发器(flip-flop)。 2 hold timeHold time (保

FPGA设计准则

直播时间:11月11日 晚8点直播结束后扫码添加助教领取直播福利直播介绍:近年来,随着国产全面化目标的推进,国产FPGA迎来了春天,Mill团队作为国内知名的FPGA研究团队,多次深度参与各大高校的FPGA课程改革和重大项目开发,本次直播,Mill团队将和大家一起聊聊FPGA设计准则及未来前景....直播大纲:(1)FPGA开发硬件思想(2)FPGA开发标准化设计流程(3)时序分析及时序分析准则直播福利:1、观看直播赠送【3套紫光CPLD板卡及配套指导手册】2、报名直播,可永久观看回放讲师介绍:缪老师(Mill),现为紫光同创FPGA原厂核心生态战略伙伴,拥有超过10年FPGA开发经验,在技术层面,曾重点参与和主导多个大型项目开发,熟悉各类高速协议应用开发:TCP/IP ,Serdes,光纤通信等。熟悉各类数字信号处理及定点技巧,独立完成纯逻辑LDPC编解码,DVB-T2等无线标准核心模块开发。凡亿教育课堂介绍:凡亿教育直播凡亿课堂是凡亿旗下开放式电子问答平台,包含免费小课、免费问答、社区、直播等版块,横跨知识分享和在线孝育两大领域。内容方面覆盖了嵌入式、单片机、电源设计、模拟技术、PCB、仿真、软件开发、Lab应用、IC设计等细分领域品类,汇聚了上百名网师,利用平台的在线教学课堂,为电子行业学生无界交流。

扫码关注

扫码关注