时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多

1、布局太差

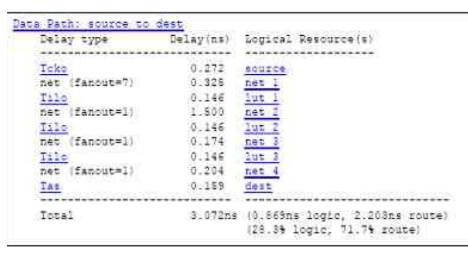

如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.027ns,逻辑时间只有0.869ns,而布线延迟经达到2.203ns,失败原因就是布局太差。

相应的解决方案:

①在ISE布局工具中调整布局的努力程度(effort level);

②利用布局布线工具的特别努力程度(extra effort)或MPPR选项;

③如果用户熟悉区域约束,则利用Floorplanner相对区域约束(RLOC),重新对设计进行布局规划。

2、逻辑级数过多

在FPGA设计中,逻辑级数越高,意味着资源的利用率越高,但对设计工作频率的影响也越大。而且对于逻辑级数过多,ISE实现工具是没有任何改善的,必须通过修改代码来提高性能。

相应的解决方案有:

①使用流水线级数,在组合逻辑中插入寄存器,简化原有的逻辑结构;

②检查该路径是否多周期路径,如果是,添加相应的多周期约束;

③具备良好的编码习惯,不要嵌套if语句或if、case语句,并且尽量用case语句替代if语句。

3、信号扇出过高

信号高扇出会造成信号传输路径过长,从而降低时序性能。

相应的解决方案:

①通过逻辑复制的方法来降低信号的高扇出,可在HDL代码中手动复制或通过在综合工具中设置达到目的;

②可利用区域约束,将相关的逻辑放置在一起,当然笨方法仅限于高级用户。

扫码关注

扫码关注