- 全部

- 默认排序

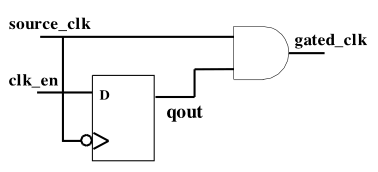

一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。1、全局时钟全局时钟即同步时钟,它是通过FPGA

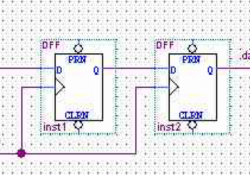

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

小伙伴们在学习FPGA时,最怕遇到同步时序电路设计,然而作为FPGA主要电路,同步时序电路试验频率居高不下,所以今天讲讲一些技巧,如如何实现同步时序电路的延时?如何实现RAM/ROM/CAM?1、FPGA设计中如何实现同步时序电路的延时?首

扫码关注

扫码关注