一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。

1、全局时钟

全局时钟即同步时钟,它是通过FPGA芯片内的全局时钟布线网络或区域时钟网络来驱动,全局时钟具有高扇出、高精度、低Jitter和低Skew的特点,它到芯片中的每一个寄存器的延迟最短,且该延迟可被认为是固定值,所以全局时钟是最常见的设计方法。全局时钟的设计有以下几种方法:

①由PLL锁相环来产生全局时钟;

②将FPGA芯片内部逻辑产生的时钟分配至全局时钟布线网络;

③将外部时钟通过专用的全局时钟输入引脚引入FPGA。

一般常推荐电路中的所有时钟都由PLL锁相环产生,一方面,PLL锁相环可以实现倍频和移相的操作,很容易获取所需频率和相位的时钟;另一方面,PLL锁相环默认将其驱动的时钟分配至全局时钟网络或区域时钟网络。

2、内部逻辑时钟

是指由芯片内部的组合逻辑或计数器分频产生的时钟。

对于组合逻辑时钟,特别是由多级组合逻辑产生的时钟,是要被阉割禁止使用,因为一方面组合逻辑极容易产生毛刺,特别是对多级组合逻辑;另--方面组合逻辑电路的Jitter和Skew比较大,这将恶化时钟的质量。所以,- -般组合逻辑产生的内部时钟仅仅适用于时钟频率较低、时钟精度要求不高的情况。

对于计数器分频产生的时钟,也应该尽量少地使用,因为这种时钟会带来比较大的延迟,降低设计的可靠性,也使得静态时序分析变得复杂。计数器分频时钟需完成的逻辑功能完全可由PLL锁相环或时钟使能电路替代。

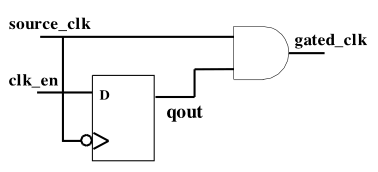

3、门控时钟

一般情况下,我们应尽量避免使用门控时钟,因为经组合逻辑产生的门控时钟极有可能产生毛刺,对系统造成很大的维护,但对于特定功耗大的系统来说,需要通过门控时钟来降低功耗,

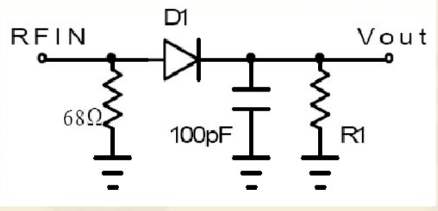

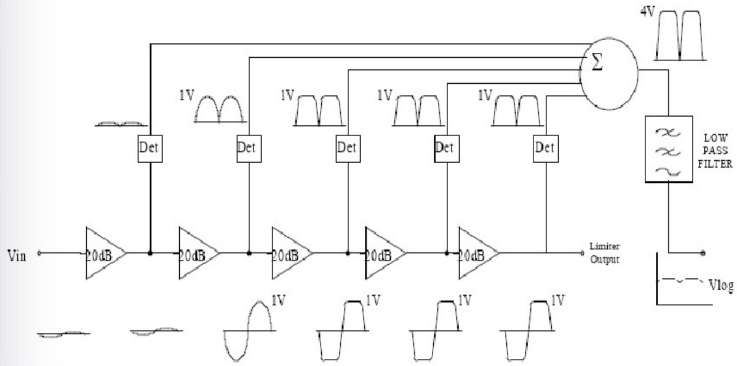

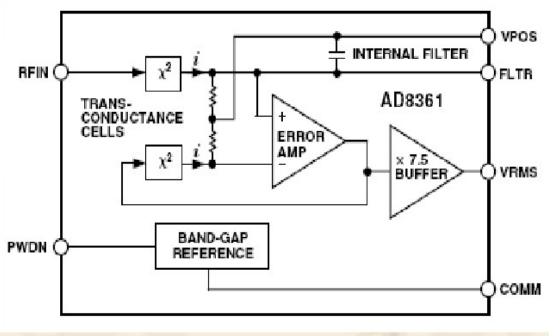

常用的门控时钟如图所示,该设计一般不产生毛刺和亚稳态问题。

扫码关注

扫码关注