FPGA和CPLD都属于可编程逻辑器件,有着很多共同特点,但由于FPGA和CPLD的结构差异,所以它们的区别也很大,所以本文将详谈FPGA和CPLD的区别及联系。

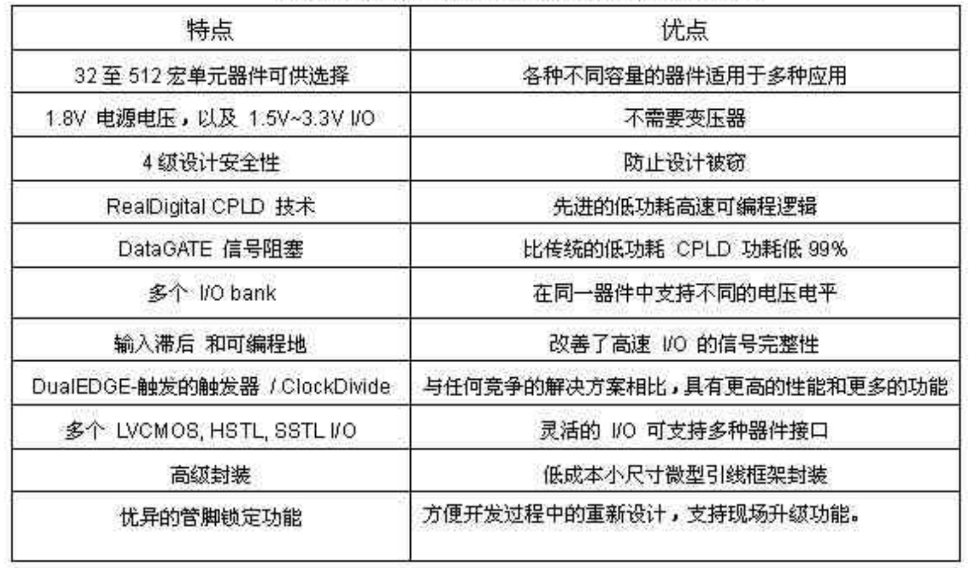

1、CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。换句话说,FPGA更适合触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构。

2、CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。

3、在编程上FPGA比CPLD具有更大的灵活性,CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门下编程,而CPLD是在逻辑块下编程。

4、FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

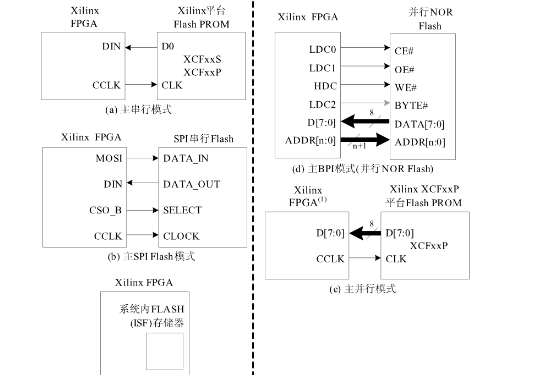

5、CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需要存放在外部存储器上,使用方法复杂。

6、CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于FPGA是门级编程,并且CLB之间采用分布式互连,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集中式。

7、在编程方式上,CPLD主要是基于E2PROM或FLASH存储器编程,编程次数可达一万次,优点是系统断电时编程信息也不丢失。CPLD又可分为在编程器上编程和在系统编程两类。FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从器件外部将编程。数据重新写入SRAM中。其优点是可以编程任意次,可在工作中快速编程,从而实现板级和系统级的动态配置。

8、CPLD保密性好,FPGA保密性差。

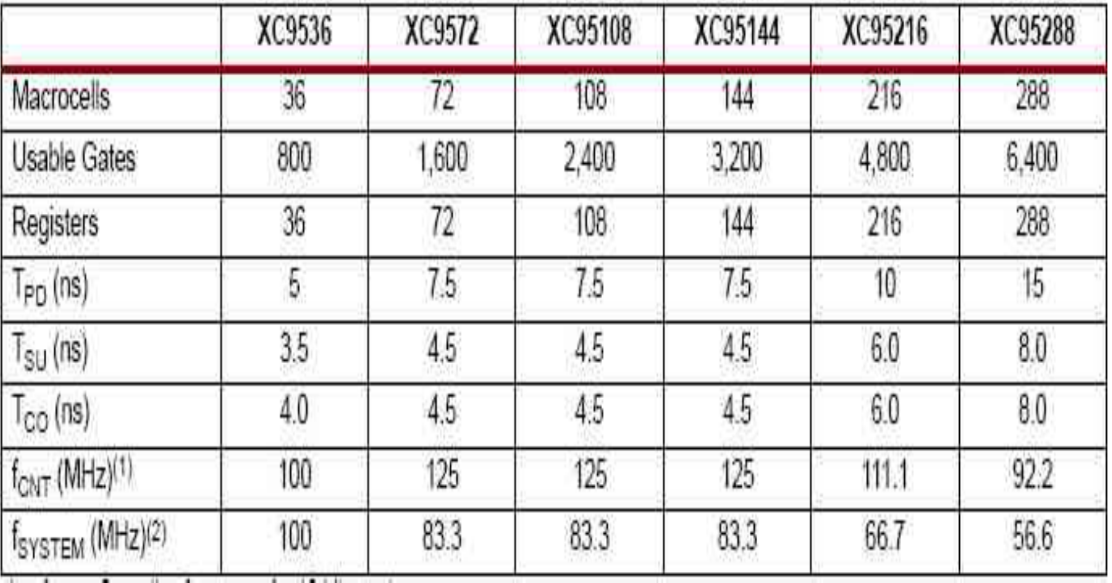

9、一般情况下,CPLD的功耗要比FPGA大,且集成度越高越明显。CPLD最基本的单元是宏单元。一个宏单元包含一个寄存器(使用多达16个乘积项作为其输入)及其它有用特性。因为每个宏单元用了16个乘积项,因此设计人员可部署大量的组合逻辑而不用增加额外的路径。这就是为何CPLD被认为是“逻辑丰富”型的。宏单元以逻辑模块

的形式排列(LB),每个逻辑模块由16个宏单元组成。

宏单

元执行一个AND操作,然后一个OR操作以实现组合逻辑。

欲了解更多的FPGA知识,来《集成电路FPGA/ASIC设计技巧提升》。

扫码关注

扫码关注