FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。

偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信号,包括OFFSET_IN_BEFORE、OFFSET_IN_AFTER、OFFSET_OUT_BEFORE、OFFSET_OUT_AFTER等4类基本约束,便宜约束的基本语法为:

OFFSET = [IN | OUT] "offset_time" [units]{BEFORE | SFTER} "clk_name"

[TIMEGRP "group_name"];

其中[IN | OUT]说明约束的是输入还是输出。“offset_time”为数据和有效时钟沿之间的时间差,{BEFORE | AFTER}表明该时间差是在有效时钟之前还是之后,“clk_name”为有效时钟的名字,[TIMEGRP "group_name"];是用户添加的分组信号,在缺省时,默认为时钟clk_name所驱动的所有触发器。偏移约束通知布局布线器输入数据的到达时刻,从而可准确调整布局布线的过程,使约束信号建立时间满足要求。

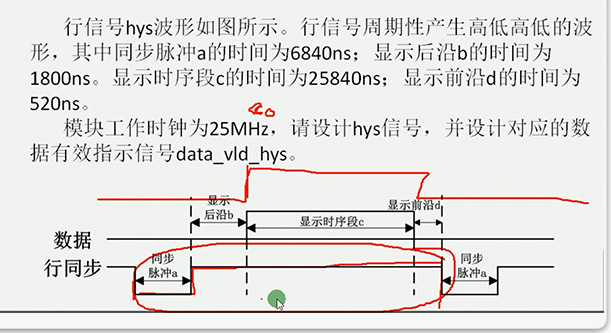

1、“OFFSET IN”偏移约束

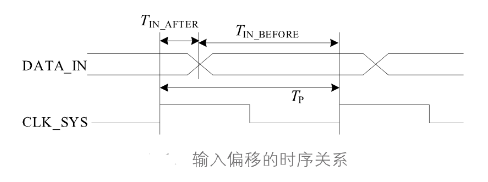

“OFFSET IN”偏移约束是输入偏移约束,有OFFSET_IN_AFTER和OFFSET_IN_BEFORE两种,前者定义了输入数据在有效事中到达多长时间后可以到达芯片的输入管教,这样可以得到芯片内部的延迟上限,从而对那些与输入引脚相连的组合逻辑进行约束;后者定义数据比相应的有效时钟沿提前多少时间到来,是与其相连的组合逻辑的最大延时,否则在时钟沿到来时,数据不稳定,会发生采样错误。输入偏移的时序关系如图所示:

2、“OFFSET OUT”偏移约束

“OFFSET OUT”偏移约束是输出偏移约束,有OFFSET_OUT_AFTER和OFFSET_OUT_BEFORE两种,前者定义了输出数据在有效事中沿之后多长时间稳定下来,是芯片内部输出延时的上限;后者定义了在一个时钟信号到来之前多长时间必须输出数据,是下一级逻辑建立时间的上限。输出偏移的时序关系如图所示:

扫码关注

扫码关注