- 全部

- 默认排序

PCB设计当中,为了满足时序匹配的要求,我们通常对数据总线进行等长,那么等长的时候,我们需要用到蛇形走线,那关于蛇形等长的参数设置及要求是怎么样的呢,我们又需要去学习呢?

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,b.能有效抑制EMI,c.时序定位精确, 那么在实际设计当中,Altium Designer软件当中差分是怎么定义添加的,又是怎么设置相关规则的呢?我们一起来学习下吧!

本课程介绍了FPGA SDRAM文档的阅读和理解、SDRAM的功能汇总、SDRAM的实现架构、SDRAM接口的模块划分、SDRAM的时序分析和约束。

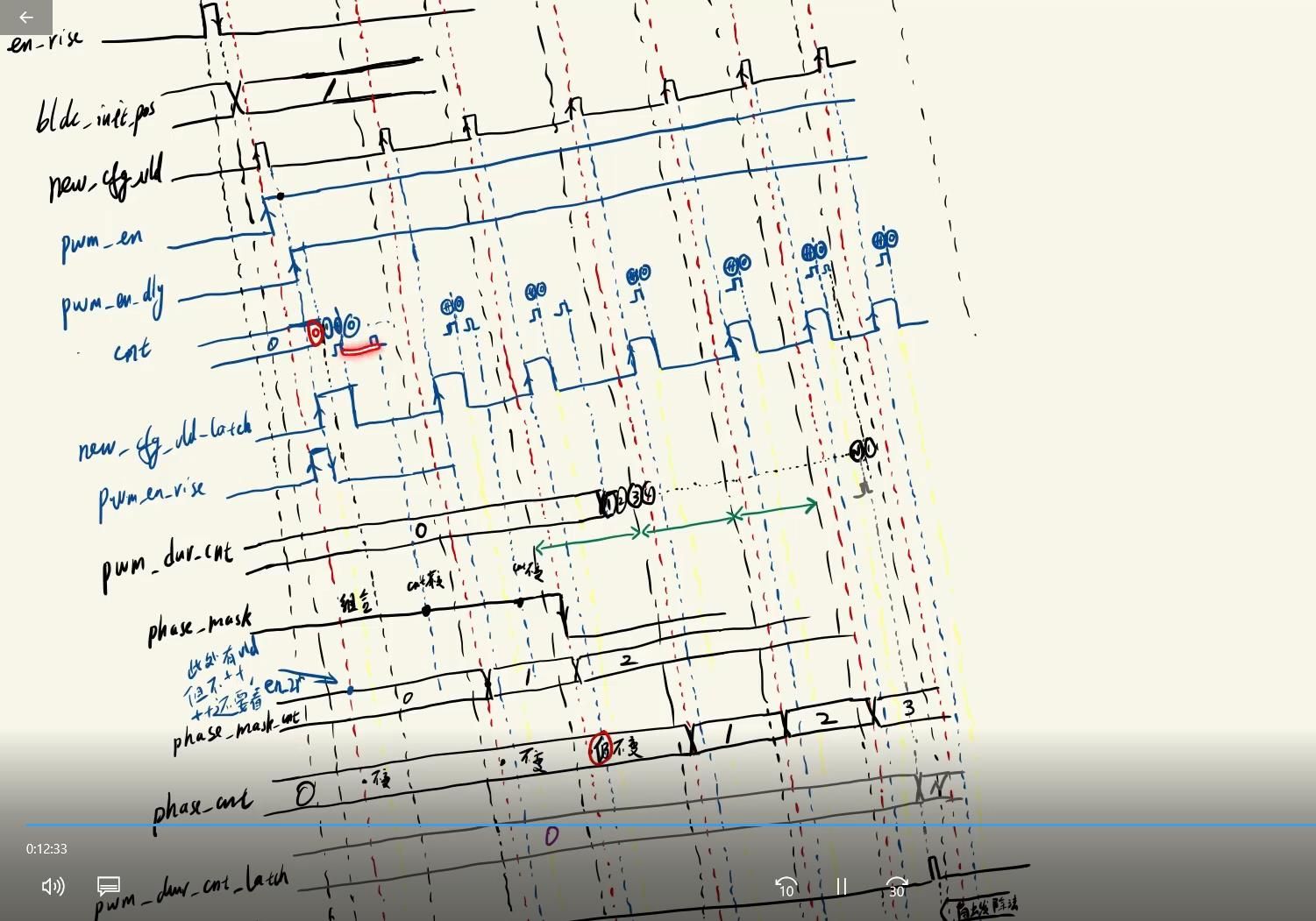

数字设计的时序图的画法

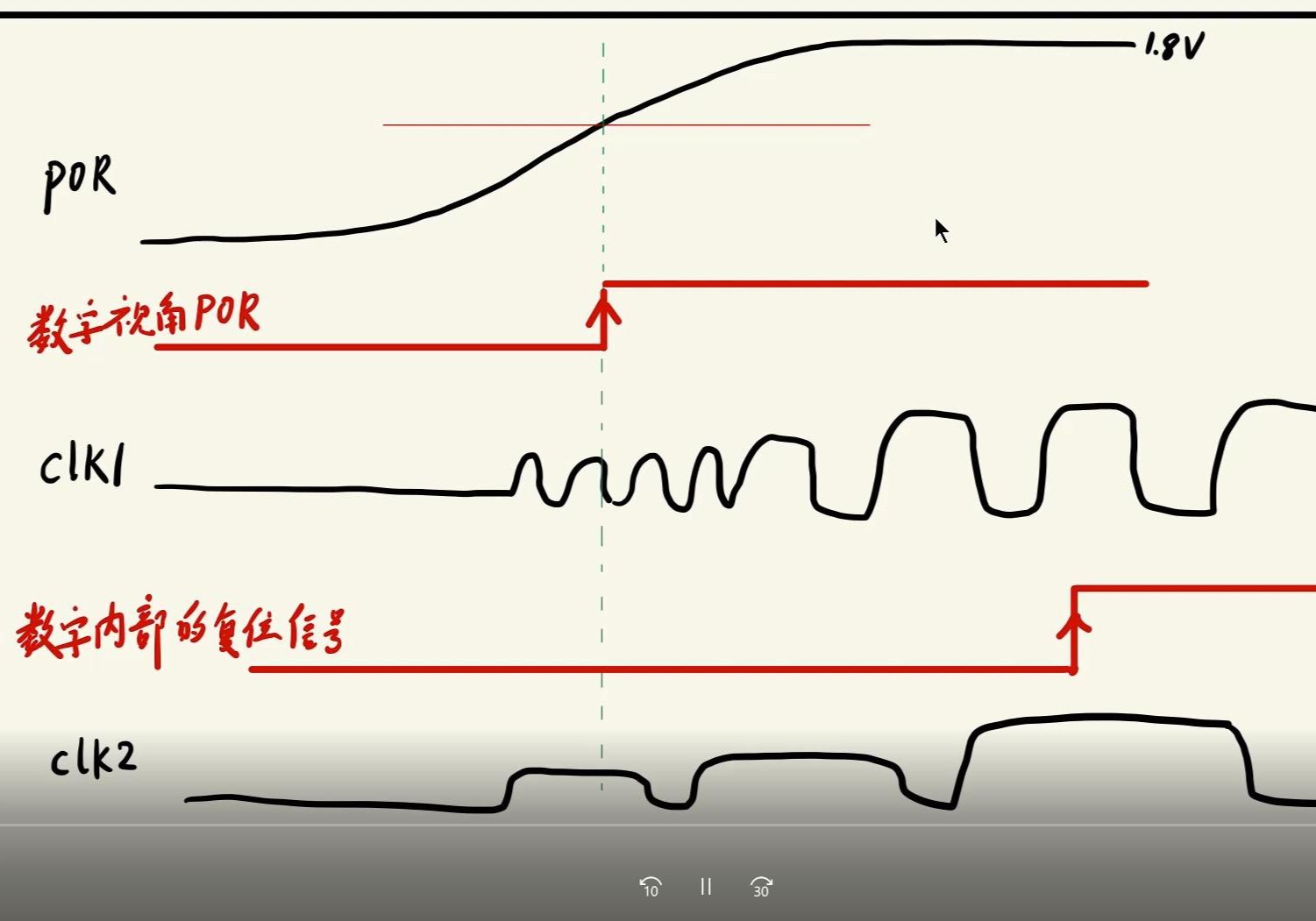

芯片的上电时序经验谈

时序图的讲解

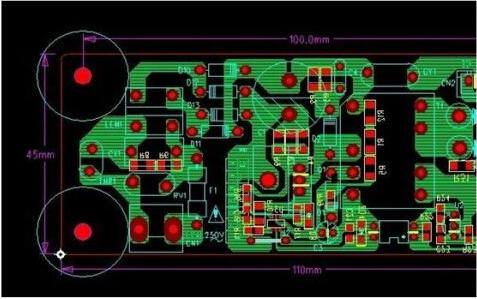

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

扫码关注

扫码关注