在FPGA设计里,状态机的设计是最为重要的环节之一。很多FPGA系统里的运行成功基本上和状态机设计相关,毫不夸张地说,FPGA系统的成功,其中一半归于状态机。所以我们该如何做好状态机?

一般来说,工程师在状态机的设计中基本采用两段式写法(2个always模块)或三端式写法(3个always模块)。

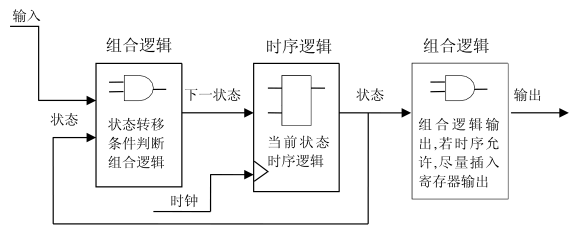

1、两段式写法

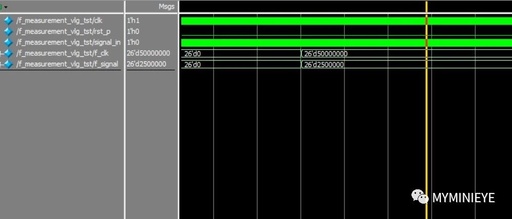

两段式写法的核心思想是:一个always模块采用同步时序描述状态转移,另一个always模块采用组合逻辑方式频段状态转移条件,描述状态转移规律,其结构如下图:

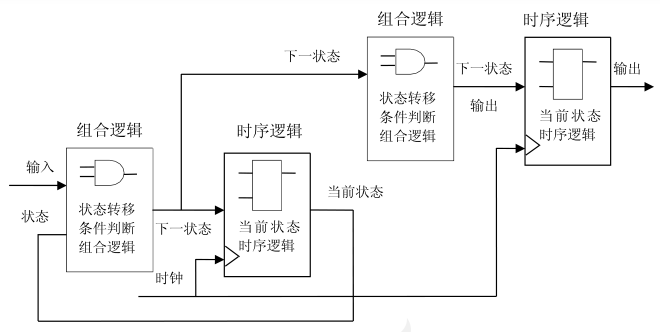

2、三段式写法

三段式写法的核心思想是:一个always模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断转移条件,描述状态转移规律,第三个always模块使用同步时序电路描述每个状态的输出,其结构如下图:

3、状态机设计的其他技巧及注意事项:

①状态机的编码最好使用one-hot(独热码);

②一个完备的状态机应具备初始化状态和默认状态;

③状态机的编码可以用parameter定义,不推荐使用define宏定义;

④时序逻辑always模块使用非阻塞幅值“<=”,组合逻辑模块使用阻塞赋值“=”;

⑤使用完备的if...else语句和case语句;

⑥case语句需具备full_case和parallel_case属性,full_case定义了所有可能的输入模式,parallel_case定义了case项是不重复的。

扫码关注

扫码关注