12.4 模块化设计

12.4.1 CPU的设计

1.电容的放置

CPU电源布线时都需要一些电容。滤波电容(也作旁路电容)放置在距离电源较近的位置。用旁路电源位置引入的高频信号,如果不加旁路电容,高频干扰可能从电源部分引入芯片的内部。退耦电容在数字电路高速切换时起到缓冲电压变化的作用。一般来说,大电容放置在主控芯片背面(或就近),以保证电源纹波在100mV以内,避免在大负载情况下引起电源纹波偏大。

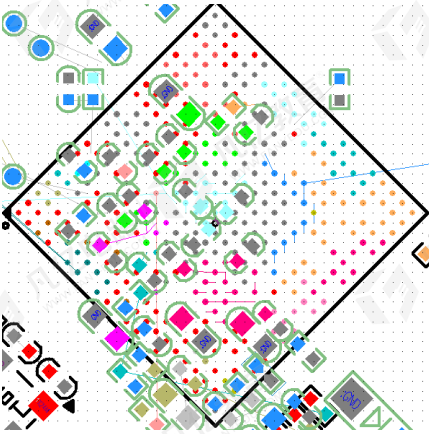

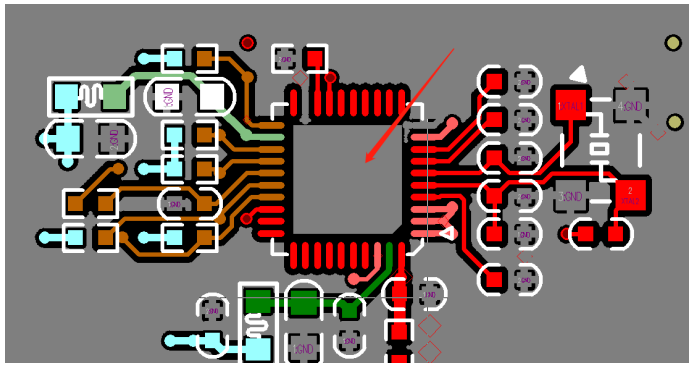

此实例由于结构限制,小电容靠近CPU背面进行放置,大电容就近放置在CPU周围及路径上,如图12-6所示。

图12-6 滤波电容的放置

2.电源供电的设计

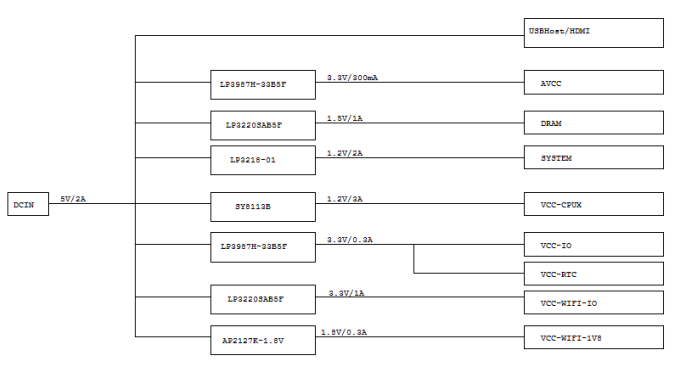

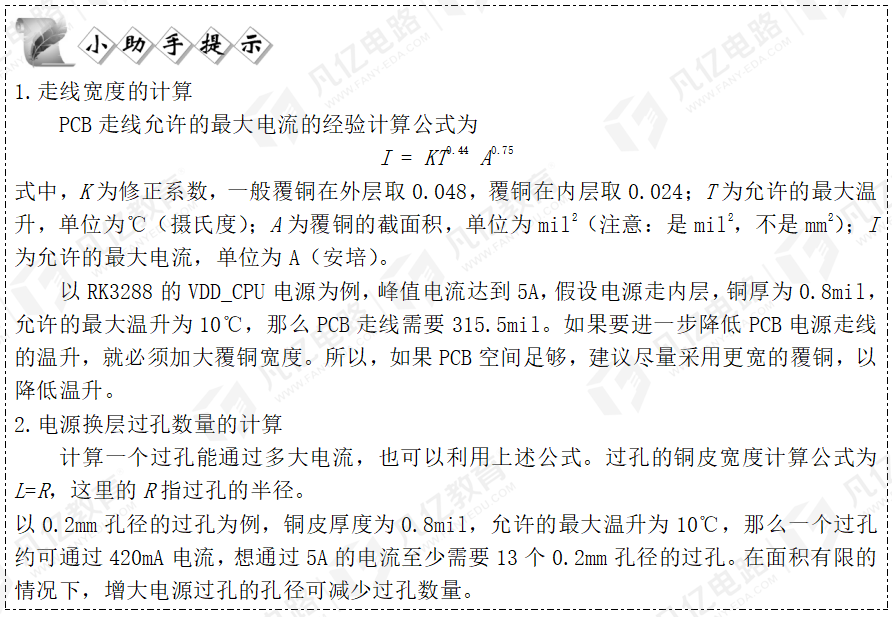

电源供电的设计至关重要,直接影响产品的性能及稳定性,应严格按设计中电流参数要求进行设计。VDD_CPU为主控供电,峰值电流分别可达3A。从电源模块输出到主控相应电源管脚之间保证有大面积的电源覆铜,一般过载通道为3~5mm,承载过孔设置为0.3mm(孔)/0.5mm(盘),数量为8~14个,可提高过电流能力,并降低线路阻抗。如图12-7所示为该设计的电源树枝图。

图12-7 电源树枝图

3.晶振的设计

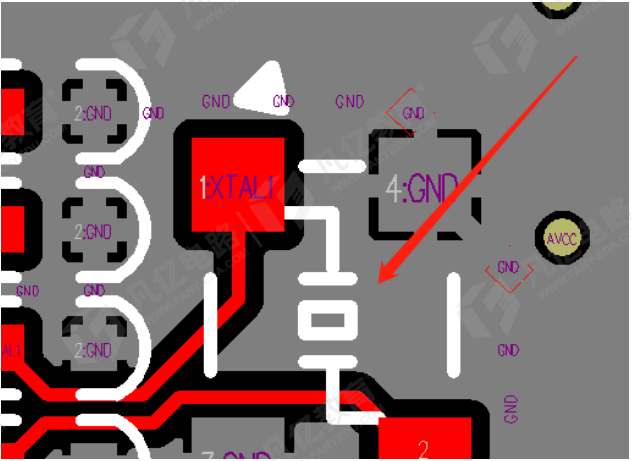

晶振是一个干扰源,本体表层及第二层禁止其他网络走线,并注意在晶振管脚及负载电容处多打地过孔。

晶振走线应尽量短,尽量不要打孔换层,走线和元件同面,并且采用p形滤波方式,如图12-8所示。

图12-8 晶振的走线

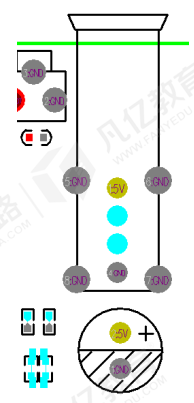

4.其他设计

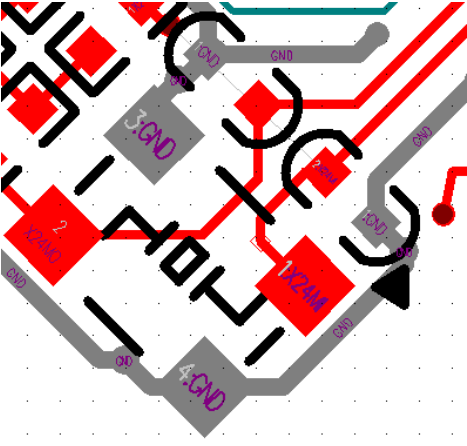

在主控下方的地过孔需要足够多,如图12-9所示,尽可能地多打过孔,均匀放置并交叉连接,以改善电源质量,提高散热性,并提高系统的稳定性。电源信号也可以采用这种方式加大载流及散热。

图12-9 CPU地及电源的连接方式

12.4.2 存储器DDR3的设计

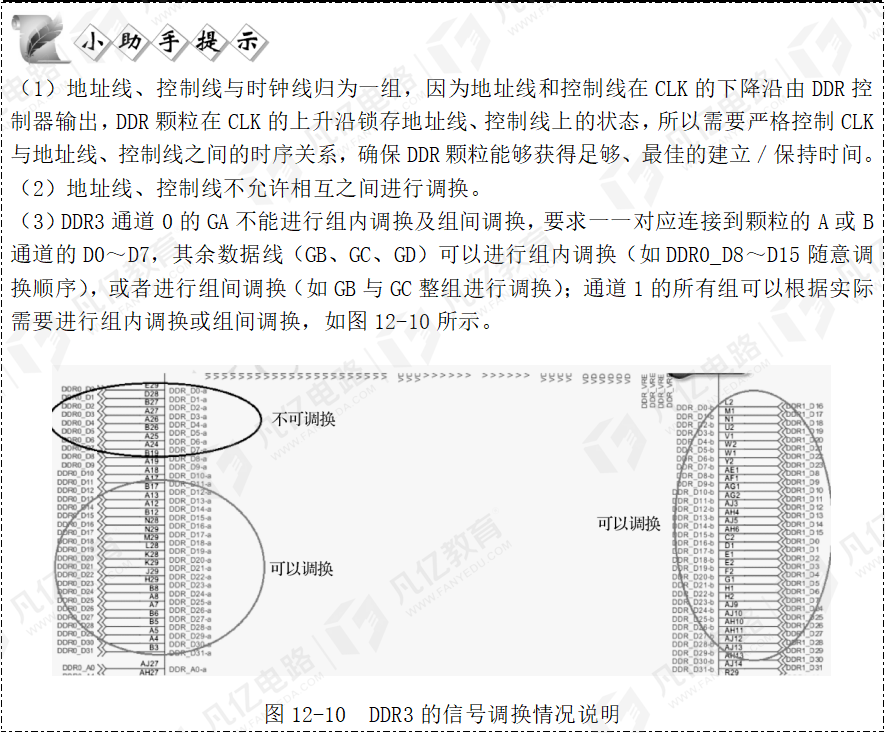

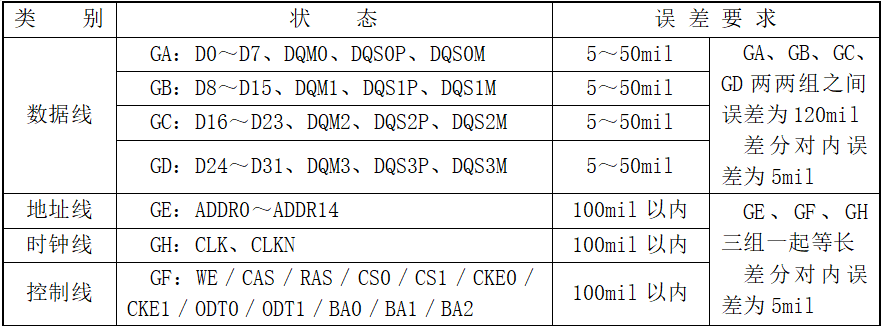

1.信号分类

可以对此实例的双通道DDR3的信号进行大致分类,如表12-3所示。

表12-3 DDR3的信号分类

2.阻抗控制要求

数据线、地址线及控制线单端走线控制50Ω阻抗,DQS差分线和时钟差分线需要控制100Ω差分阻抗。具体的走线线宽与间距可以参考阻抗叠层章节。

3.DDR3的布局

本实例中DDR为两片DDR,拓扑结构采用T点设计,两片DDR中心对齐,对称放置,并预留等长的空间,不宜过近或过远,关于CPU中心对齐。DDR3滤波电容要靠近IC管脚摆放,可以考虑放到IC背面。主芯片和DDR颗粒的每个VCC_DDR管脚尽量在芯片背面放置一个退耦电容,而且过孔应该紧挨着管脚放置,以避免增大导线的电感。DDR3的布局如图12-11所示。

图12-11 DDR3的布局

4.DDR3的布线

(1)同组同层:为了尽量保证信号的一致性,数据线尽量做到同组同层,如GA组11条信号线走在同一层,GB组11条信号线走在同一层;地址线、控制线没有这个要求。

(2)3W原则:为了尽量减少串扰的产生,信号线之间满足3W原则,特别是数据线之间;组与组之间满足3W及以上间距;差分线与信号线间距满足3W及以上间距;差分Gap间距满足3W及以上间距,同时振幅不要超过180mil。

(3)平面分割:为了不使阻抗突变,所有属于DDR的信号线不允许有跨分割的现象,即不允许信号线穿越不同的电源平面。

(4)等长要求:有关要求如下。

① GA~GD组中数据线及DQSP、DQSM之间的线长误差控制在5~50mil(速率越高,要求越严格);每组内的DQSP、DQSM差分对内误差控制在5mil以内;组与组的数据线不一定要求严格等长,但是尽量靠近,控制在120mil以内。

② GE、GF、GH组的信号线的线长误差控制在100mil以内,时钟差分需要控制对内误差为5mil。

DDR3的等长要求如表12-4所示。

表12-4 DDR3的等长要求

(5)VREF的处理:VREF尽量靠近芯片;VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰);VREF只需要提供非常小的电流(输入电流大概为3mA);每一个VREF管脚都要靠近管脚加1nF旁路电容(每路电容数量不超过5个,以免影响电源跟随特性);线宽建议不小于10mil。

(6)保证平面完整性:DDR部分的平面完整性会直接影响DDR性能及DDR兼容性;在设计PCB的时候,注意过孔不能太近,以免造成平面割裂,一般推荐两孔中心间距大于32mil,两孔之间可以穿插铜线,如图12-12所示。

图12-12 DDR3的平面完整性

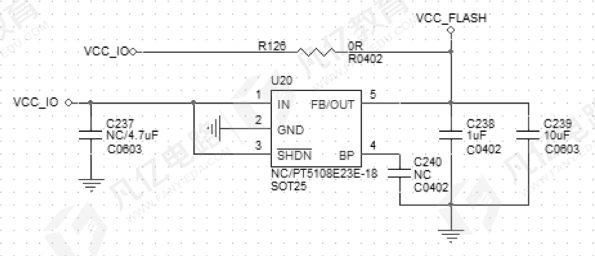

12.4.3 存储器NAND Flash/EMMC的设计

1.原理图

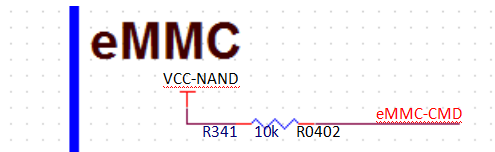

全志H3芯片支持NAND Flash、EMMC等Flash存储设备。使用NAND Flash时,控制器及颗粒供电VCC_NAND为3.3V,而不同版本的EMMC,控制器及颗粒供电VCC_NAND可能为1.8V(EMMC4.1以上)或者3.3V,设计时根据数据表调整并修改。FLASH0_VOLTAGE_SEL默认3.3V时下拉到GND,1.8V时上拉到VCC_NAND,如图12-13所示。

图12-13 FLASH0_VOLTAGE_SEL上拉状态

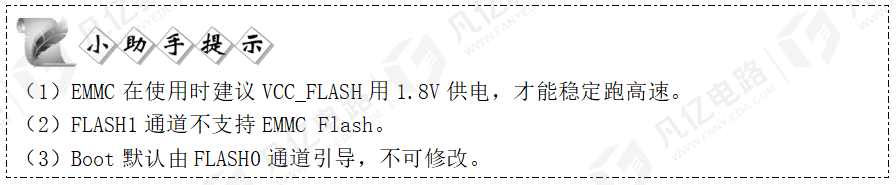

EMMC默认为1.8V LDO供电,如图12-14所示,可兼容EMMC4.1以下颗粒,可以使产品备料范围更广。

图12-14 EMMC供电兼容

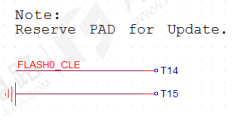

为了方便在开发阶段进入Mask Rom固件烧写模式(需要更新Loader),在使用NAND Flash时FLASH_CLE需预留测试点,在使用EMM时EMMC_CLKO也要预留测试点,如图12-15所示。

图12-15 测试点的添加

2.PCB部分

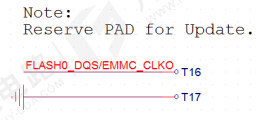

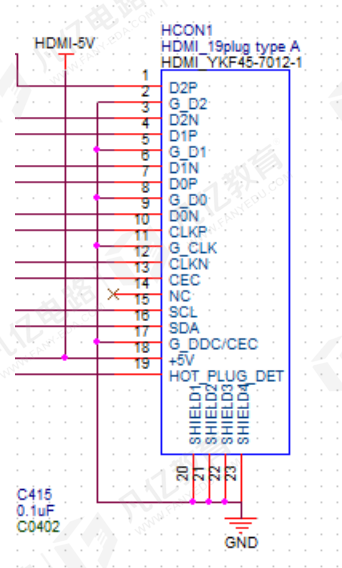

图12-16 EMMC的出线方式

(1)NAND Flash与EMMC一般通过双布线兼容设计,EMMC的出线方式如图12-16所示。EMMC芯片下方在覆铜时,焊盘部分需要增加覆铜禁布框,避免铜皮分布不均匀影响散热,导致贴片时出现虚焊现象。

(2)走线尽量走在一起,并包地处理,空间准许的情况下可以等长处理,误差不要超过±100mil,以提高EMMC的稳定性和兼容性。

(3)EMMC处为BGA为0.5mm的Pitch间距,为了避免局部使用较小的线宽和间距提高整体生产难度及成本,无用的焊盘可以通过改小的办法出线,如图12-16所示。

12.4.4 HDMI的设计

1.原理图

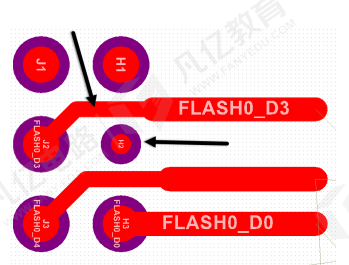

原理图中的管脚定义如图12-17所示。

图12-17 HDMI管脚定义

HDMI信号走线需按3W原则要求走线;为抑制电磁辐射,建议差分信号线整组包地,并保证走线参考面连续完整;走线尽量少换层,因为过孔会造成线路阻抗的不连续。

2.PCB

(1)差分匹配电阻作用:

①ESD作用。

②微调电阻。

③放置要求:靠近接口,并排放置。

(2)差分信号线布线要求:

①四队差分之间的等长误差为10mil,同一对差分组内等长误差为5mil。

②差分对与差分对之间保持3W以上的间距。

③靠近GND层走线。

④包地处理。

12.4.5 百兆网口的设计

以太网是现在最普遍的局域网技术。Ethernet接口实质是MAC通过MII总线控制PHY的过程。以太网接口电路主要由MAC控制器和物理接口构成,目前常见的网口接口芯片有LXT971、RTL8018、CS8900、DM9008等。

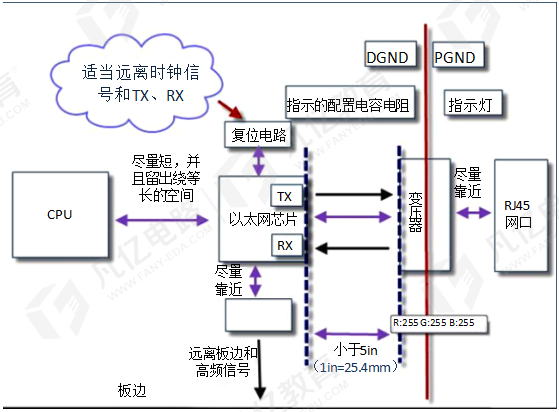

总体设计要求如图12-18所示。

图12-18 总体设计要求

布局布线的原则如下所述。

(1)变压器下面所有层挖空。

(2)选择最优的信号层布线,过孔数量不要超过两个。换层的时候在孔的周边加上回流地过孔。

(3)网口模块的电源线要粗而滤波电容的放置位置和数量要合理。

(4)RJ45和变压器之间的距离应尽可能缩短。

(5)复位电路应尽可能靠近网口转换芯片,原理电路板边缘、其他的高频信号、IO端口。走线或磁性元件周围。

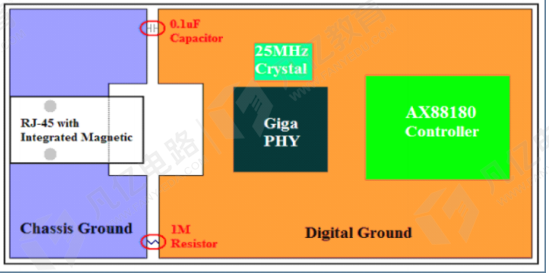

(6)百兆网口为两对差分,对内等长应做到5mil以内。电源和地的处理如图12-19所示。

图12-19 电源和地的处理

12.4.6 USB OTG的设计

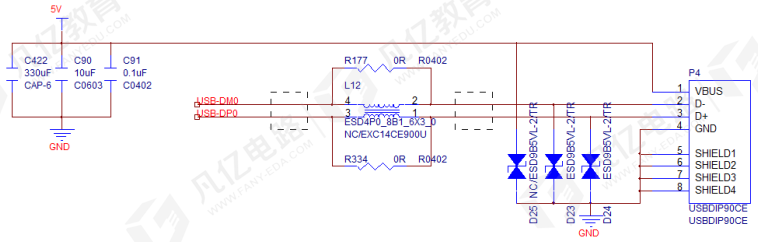

USB 控制器参考电阻R60、R61选用1%精度的电阻,参考电阻关系到USB眼图的好坏。USB 具有高达480Mbps的传输速率,差分信号对线路上的寄生电容非常敏感,因此要选择低结电容的ESD保护元件,结电容要小于1pF。同时,为抑制电磁辐射,可以考虑在信号线上预留共模电感,在调试过程中根据实际情况选择使用电阻或者共模电感,如图12-20所示。

图12-20 OTG设计

布线注意事项如下。

(1)USB差分走线越短越好,综合布局及结构进行调整。

(2)DP/DM 90Ω差分走线,严格遵循差分走线规则,对内误差满足5mil。

(3)为抑制电磁辐射,USB建议在内层走线,并保证走线参考面是连续完整的,不被分割,否则会造成差分线阻抗的不连续,并增加外部噪声对差分线的影响。空间充足的情况下进行包地处理。同时,尽量减少换层过孔,因为过孔会造成线路阻抗的不连续,实在需要的时候建议在打孔换层处放置地过孔。

(4)ESD保护元件、共模电感和大电容在布局时应尽可能靠近USB接口摆放,走线先经过ESD元件及共模电感之后再进入接口,如图12-21所示。

图12-21 ESD元件及共核电感后走线的处理

(5)USB 2.0规范定义的电流为500mA,但是USB_VBUS走线最好能承受1A的电流,以防过流。如果是在使用USB充电的情况下,USB_VBUS走线要能承受2.5A的电流。

12.4.7 WIFI/BT的设计

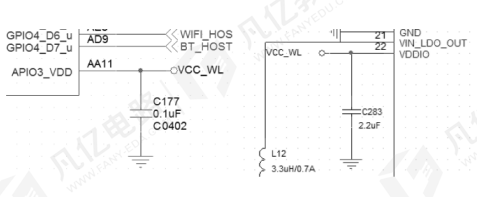

全志H3支持SDIO接口的WIFI/BT模块,采用SDIO、UART接口的WIF/BTI模块时,需要注意 SDIO、UART控制器的供电APIO3_VDD要与模块VCCIO Supply一致,如图12-22所示。

图12-22 APIO3_VDD供电

注意WIFI需选择ESR小于60Ω、频偏误差小于20ppm的晶振。对于晶振的匹配电容,可根据晶振规格选择合适的电容值,避免频偏太大而出现的工作异常(如热点数较少等),如图12-23所示。

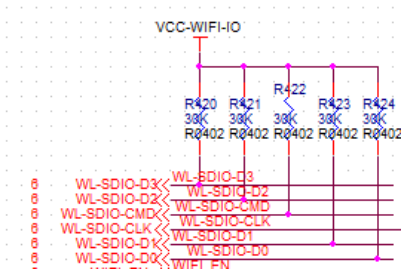

预留SDIO上拉电阻,上拉电阻(图12-24所示)贴片可提高信号质量。

图12-23 晶振及匹配电容 图12-24 SDIO上拉电阻的连接

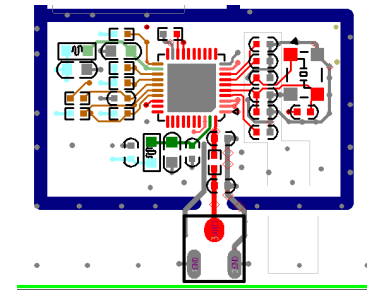

WIFI/BT模块属于易受干扰的模块,PCB布线时注意远离电源、DDR等模块,在空间充足的情况下,建议添加屏蔽罩,如图12-25所示。

图12-25 WIFI/BT模块的屏蔽罩

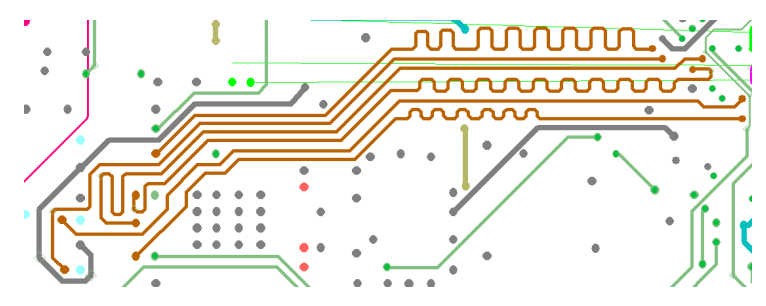

SDIO走线作为数据传输走线,需尽可能平行,并进行整组包地处理。如果有空间的话,CLK建议单独包地。需避免靠近电源或高速信号布线。同时,信号组内任意两条信号线的长度误差控制在400mil以内,尽量等长,否则会导致SDIO高速模式下频率跑不高。SDIO走线处理如图12-26所示。

图12-26 SDIO走线处理

如图12-27所示,同样是为了避免干扰,模块下方第一层保持完整的地,不要有其他信号走线,其他信号走线尽量走在内层。

图12-27 WIFI/BT模块的地平面处理

晶振本体下方保持完整的地,不要有其他信号走线,晶振管脚要有足够的地过孔进行回流,如图12-28所示。

图12-28 晶振的处理

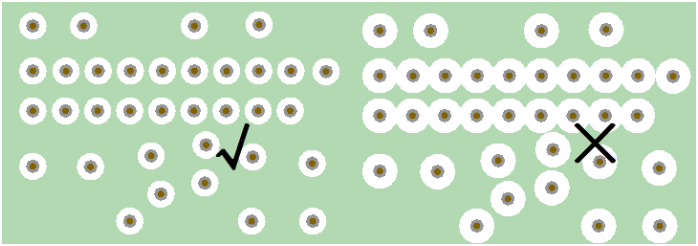

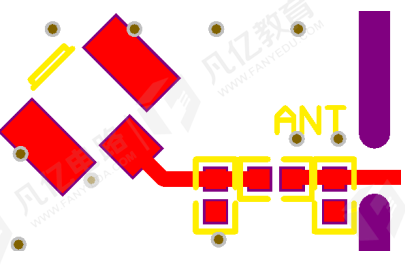

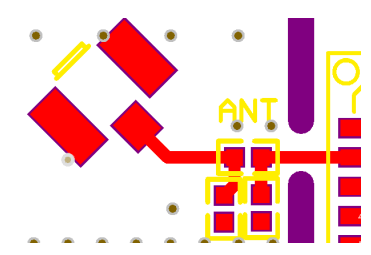

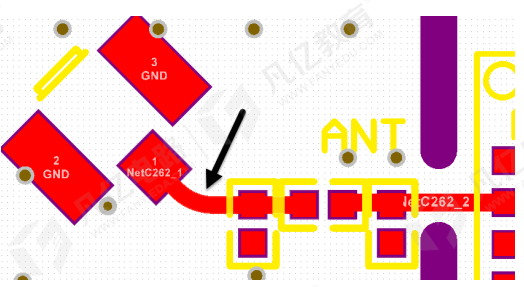

天线及微带线宽度设计需考虑到阻抗,阻抗严格为(50±10)Ω。走线下方需有完整的参考平面作为RF(射频)信号的参考地,天线布线越长,能量损耗越大,因此在设计时,天线路径越短越好,不能有分支出现,不能打过孔。图12-29所示为WIFI/BT天线错误的走线方法。天线走线需转向时,不可以用转角的方法,需用弧形走线。图12-30所示为WIFI/BT天线正确的走线方法。

图12-29 WIFI/BT天线错误的走线方法

图12-30 WIFI/BT天线正确的走线方法

扫码关注

扫码关注