1、元器件间距检查

1)元器件选择小间隙、紧凑布局时是可以提升空间的利用,但是会引发元器件空间干涉的等问题。

2)元器件布局间距小,影响SMT的可靠性,甚至影响元器件的可焊性。

3)避免元器件间距不足的隐患,制版前需进行可焊性检查,如图1所示。

图1 检测各类元器件间距

2、器件到边缘检查

1)元器件布局太靠近板边,成型铣削或裁板会伤及板边的焊盘,影响SMT焊接。

2)在过机器时元器件可能会碰到机器的导轨,导致元器件被撞坏。

3)避免靠近板边的元器件存在组装隐患,元器件布局距板边大于5mm或加工艺边,且制板前进行可组装性检查,如图2所示。

图2 检查器件到板边

3、贴片引脚检查

1)贴片引脚的脚趾、脚后跟,距焊盘的边缘距离不足,焊接会存在上锡量不足虚焊或焊接不牢的风险。

2)BGA球径引脚焊盘直径比引脚<20%,存在焊接上锡不足虚焊的风险。

3)提前检查焊盘与元器件引脚比例,保证足够上锡面积,避免贴片品质不良的风险,如图3所示。

图3 检查引脚的脚趾、脚后跟与焊盘比

4、通孔引脚检查:

1)插件(THT)元件的引脚封装设计应在合理的范围,公差过大放置器件会松动吃锡多,公差过小则无法插入焊接,封装设计请参考《PCB封装设计指导白皮书》。

2)设计插件(THT)元器件封装时需注意引脚孔的属性,引脚孔属性必须是PTH(金属孔),如设计为NPTH(非金属孔)则电气信号无法导通,如图4所示。

图4 检查通孔引脚设计的合理性

5、Chip焊盘检查

1)Chip器件的焊盘大小、间距需设计合理,否则会影响贴片的质量。如焊盘大小不一会导致贴片Chip器件立碑、焊盘过大导致Chip器件拉偏、焊盘内间距小导致贴片短路等。

2)针对各类Chip器件做可检查其封装名称与焊盘大小关系是否正确,封装设计请参考《凡亿电路PCB封装设计指导白皮书》,如图5所示。

图5 Chip器件可焊性检查

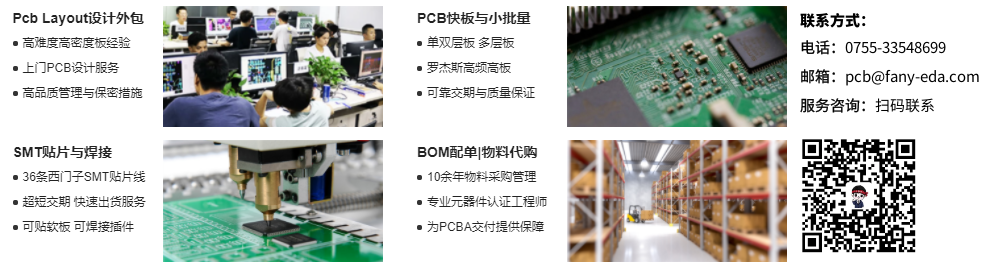

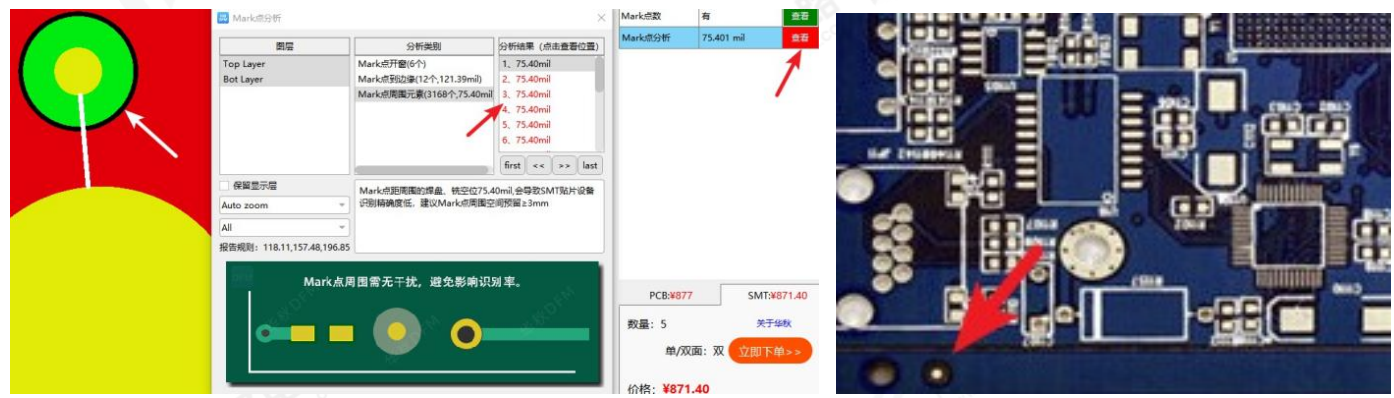

6、Mark点检查

1)Mark点也称基准点、光学点,是SMT自动贴片用作定位的点。Mark点的数量、Mark点的开窗大小、Mark的到板边的距离、Mark点周围的元素干涉都会影响SMT自动贴片的精准度(干涉范围参考华秋DFM规则管理)。

2)Mark点设计一般要3个或以上且不能对称,不对称设计Mark点目的是为了防错,如图6所示。

图6 检查Mark点设计是否合理

扫码关注

扫码关注