- 全部

- 默认排序

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

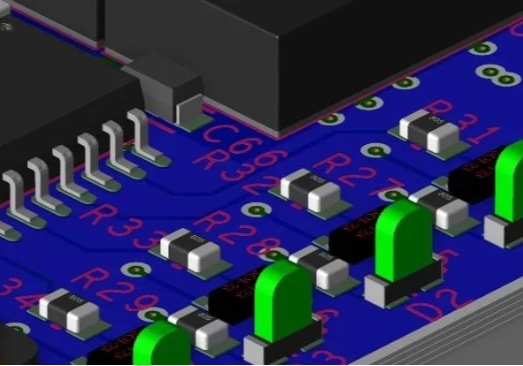

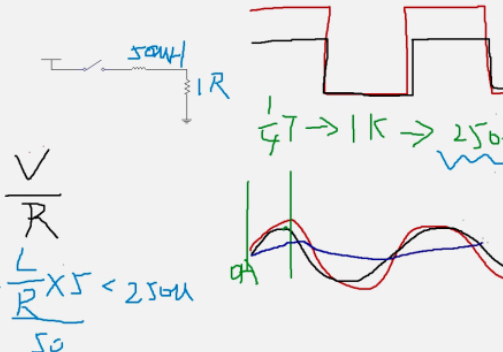

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

DDR布线技术的重要性在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。DDR的名称来源于其能够在每个时钟周期内发送和接收两次信号,是原先的单数据速率

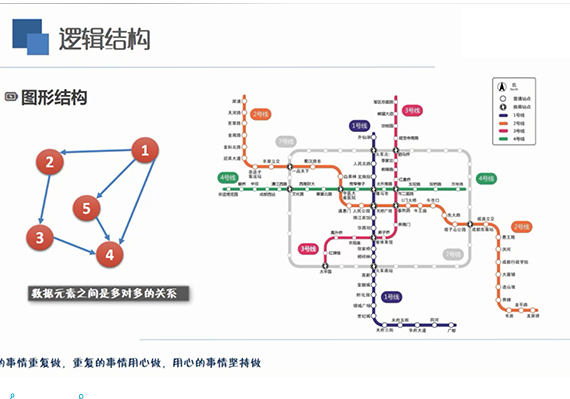

随着科技不断发展,物流行业开始转换为智慧物流,物流机器人也受到了物流行业的青睐,开始成为物流行业新一代宠儿。那么什么是物流机器人?它由那部分组成?凡亿教育嵌入式进阶系列:>>数据结构与算法实战课程>>嵌入式裸机时钟温度显示器物流机器人广义上

No.1 资料输入阶段在流程上接收到的资料是否齐全(包括:原理图、*.brd文件、料单、PCB设计说明以及PCB设计或更改要求、标准化要求说明、工艺设计说明等文件)。确认PCB模板是最新的。时钟器件布局是否合理。确认模板的定位器件位置无误。

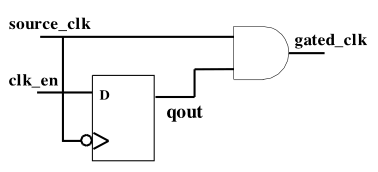

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

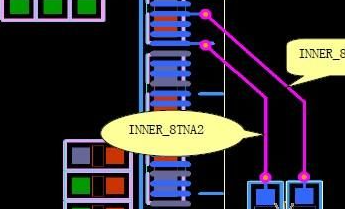

一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。1、全局时钟全局时钟即同步时钟,它是通过FPGA

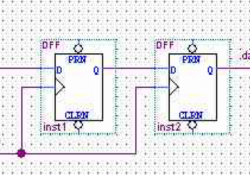

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

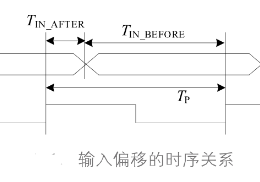

FPGA的时序分析及时序约束一直以来是小白难以搞懂的知识点,经常劝退不少小白,尤其是其中的偏移约束,所以本文将重点谈谈偏移约束。偏移约束属于基本时序约束,规定了外部时钟和数据输入输出引脚之间的相对时序关系,智能用于端口信号,不能应用于内部信

扫码关注

扫码关注