同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。

同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实际系统中,往往存在多时钟域的情况,这时同步的概念有所延伸,不再专指整个设计同步于同一时钟沿,而是指设计应该做到局部同步,在每个时钟域内的电路要同步于同一时钟沿。

1、同步电路设计的优点

①同步设计能有效地避免毛刺的影响,使得设计更可靠;

②同步设计易于添加异步复位reset,以使整个电路有一个确定的初始状态;

③同步设计可以减小环境对芯片的影响,避免器件受温度、电压、工艺的影响;

④同步设计可以使静态时序分析变得简单和可靠;

⑤同步设计可以很容易地组织流水线,提高芯片的运行速度。

2、同步电路的设计指南:

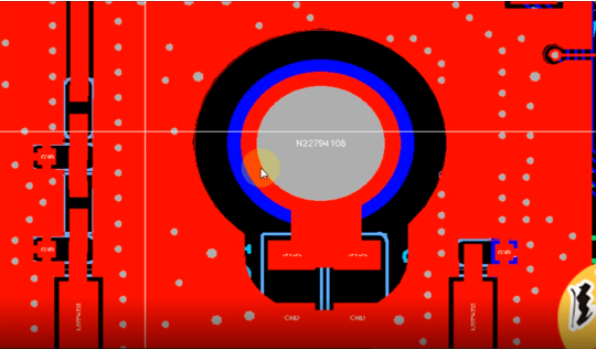

①尽可能在设计中使用同一时钟,时钟走全局时钟网络。走全局时钟网络的时钟是最简单、最可预测的时钟,它具有很强的驱动能力,可以驱动FPGA内部中的所有触发器,并保证Clock skew可以小到忽略的地步。

②避免使用混合时钟沿采样数据,即避免在设计中同时使用时钟的上升沿和下降沿。

③尽量少在模块内部使用计数器分频所产生的的时钟。计数器分频时钟需完成的逻辑功能完全可由PLL锁或时钟使能电路替代。计数器分频时钟的缺点是使得系统内时钟不可控,并产生较大的Clock skew,还使静态时序分析变得复杂。

④避免使用门控时钟,因为经组合逻辑产生的门控时钟极有可能产生毛刺,使D触发器误操作。

⑤当整个电路需要多个时钟来实现,则可以将整个电路分成若干局部同步电路(尽量以同一个时钟为一个模块),局部同步电路之间接口当做异步接口考虑,且每个时钟信号的时钟偏差要严格控制。

⑥电路的实际最高工作频率不应大于理论最高工作频率,留有设计余量,保证芯片可靠工作。

⑦电路中所有寄存器、状态机在系统被reset复位时应处在一个已知的状态。

扫码关注

扫码关注