用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。

Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)的基础上单边大0.2mm左右。

Sop类器件,place_bound层有引脚两侧比器件最大外围尺寸单边大1.35mm,无引脚侧比最大外围尺寸单边大1.5mm。

Qfp器件,place_bound层比器件最大外围尺寸的基础上四周大1.35mm。

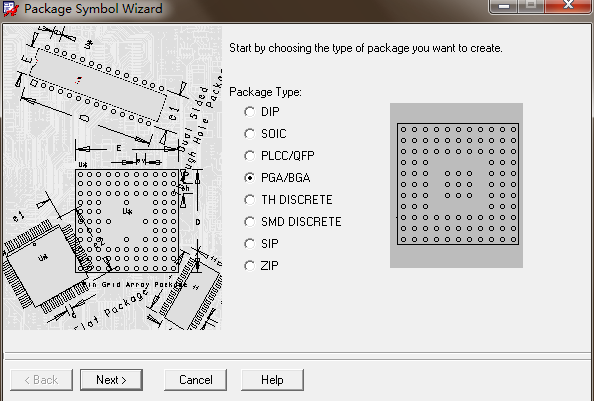

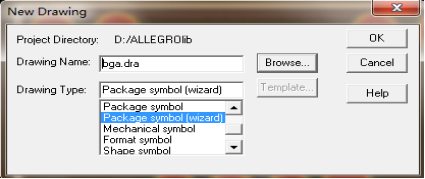

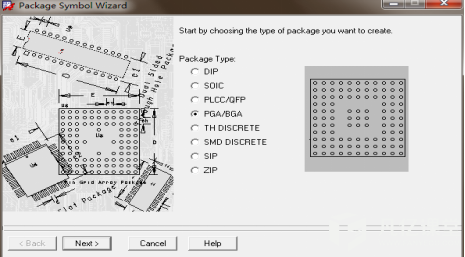

BGA器件,place_bound层比器件最大外围尺寸的基础上四周大5.0mm。

插装器件,place_bound层比器件最大外围尺寸的基础上四周大0.5mm。

连接器:立式安装器件,长边每边大5.0mm,对于弯式安装器件,背向板边的大5.0mm,板边可以为0。

其它类器件则分为插装和贴装:插装中PLACE_BOUND_TOP层的尺寸大小是在器件最大外围尺寸(焊盘和丝印中取大值)的基础上单边再加0.5mm,而贴装则在最大外围尺寸的基础上单边再加0.3mm。

扫码关注

扫码关注