- 全部

- 默认排序

用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。

新加坡将在水库上组装太阳能光伏系统,占地面积约45个足球场-新加坡公用事业委员会和森科工业公司已经开始在Tengeh水库上组装一个60兆瓦峰值浮动太阳能光伏系统。他们说,它占地相当于45个足球场,是世界上最大的内陆浮动光伏农场之一,并且由于该岛的可用土地稀缺而成为必需。

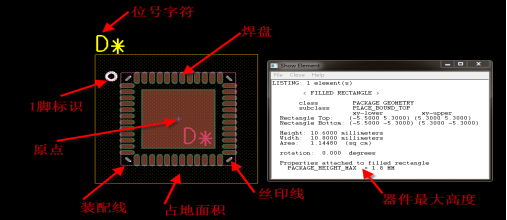

答:一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、管脚编号(Pin Number)、管脚间距、管脚跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符、装配字符、1脚标识、安装标识、占地面积、器件高度。在Cadence Allegro软件中,以下元素是必须要有的:焊盘(包括阻焊、孔径等内容)、丝印线、装配线、位号字符、1脚标识、安装标识、占地面积、器件最大高度、极

答:一般来说,针对于Allegro软件,完整的封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、花焊盘、反焊盘、Pin_number、Pin间距、Pin跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符,装配字符、1脚标识、安装标识、占地面积、器件高度等。其中,必须注意的是,下面几项是必须包含的:Ø 焊盘(包括阻焊、孔径等内容);Ø 丝印;Ø 装配线;Ø 位号字符;Ø&

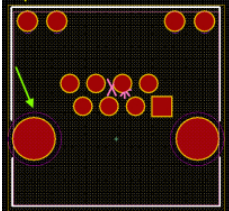

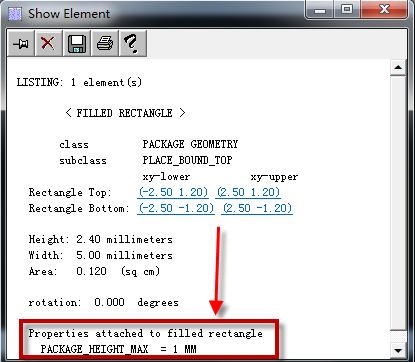

答:在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。第一步,打开一个PCB封装,将Package Geometry-Place_Bound_top层显示出来,如图4-70所示, 图4-70 显示元器件占地面积示意图第二步,点击Setup-Areas-Package Height选项,如图4-71所示

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)

答:一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、管脚编号(Pin Number)、管脚间距、管脚跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符、装配字符、1脚标识、安装标识、占地面积、器件高度。

在印刷电路板设计中,设置电路板轮廓后,将零件(占地面积)调用到工作区。然后将零件重新放置到正确的位置,并在完成后进行接线。组件放置是这项工作的第一步,对于之后的平滑布线工作是非常重要的工作。如果在接线工作期间模块不足,则必须移动零件,并且必须剥落完成的接线图并重新开始。除了在零件放置期间必须放置许多

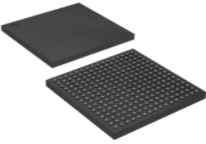

一、5M1270ZF256I5N IC CPLD 980MC 6.2NS 256FBGA说明:与其他cpld相比,MAX V系列低成本和低功耗cpld提供更大的密度和每占地面积的I/ o。MAX V器件的密度从40到2210个逻辑元件(32

概述MAX V系列低成本和低功耗CPLD提供更大的密度和每占地面积的I/O。MAX V器件的密度从40到2210个逻辑元件(32到1700个等效宏单元)和多达271个I/O,为I/O扩展、总线和协议桥接、电源监控和控制、FPGA配置和模拟I

扫码关注

扫码关注