人气阅读

一文说清反激电源的连续与断续模式

1

华为Mate 70来了,国产半导体迎来机会!

2

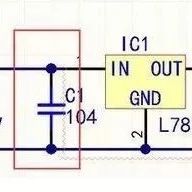

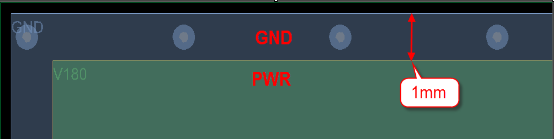

大电流开关电源的接地如何设计?

3

Linux中级技巧:如何在Linux上设置环境变量?

4

晶圆键合技术

5

What's the difference between Maxon WiFi6 4x4 M.2 industrial Wireless Module with QCN9074 & QCN9024?

6

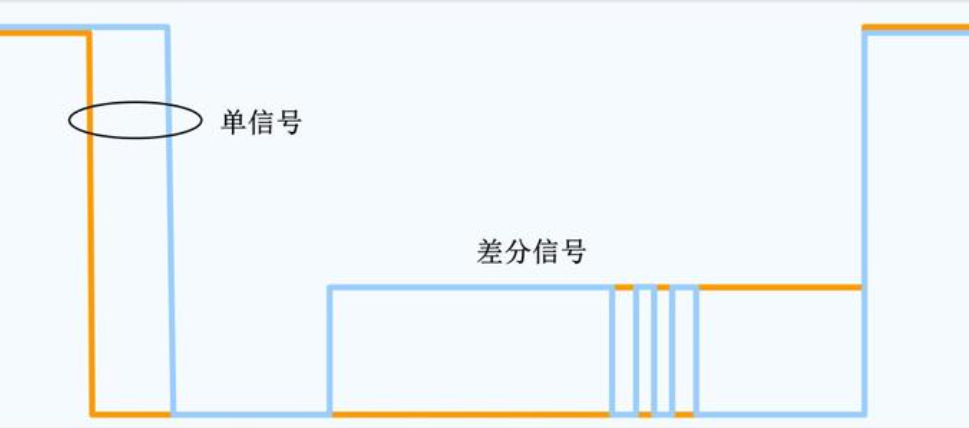

传感器检测中的八大抗干扰技术解析

7

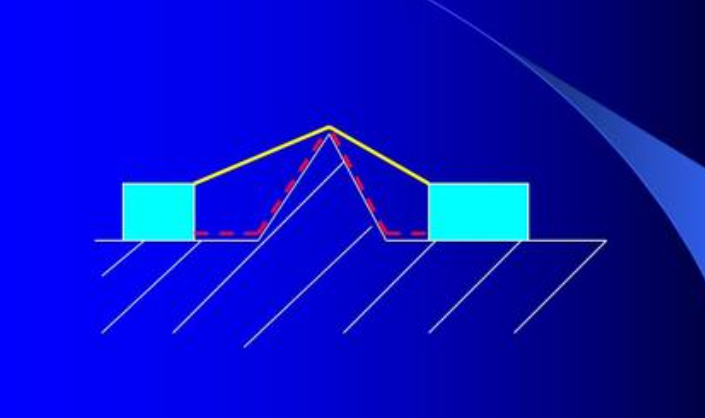

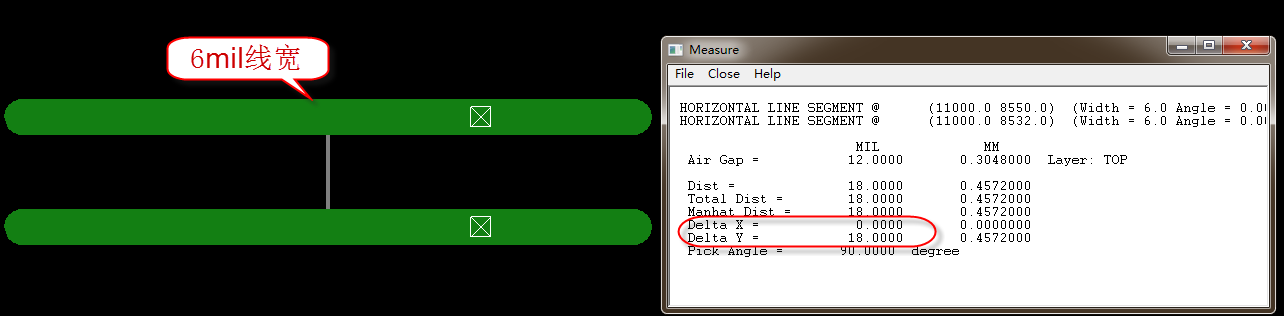

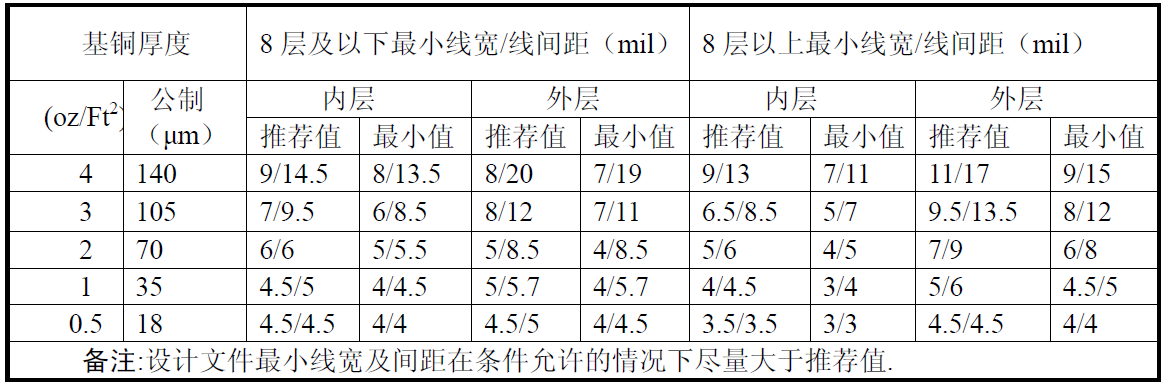

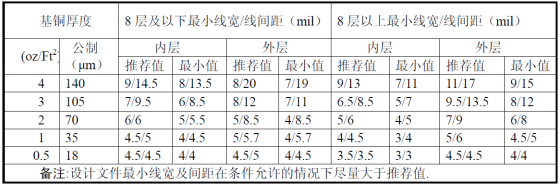

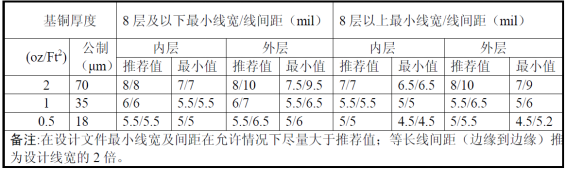

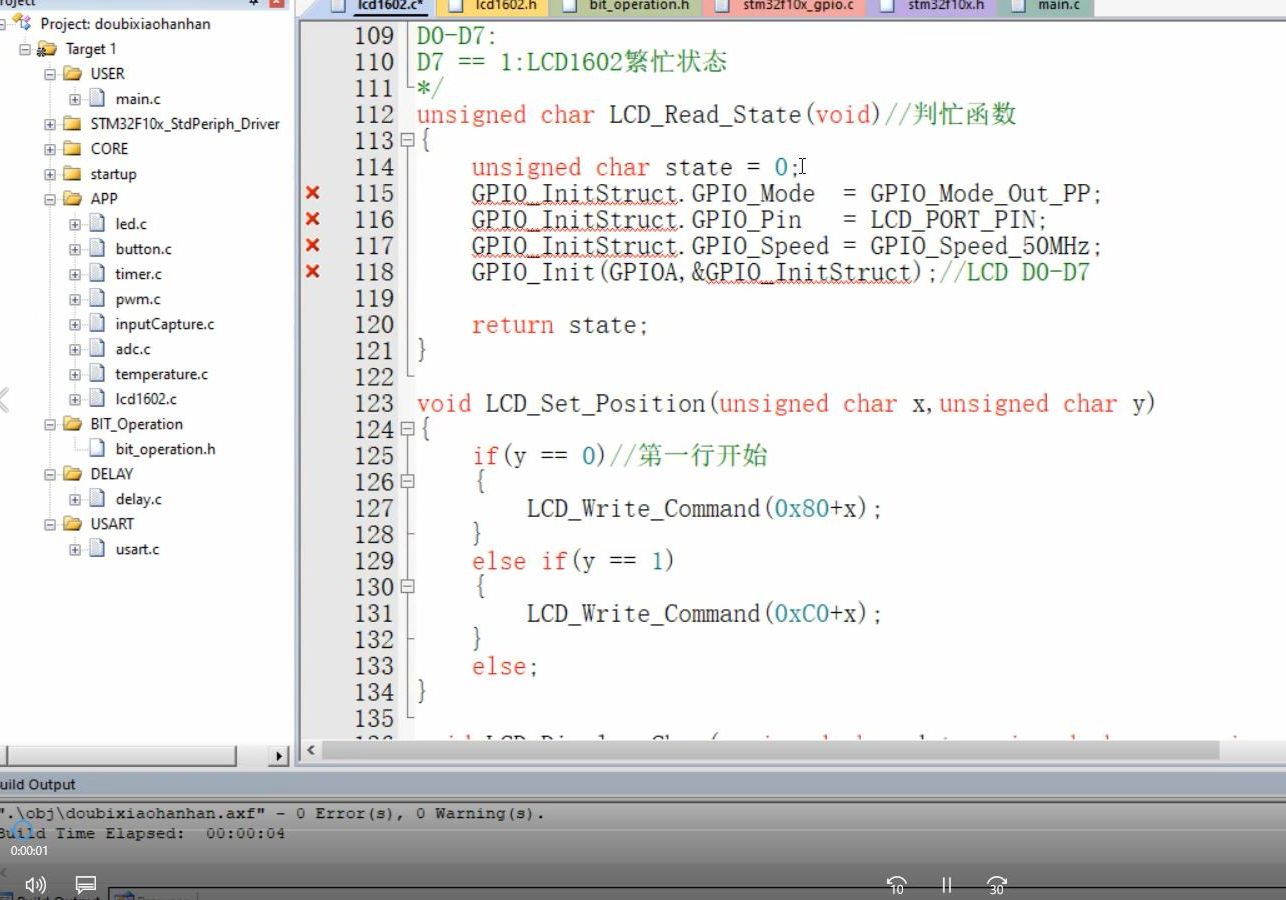

老工程师荐读!PCB设计避坑指南(图文结合、视频演示)

8

太阳能电池的使用寿命有多长?该如何注意使用?

9

面试官:宕机了,Redis 如何避免数据丢失?

EDA设计

硬件技术

EDA仿真

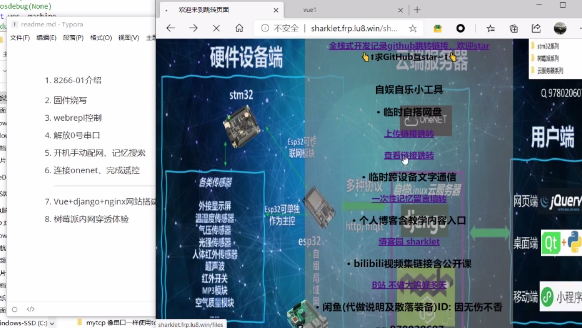

嵌入式

IC设计

人工智能

考试认证

结构设计

其他

扫码关注

扫码关注