- 全部

- 默认排序

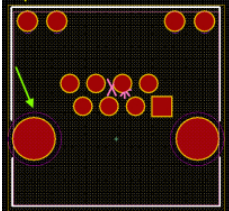

用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_TOP层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。

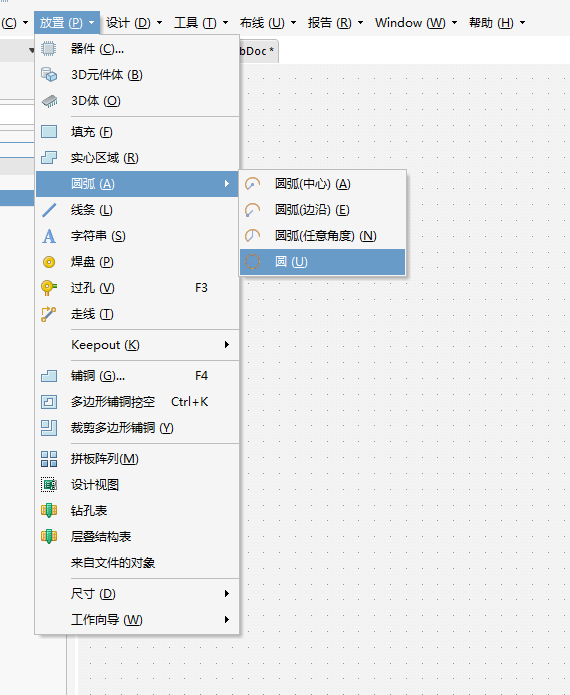

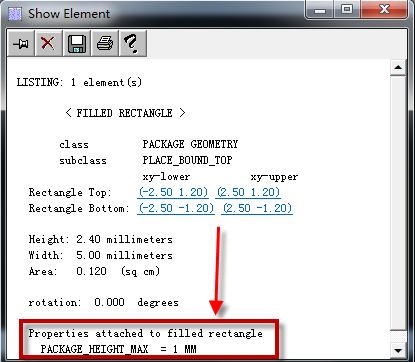

答:在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。第一步,打开一个PCB封装,将Package Geometry-Place_Bound_TOP层显示出来,如图4-70所示, 图4-70 显示元器件占地面积示意图第二步,点击Setup-Areas-Package Height选项,如图4-71所示

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_TOP层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)

答:我们在Allegro软件中,新建的PCB文件,默认的模板都是只有两层,TOP层跟BOTTOM层,但是我们在实际的电子设计中,是有多层板的,比如4层、6层、8层,我们在PCB中如何添加层叠呢,具体的操作步骤如下所示:

答:在做封装时,一般会添加2种类型的器件编号,即装配字符和丝印字符,这2种类型的器件编号分别是添加到Ref Des-Assembly_TOP层、Ref Des-Silkscreen_TOP层。

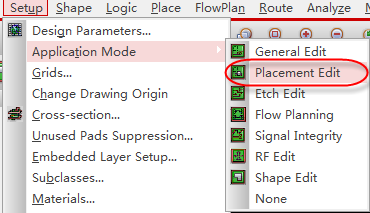

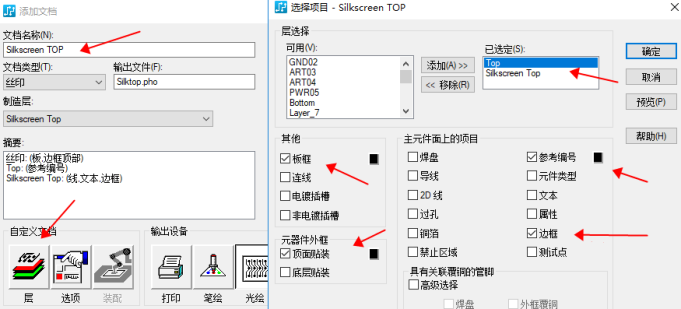

丝印层的设置与电气层设置步骤大致相同,主要区分内容在层对应的选项,注意丝印包含TOP、BOTTOM层,需要设置2个文件。TOP层设置如图5-172、5-173所示。图5-172 丝印层TOP设置图5-173 丝印层Silkscreen TO

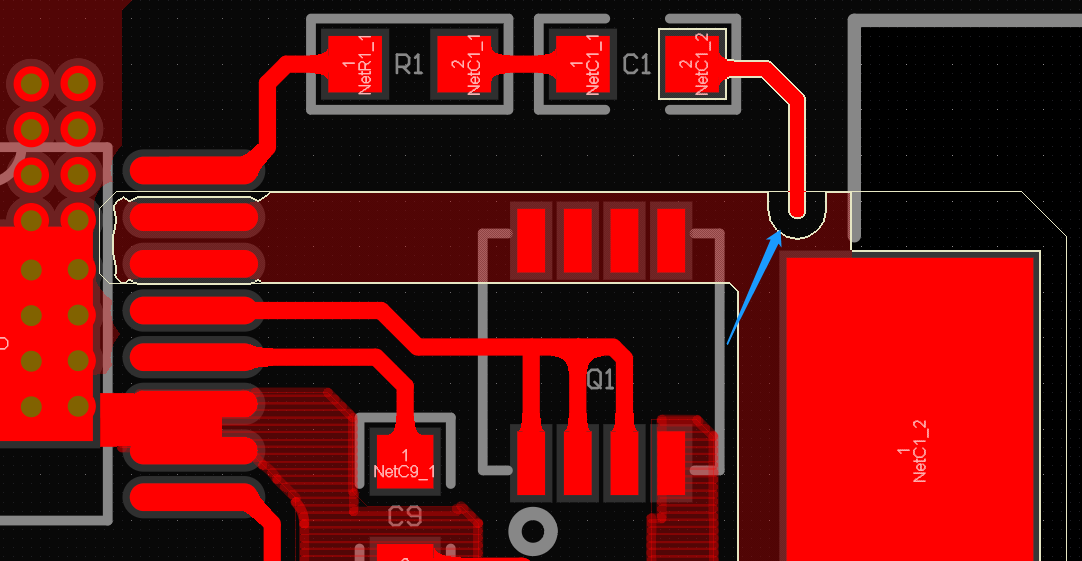

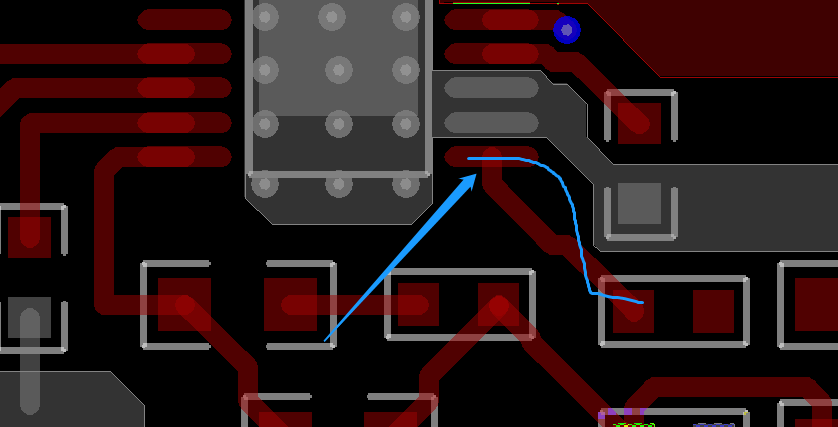

相同网络的铜皮和走线没有连接在一起,后期自己调整一下铜皮属性重新铺铜2.走线未从焊盘中心出线,存在开路3.存在短路4.贴片器件焊盘需要放置TOP层,后期自己重新处理一下5.电感所在层的内部需要挖空处理6.pcb上存在多处DRC,后期自己更改

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.走线尽量不要走直角,建议45度3.铺铜注意层的问题,器件在TOP层,铜皮在bottom层4.模块复用后铜皮变静态铜皮,需要自己调整成动态铜皮,后期自己处理一下5.采用单点接

扫码关注

扫码关注