要想成为一个优秀的电子工程师,熟练掌握IC设计是基本技能之一,IC设计可分为多个环节,其中之一是静态时序分析,要想做好IC设计的静态时序分析,该如何做?

首先,静态时序分析是检查IC系统时序是否满足要求的主要方法,静态时序分析工具根据往表中各节点的负载,利用综合库中各单元的延时查找表,计算出单元延时及连线延时,从而可以判断在该设计中寄存器之间最长路径上的延时有多少,是否满足最大时钟约束。若不满足,则静态时序分析工具将给出setup违例。

静态时序工具还会分析hold违例,hold违例跟时钟树有关。

在深亚微米设计中,串扰(crosstalk)、IP drop等都将影响芯片的时序甚至功能,这些属于信号完整性的范畴,OCV(On Chip Variation、片上偏差)效应也越来越显著,现在的静态时序工具中,也支持对这些现象的分析。

静态时序分析可分为两类:逻辑及分析和电路级分析,前者针对用标准单元构成的网表,后者主要针对模拟电路和混合电路。

在进行逻辑级静态时序分析时,需要输入如下内容:网表、综合库、时序约束(时钟、输入延时、输出延时等)。

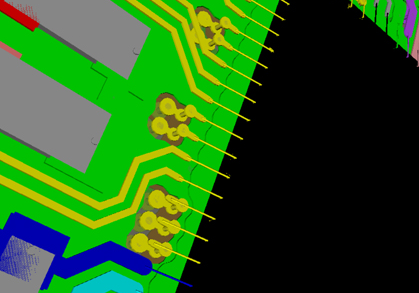

如果是对布局布线之后的网表进行静态时序分析,还需要输入寄生参数文件(该文件包含了由版图提取的网表中各节点的寄生电容和寄生电阻等信息)。

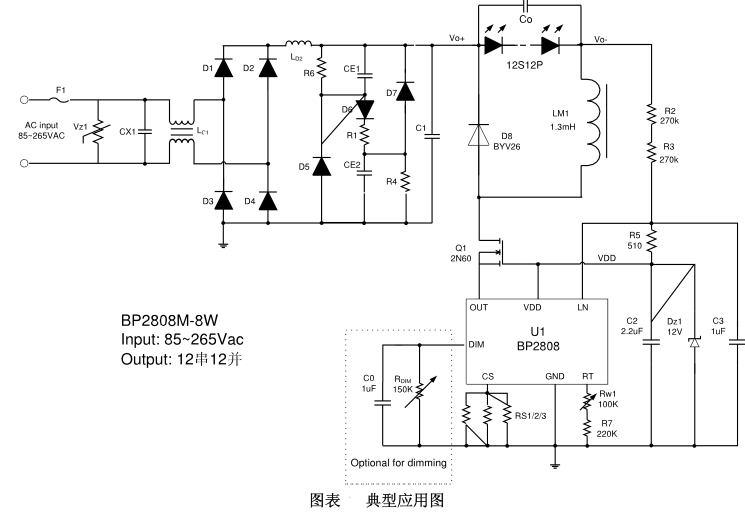

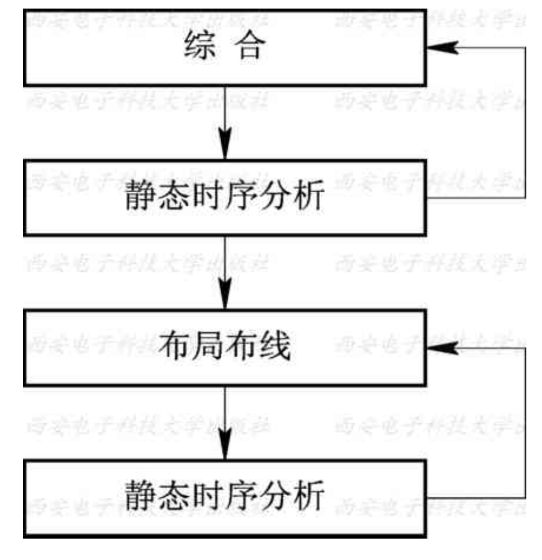

如图所示,改图给出了逻辑及静态时序分析的步骤,通常来说,在网表综合完成后,需进行静态时序分析,在布局布线完成后,在进行以此静态时序分析。当然在布局布线尚未最终完成时,也可进行静态时序分析。

而电路级的静态时序分析工具(如:PathMill)是可以分析一个芯片的I/O是否满足时序要求。

扫码关注

扫码关注