FPGA是一种功能强大的可编程逻辑器件,广泛应用在数字电路设计、信号处理、无线通信等多领域,自然也就成为电子工程师的关键技能之一,若是不合理使用FPGA,极有可能导致FPGA设计不稳定、延迟大、时序崩溃等问题,所以下面将聊聊FPGA设计中的常见问题及设计技巧。

1、时序分析问题

①是时序分析是基于FPGA设计过程中的一个关键环节,它涉及到时钟频率、时序路径等方面。时序分析不足可能导致设计不稳定、延迟大、时序崩溃等问题。为了解决这些问题,设计师可以采用以下方法:

①优化时序路径:使用更快的器件、减少延迟、使用更好的布局布线方法等。

②使用高精度时钟:使用高精度时钟可以减小时钟抖动和时钟偏移,提高时序分析的准确性。

③使用静态时序分析工具:使用静态时序分析工具可以检查和优化设计中的时序路径,避免时序问题。

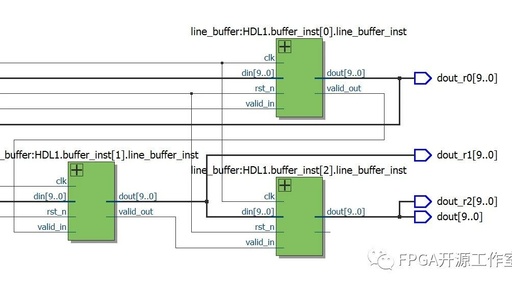

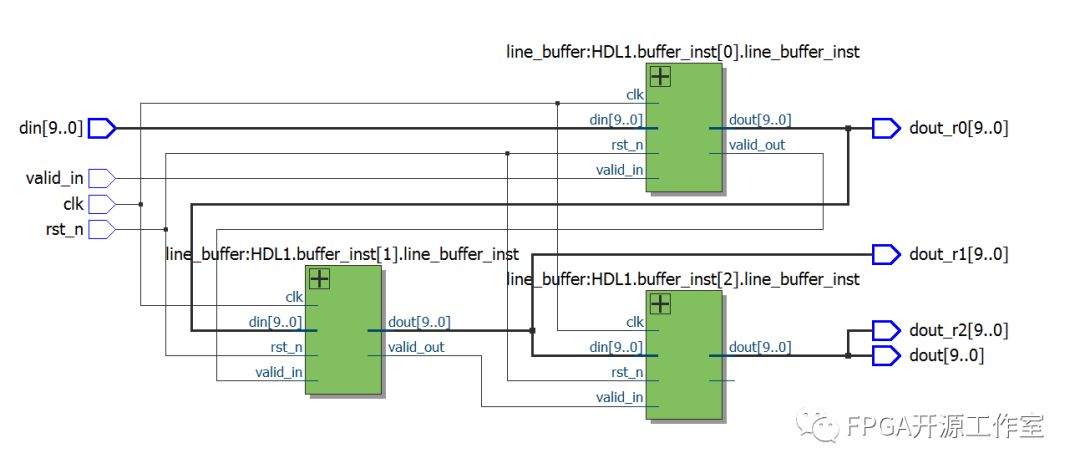

2、资源利用问题

在FPGA设计中,资源利用是一个重要问题。由于FPGA资源有限,设计师需要尽可能地优化资源利用,以便实现更复杂的设计。为了解决资源利用问题,设计师可以采用以下方法:

①使用多工程设计:多工程设计可以将设计模块分解为多个模块,从而减少资源使用,提高设计的可维护性和可重用性。

②使用优化的布局布线方法:使用优化的布局布线方法可以最大限度地减少资源使用,提高设计的性能。

③使用高级合成工具:高级合成工具可以自动优化设计,减少资源使用,并提高设计的性能和可重用性。

3、时钟分频问题

时钟分频是FPGA设计中常见问题,时钟分频可实现不同频率的时钟信号,从而满足不同的时序要求,为了解决时钟分频问题,工程师可采用以下方法:

①使用PLL:使用PLL可生成多种频率的时钟信号,从而实现时钟分频;

②使用逻辑分频器:逻辑分频器可将时钟信号分频为任意频率,从而实现时钟分频;

③使用时钟控制器:时钟控制器可以控制时钟信号的频率和相位,从而实现时钟分频。

扫码关注

扫码关注