小伙伴们在学习FPGA时,最怕遇到同步时序电路设计,然而作为FPGA主要电路,同步时序电路试验频率居高不下,所以今天讲讲一些技巧,如如何实现同步时序电路的延时?如何实现RAM/ROM/CAM?

1、FPGA设计中如何实现同步时序电路的延时?

首先说说异步电路的延时实现:异步电路一半是通过加buffer、两级与非门等来实现延时(我还没用过所以也不是很清楚),但这是不适合同步电路实现延时的。在同步电路中,对于比较大的和特殊要求的延时,一半通过高速时钟产生计数器,通过计数器来控制延时;对于比较小的延时,可以通过触发器打一拍,不过这样只能延迟一个时钟周期。

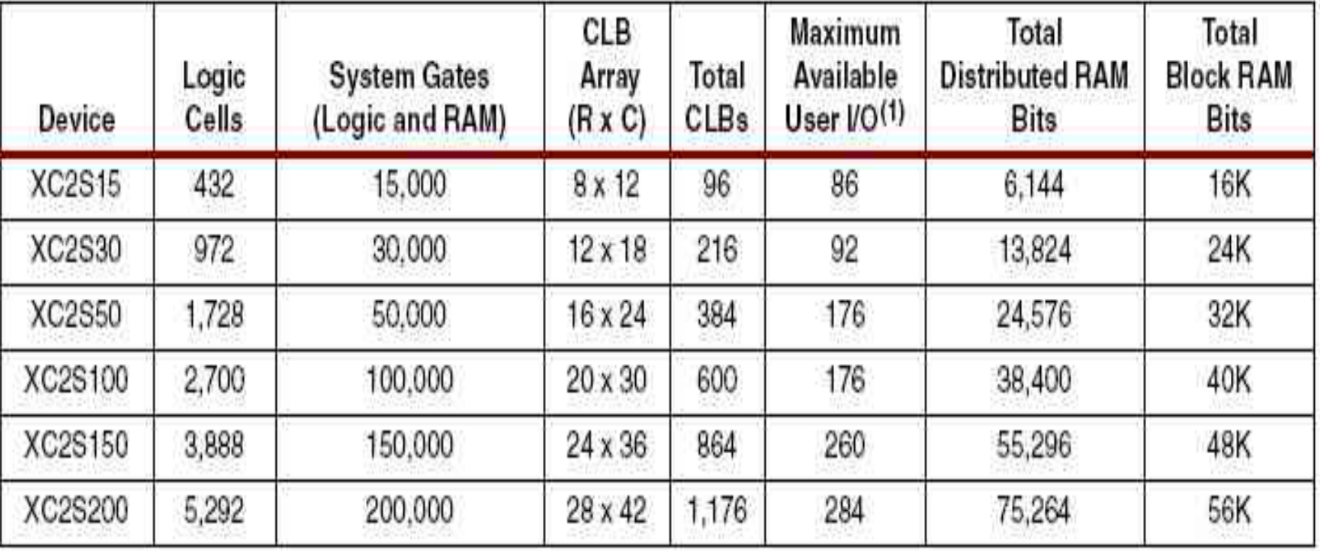

2、FPGA中可以综合实现为RAM/ROM/CAM的三种资源及其注意事项?

三种资源:BLOCK RAM,触发器(FF),查找表(LUT);

注意事项:

①在生成RAM等存储单元时,应该首选BLOCK RAM资源;其原因有二:第一使用BLOCK RAM等资源,可以节约更多的FF和4-LUT等底层可编程单元。使用BLOCK RAM可以说是“不用白不用”,是最大程度发挥器件效能,节约成本的一种体现;第二BLOCKRAM是一种可以配置的硬件结构,其可靠性和速度与用LUT和REGISTER构建的存储器更有优势。

②弄清FPGA的硬件结构,合理使用BLOCKRAM资源;

③分析BLOCK RAM容量,高效使用BLOCK RAM资源;

④分布式RAM资源(DISTRIBUTE RAM)。

扫码关注

扫码关注