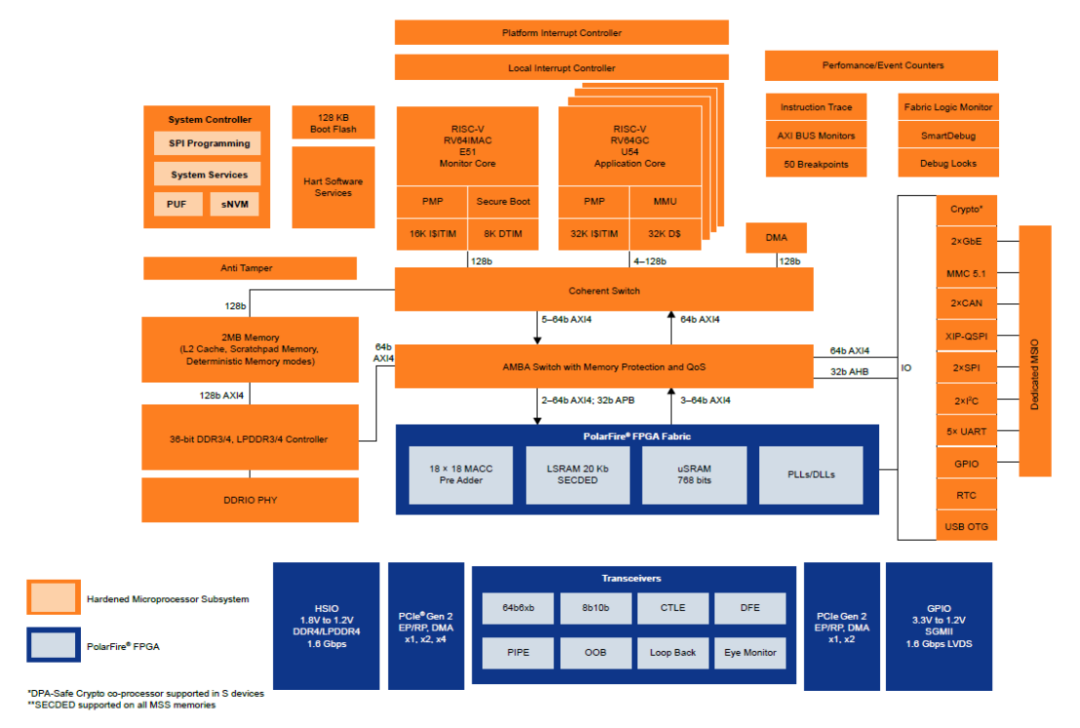

随着微电子技术的不断发展,FPGA和ASIC的性能也变得越来越优越,也开始被广泛应用在电子电路与系统的开发和调试阶段,这也促使了FPGA的配置电路模式发展。

FPGA配置方式灵活多样,根据芯片是否能够主动加载配置数据分为主模式、从模式及JTAG模式。典型的主模式都是加载片外非易失(断电不丢数据)性存储器中的配置比特流,配置所需的时钟信号(称为CCLK)由FPGA内部产生,且FPGA控制整个配置过程。从模式需要外部的主智能终端(如处理器、微控制器或者DSP等)将数据下载到FPGA中,其最大的优点就是FPGA的配置数据可以放在系统的任何存储部位,包括:Flash、硬盘、网络,甚至在其余处理器的运行代码中。JTAG模式为调试模式,可将PC中的比特文件流下载到FPGA中,断电即丢失。此外,目前赛灵思还有基于Internet 的、成熟的可重构逻辑技术 System ACE解决方案。

①主模式

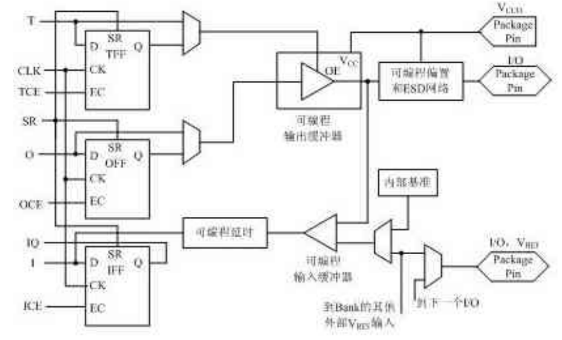

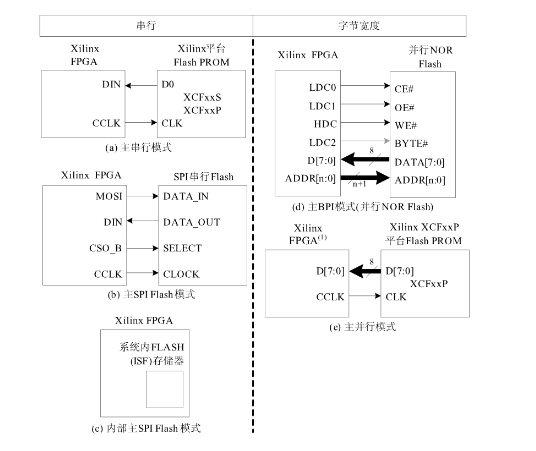

在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射﹔主模式根据比特流的位宽又可以分为:串行模式(单比特流)和并行模式(字节宽度比特流)两大类。如:主串行模式、主SPI Flash串行模式、内部主SPI Flash串行模式、主BPI并行模式以及主并行模式,如图所示。

②从模式

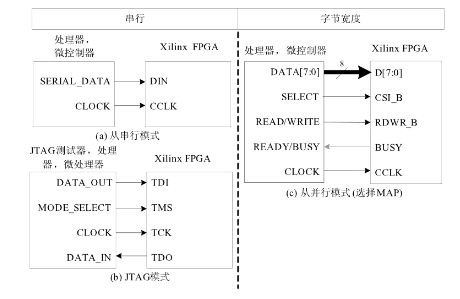

在从模式下,FPGA作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类,其概要说明如图所示。

③JTAG模式

在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

扫码关注

扫码关注