不知道大家有没有这样的经历,好好设计电路,但测试时候却发现里面电磁辐射超标,最终被打道回府,重做。遇到这样的情况很难受,所以为什么你的电路会电磁辐射超标呢?

1、PCB层数不足

原因:单层或双层PCB难以有效隔离电源层、地线层,导致公共阻抗噪声大,信号线辐射能力强。

解决方法:选用多层PCB,内层分别作为电源层、地线层,降低供电线路阻抗,抑制噪声,加大信号线与接地面间的分布电容。

2、走线阻抗高

原因:电源线、地线、印制板走线细长,高频阻抗大,易成为接收与发射骚扰的小天线。

解决方法:走线要短而粗,线条均匀,降低高频阻抗,加滤波电容进一步抑制骚扰。

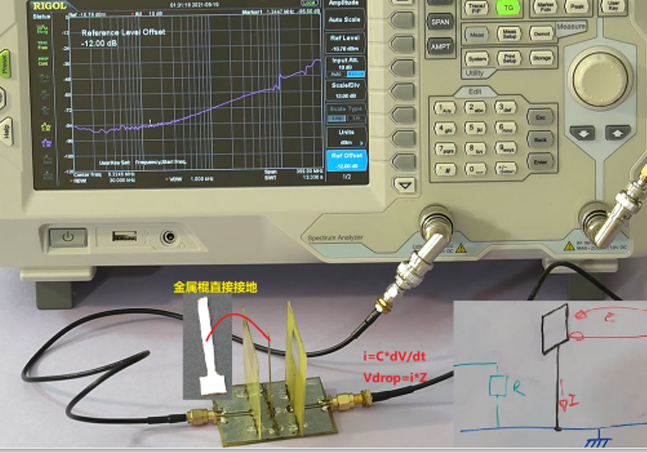

3、环路面积大

原因:电源线、地线及印制导线排列不当,信号线与回线之间形成的环路面积大,易产生辐射。

解决方法:优化走线布局,尽量做到短而直,减小环路面积。

4、信号耦合强

原因:电路元件和信号通路布局不合理,无用信号相互耦合,增强辐射。

解决方法:重新布局,最大限度减少无用信号的相互耦合,保持信号通路清晰。

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注