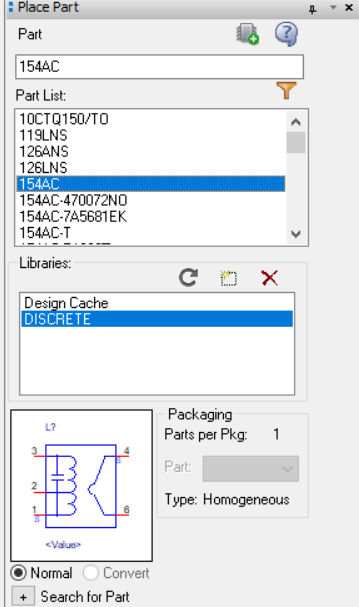

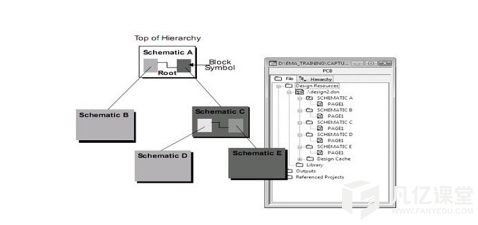

答:层次式电路设计(Hierarchical Design),通常是在设计比较复杂的电路和系统时采用的一种自上而下的电路设计方法,即首先在一张图纸上设计电路总体框图,然后再在另外层次图纸上设计每个框图代表的子电路结构,下一层次中还可以包括框图,按层次关系将子电路框图逐级细分,直到最低层次上为具体电路图,不再包括子电路框图,如图3-107所示,是一个大概的层次式原理图的框架。

图3-107 层次式原理图示意图

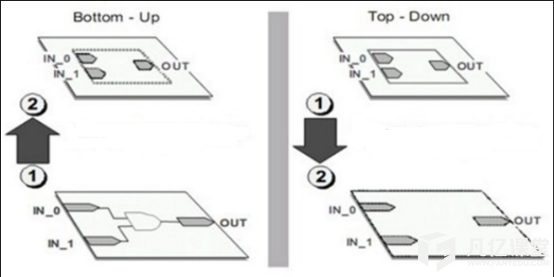

层次式原理图一种先进的原理图设计方法,使用符号代表功能,并且能够重复的调用,(同FPGA的verilog 语言一样)。设计的两种方法:自下而上(Bottom-Up)和自上而下(Top-Down),如图3-108所示:

图3-108 层次式原理图绘制方式示意图

层次原理图结构分明,模块化清晰,可以重复调用,它的优点有如下几个:

Ø 分工,将一个复杂的电路设计分为几个部分,分配给几个工程技术人员同时进行设计;

Ø 模块化,让具有不同特长的设计人员负责不同部分的设计;

Ø 设备限制,打印输出设备不支持幅面过大的电路图页面;

Ø 自上而下的设计策略,目前该策略已成为电路和系统设计的主流。

扫码关注

扫码关注