【摘要】

PECL/CML/LVDS这几种高速差分接口是我们工程中常用接口,本文将从接口起源、输出内部结构、输入内部接口三方面分别阐述各自原理。下一篇文章将重点阐述这几种高速接口之间的互联硬件设计。

1. 差分信号接口介绍1.1 PECL 接口

PEL 是有 ECL 标准发展而来,在 PECL 电路中省去了负电源,较 ECL 电路更方便使用。PECL 信号的摆幅相对 ECL 要小,这使得该逻辑更适合于高速数据的串性或并行连接。PECL 标准最初有 MOTOROLA 公司提出,经过很长一段时间才在电子工业界推广开。

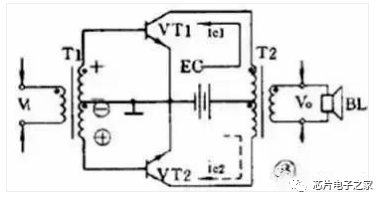

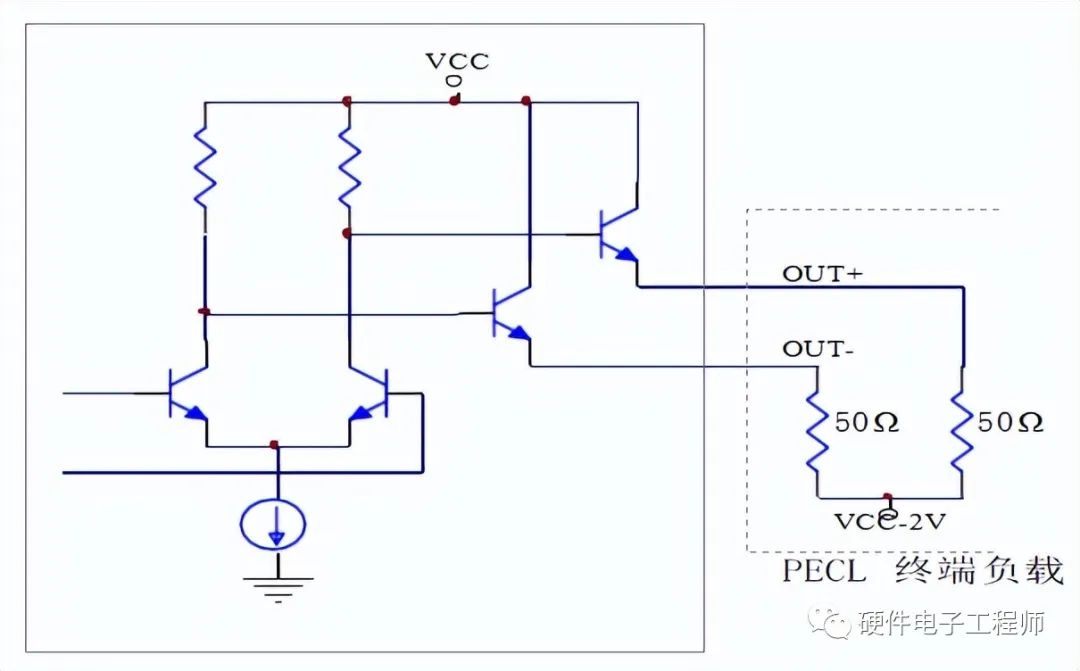

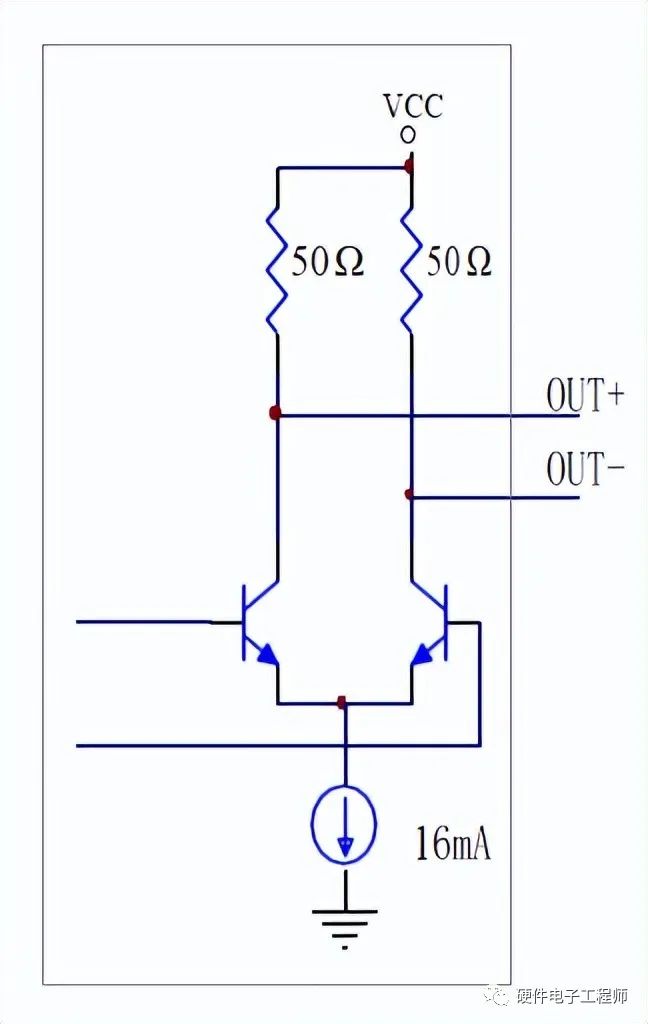

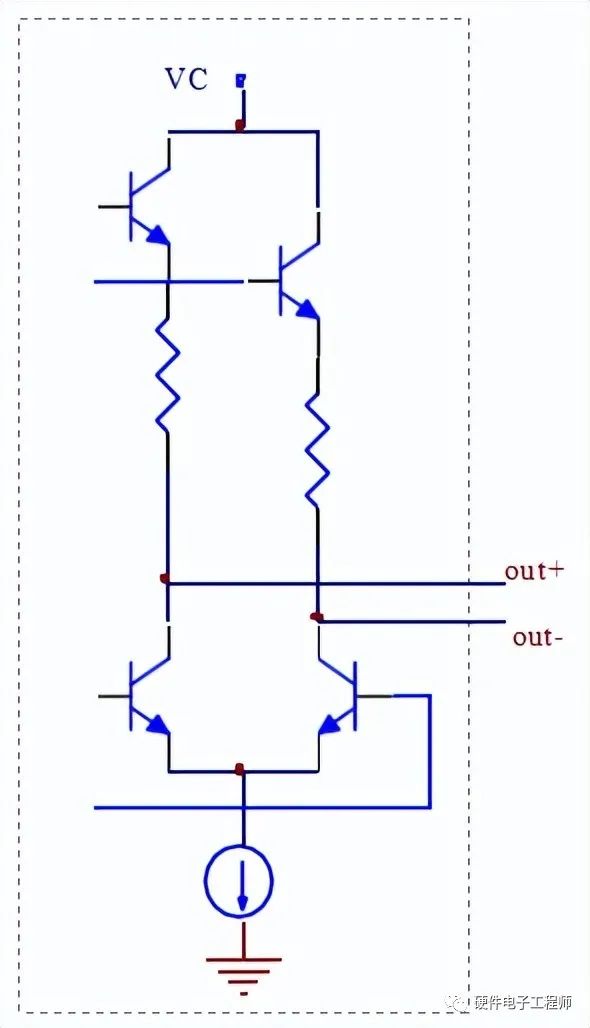

(1)PECL 接口输出结构

PECL 电路的输出结构如图 1 所示,包含一个差分对和一对射随器。输出射随器工作在正电源范围内,其电流始终存在,这样有利于提高开关速度。标准的输出负载是接 50Ω至 VCC-2V 的电平上,如图 1 中所示,在这种负载条件下,OUT 与 OUT-的静态电平典型值为 VCC-1.3V, OUT 与OUT-输出电流为 14mA。PECL 结构的输出阻抗很低,典型值为 4~ 5 Ω,这表明它有很强的驱动能力,但当负载与 PECL 的输出端之间有一段传输线时,低的阻抗造成的失配将导致信号时域波形的振铃现象。

图1. PECL 输出结构

图1. PECL 输出结构

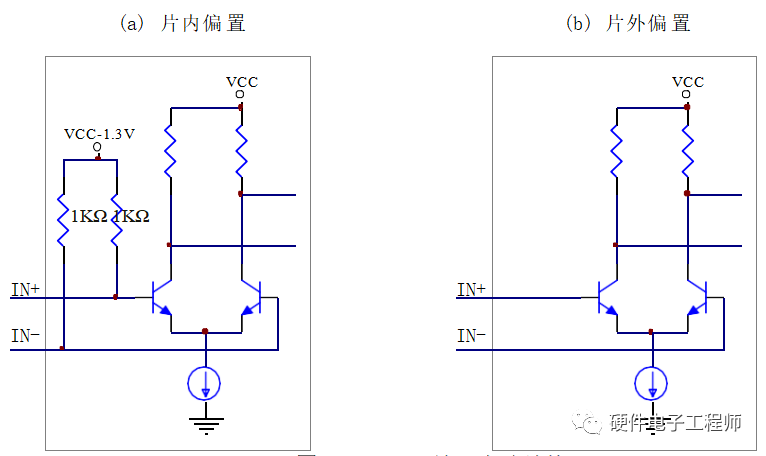

(2) PECL 接口输入结构

PECL 输入结构如图 2 所示,它是一个具有高输入阻抗的差分对。该差分对共模输入电压需偏置到 VCC-1.3V,这样允许的输入信号电平动态最大。MAXIM 公司的 PECL 接口有两种形式的输入结构,一种是在芯片上已加有偏置电路,如 MAX3867、MAX3675,另一种则需要外加直流偏置。

图2. PECL 输入电路结构

图2. PECL 输入电路结构

表一中给出了 MAXIM 公司 PECL 接口输入输出的具体电气指标。

表格1. PECL 输入输出指标

参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

输出高电平 | Ta=0℃~85℃ | Vcc-1.025 | Vcc-0.88 | V | |

Ta=-40℃ | Vcc-1.085 | Vcc-0.88 | V | ||

输出低电平 | Ta=0℃~85℃ | Vcc-1.81 | Vcc-1.62 | V | |

Ta=-40℃ | Vcc-1.83 | Vcc-1.55 | V | ||

输入高电平 | Vcc-1.16 | Vcc-0.88 | V | ||

输入低电平 | Vcc-1.81 | Vcc-1.48 | V |

在5V 和3.3V 供电系统中,PECL 接口均适用,3.3V 供电系统中的PECL 常被称作低压PECL,简写为 LVPECL。

在使用 PECL 电路时要注意加电源去耦电路,以免受噪声的干扰,同时输出采用交流还是直流耦合对负载网络的形式将会提出不同的需求。

1.2 CML 接口

CML 是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,也更适合于在高的频段工作。它所提供的信号摆幅较小,从而功耗更低。

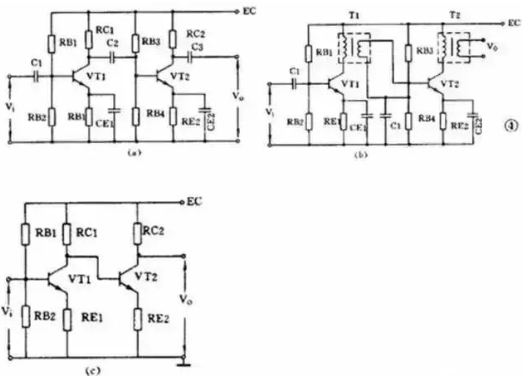

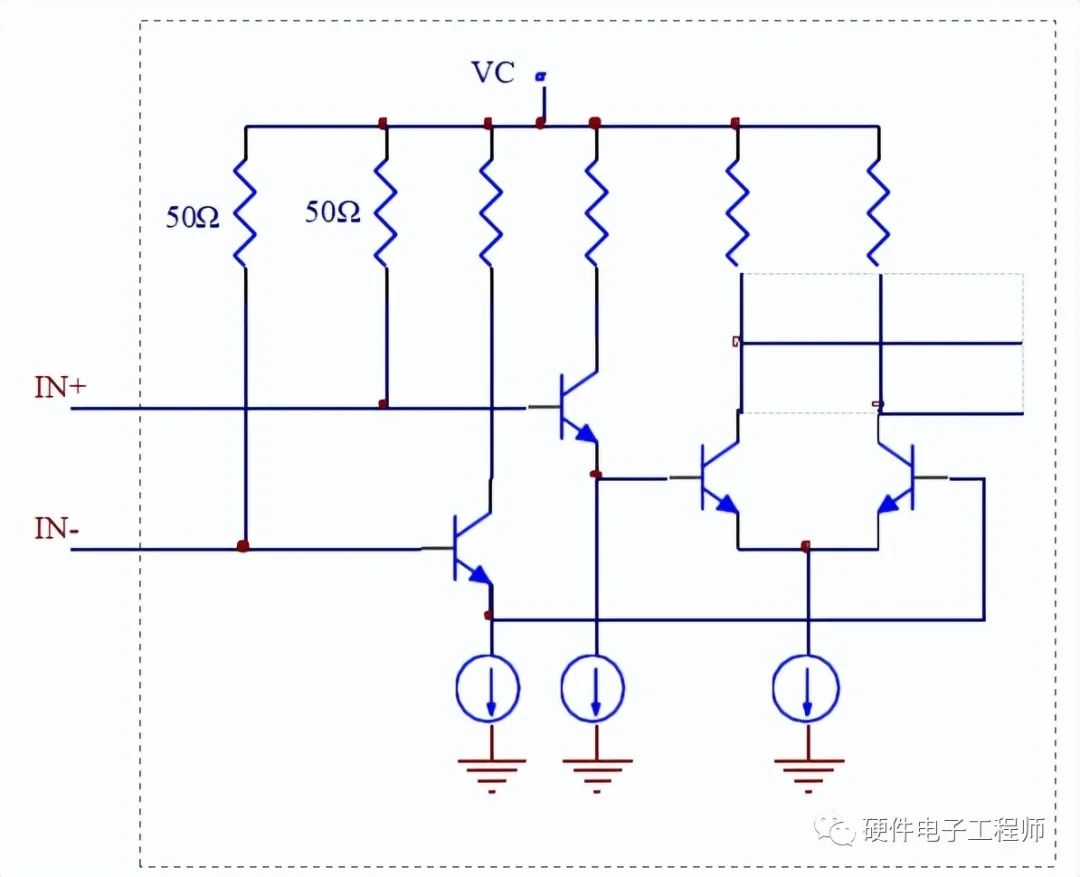

(1)CML 接口输出结构

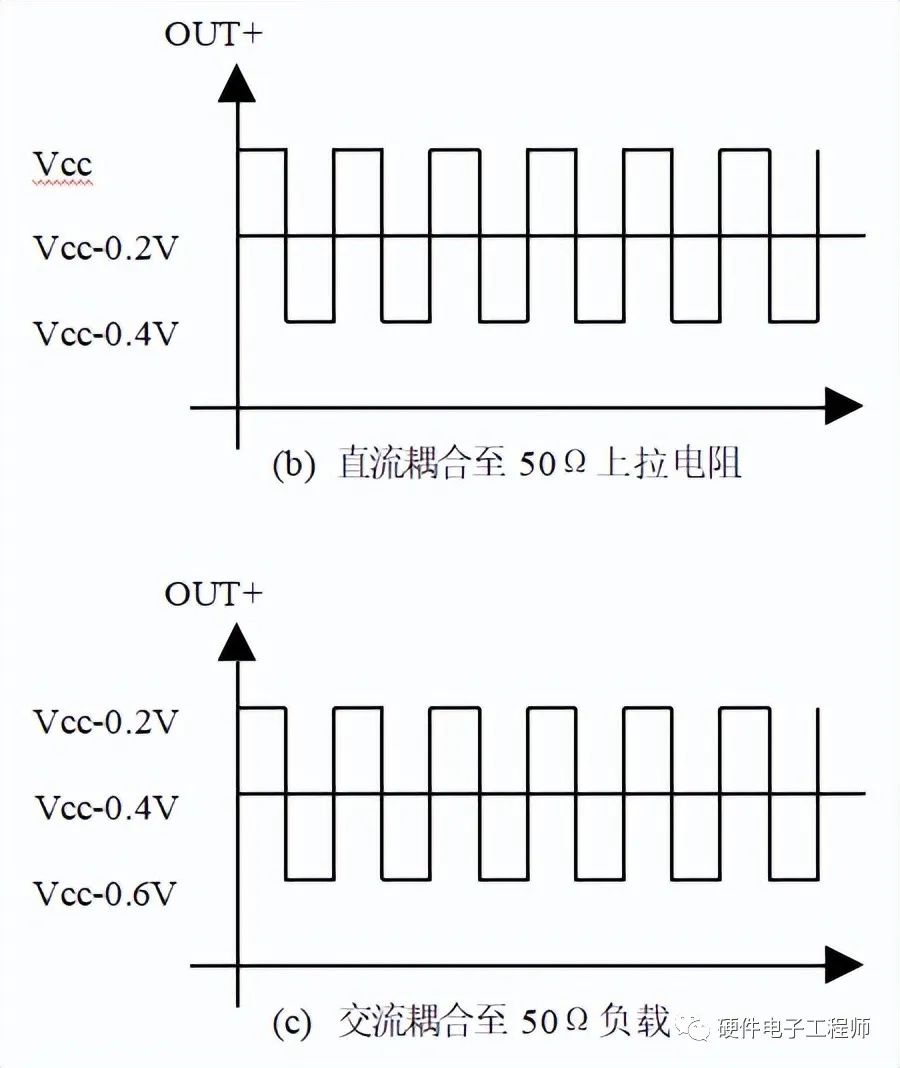

CML 接口的输出电路形式是一个差分对,该差分对的集电极电阻为 50Ω,如图 3 中所示, 输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为 16mA,假定 CML 输出负载为一 50Ω上拉电阻,则单端 CML 输出信号的摆幅为Vcc~Vcc-0.4V。在这种情况下,差分输出信号摆幅为 800mV,共模电压为 Vcc-0.2V。若 CML

输出采用交流耦合至 50Ω负载,这时的直流阻抗有集电极电阻决定,为 50Ω,CML 输出共模电压变为 Vcc-0.4V,差分信号摆幅仍为 800mV。在交流和直流耦合情况下输出波形见图 4。

图3. CML 输出结构

图3. CML 输出结构

图4. CML 在不同负载时的输出波形

图4. CML 在不同负载时的输出波形

(2)CML 接口输入结构

图5. CML 输入电路结构

图5. CML 输入电路结构

表二以 MAX3831、MAX3832 为例列出了 CML 器件的输入输出技术参数

表格2. CML 输入和输出参数

参数 | 条件 | 最小 | 典型 | 最大 | 单位 |

差分输入电压 | 640 | 800 | 1000 | mV | |

输出共模电压 | Vcc-0.2 | V | |||

单端输入电压范围 | VIS | Vcc-0.6 | Vcc 0.2 | V | |

差分输入电压摆幅 | 400 | 1000 | MVp-p |

注:MAXIM 不同产品 CML 输入灵敏度不同,如 MAX3875、MAX3876。

1.3 LVDS 接口

LVDS 用于低压差分信号点到点的传输,该方式有三大优点,从而使得它更具有吸引力:

1) LVDS 传输的信号摆幅小,从而功耗低,一般差分线上电流不超过 4mA,负载阻抗为 100Ω。这一特征使它适合做并行数据传输。

2) LVDS 信号摆幅小,从而使得该结构可以在 2.4V 的低电压下工作。

3) LVDS 输入单端信号电压可以从 0V 到 2.4V 变化,单端信号摆幅为 400mV,这样允许输入共模电压从 0.2V 到 2.2V 范围内变化,也就是说 LVDS 允许收发两端地电势有±1V 的落差。

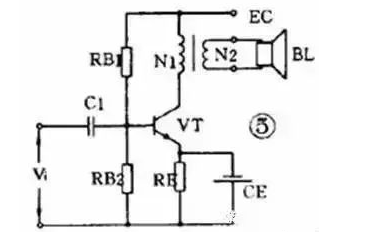

(1)LVDS 接口输出结构

MAXIM 公司 LVDS 输出结构在低功耗和速度方面做了优化,电路如图 6 所示。电路差分输出阻抗为 100Ω,表三列出了其他一些指标。

图6. LVDS 输出结构

图6. LVDS 输出结构

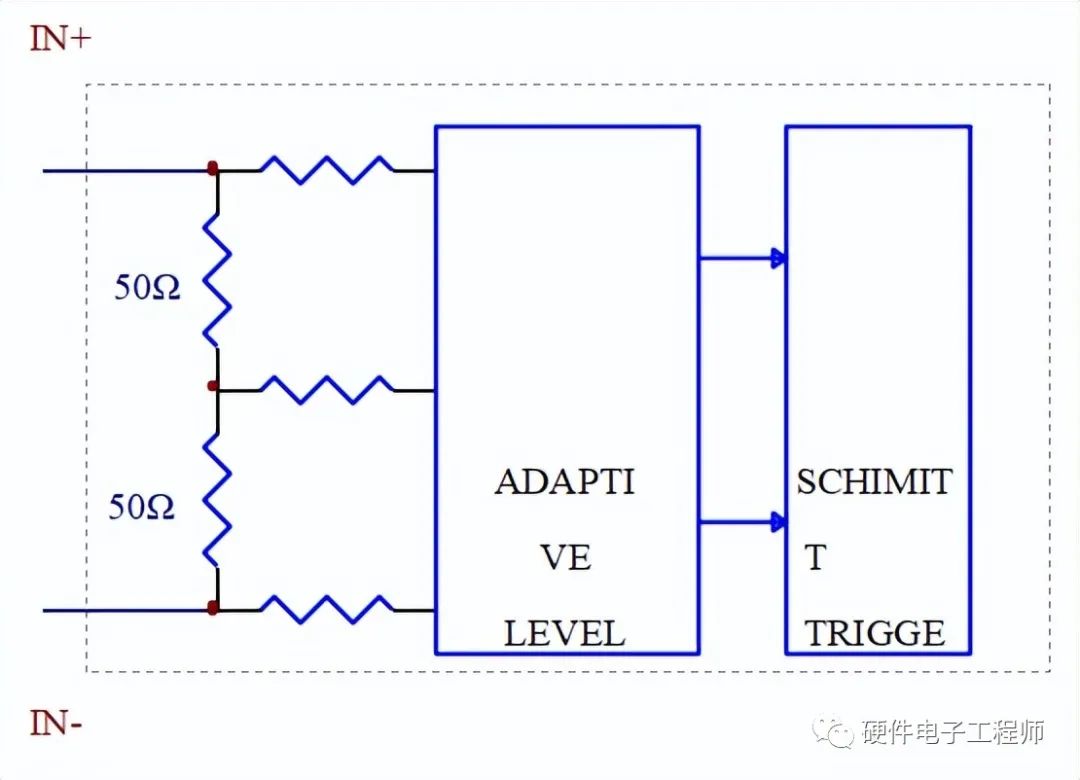

(2)LVDS 接口输入结构

LVDS 输入结构如图 7 所示,输入差分阻抗为 100Ω,为适应共模电压宽范围内的变化, 输入级还包括一个自动电平调整电路,该电路将共模电压调整为一固定值,该电路后面是一个 SCHMITT 触发器。SCHMITT 触发器为防止不稳定,设计有一定的回滞特性,SCHIMTT 后级是差分放大器。

图7. LVDS 输入结构

图7. LVDS 输入结构

表三总结了 MAXIM 公司 LVDS 输入与输出技术指标(MAX3831,MAX3832,MAX3880,MAX3890,MAX3885)

表格3. LVDS 输入与输出参数

参数 | 符号 | 条件 | 最小 | 典型 | 最大 | 单位 |

LVDS 输出高电压 | VOH | 1.475 | V | |||

LVDS 输出低电压 | VOL | 0.925 | V | |||

LVDS 输出差分电压 | |VOd| | 250 | 400 | mV | ||

LVDS 在不同状态时 输出差分电压波动 | Δ|VOd| | 25 | mV | |||

LVDS 输出电压偏移量 | 1.125 | 1.275 | V | |||

LVDS 在不同状态时 输出电压偏移量波动 | Δ|VOs| | 25 | mV | |||

LVDS 输出差分阻抗 | 80 | 120 | Ω | |||

LVDS 输出电流 | 两差分端相接 | 12 | mA | |||

差分单端到地短路 | 40 | mA | ||||

LVDS 输入单端电压范围 | Vi | 0 | 2.4 | V | ||

LVDS 输入差分信号灵敏度 | |Vid| | 100 | mV | |||

LVDS 输入共模电流 | VOS = 1.2V 时 | 350 | μA | |||

LVDS 回滞门限宽度 | 70 | mV | ||||

LVDS 输入差分阻抗 | Rin | 85 | 100 | 115 | Ω |

由于差分线信号变化连续,差分摆幅小,使之在传输速率的提高以及辐射发射的降低上,相对于传统的TTL以及CMOS等开关量信号有较大的优势,因此高速信号一般采用差分的方式进行传输。目前主要的差分信号电平有LVPECL,LVDS,CML等类型。下篇将对上述各种差分电平的互联电路设计,包括耦合方式、电路参数选择以及设计原则等,进行描述。

扫码关注

扫码关注