- 全部

- 默认排序

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

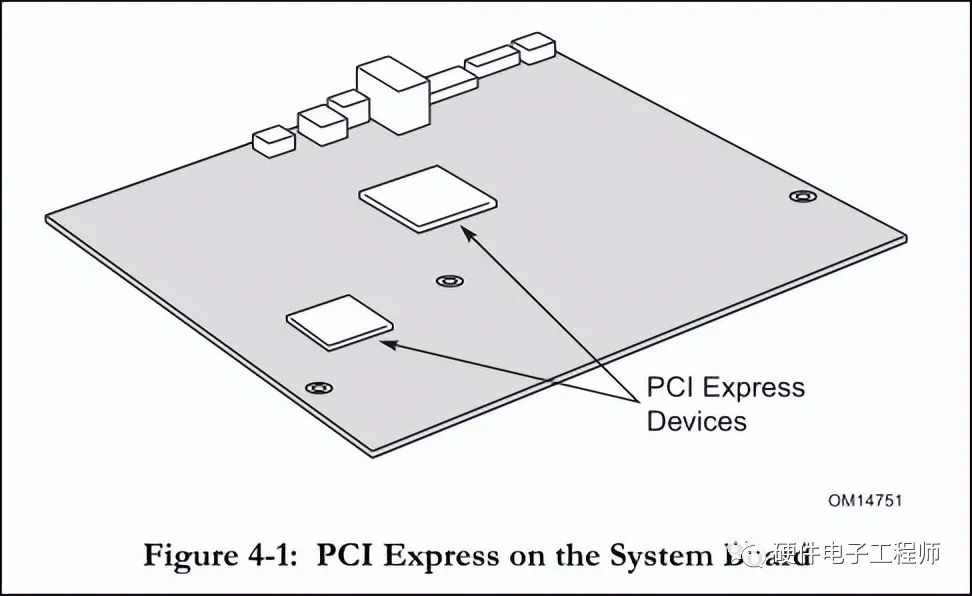

PCIe接口全称PCI Express,由PCI-SIG组织发布的用于替代PCI总路线的新一代高速串行总线与接口。PCIe接口版本经历PCIe1.0、PCIe2.0、PCIe3.0,目前主流应用的PCIe接口为PCIe2.0。PCIe作为高速差分串行接口用于替代PCI单端并行接口,在进行物理层信号测

【摘要】PECL/CML/LVDS这几种高速差分接口是我们工程中常用接口,本文将从接口起源、输出内部结构、输入内部接口三方面分别阐述各自原理。下一篇文章将重点阐述这几种高速接口之间的互联硬件设计。1. 差分信号接口介绍1.1 PECL 接口PEL 是有 ECL 标准发展而来,在 PECL 电路中省去

扫码关注

扫码关注