【课程详情】:

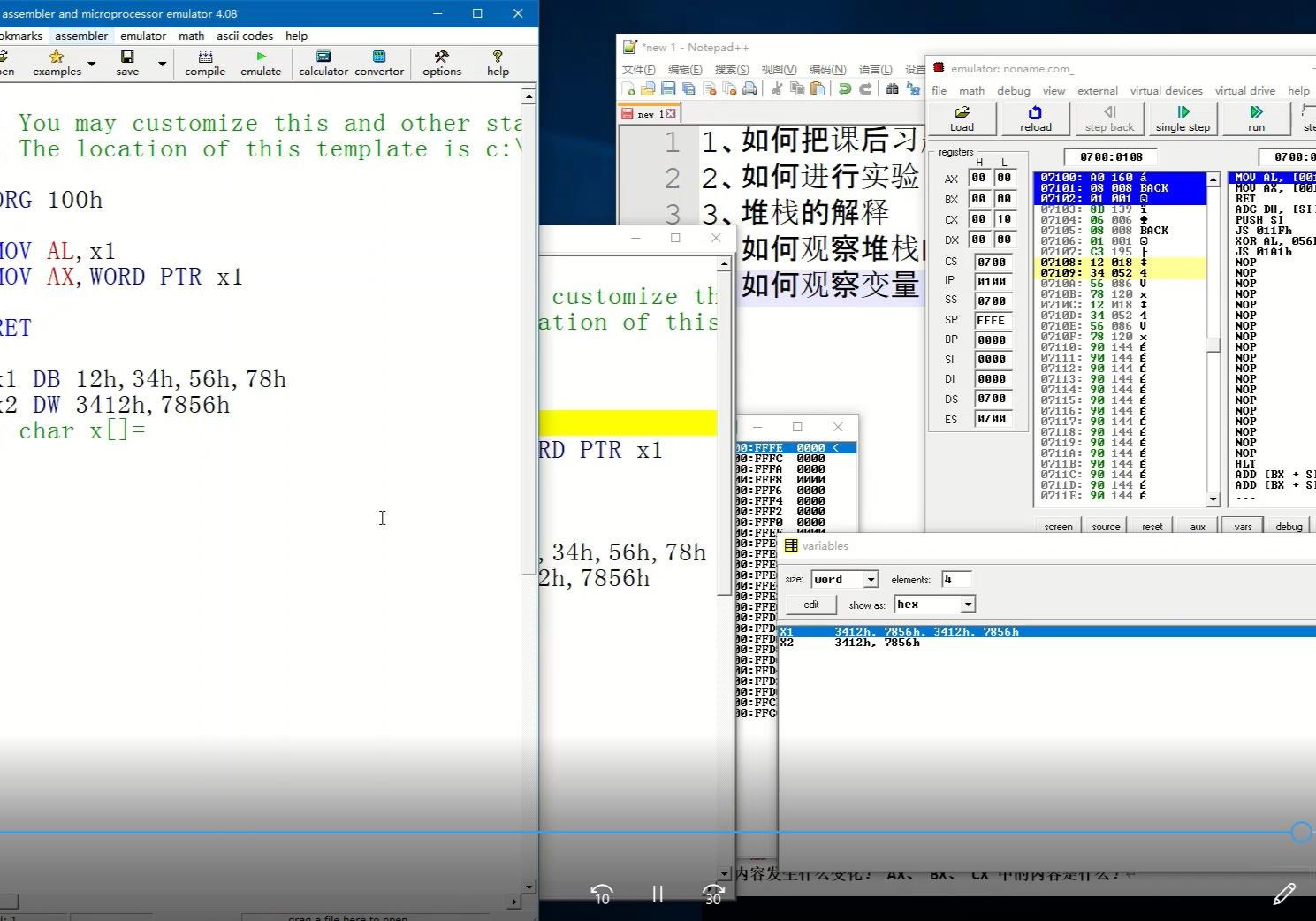

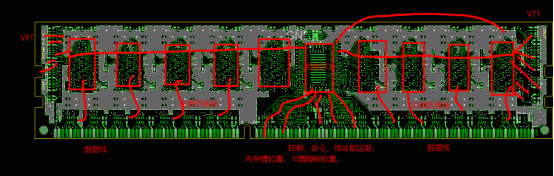

1、实例文件的互联提取方法,信号实例的文件设置;

解读文件,了解文件里面对各个信号的分配;

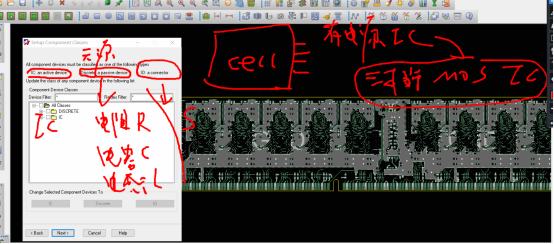

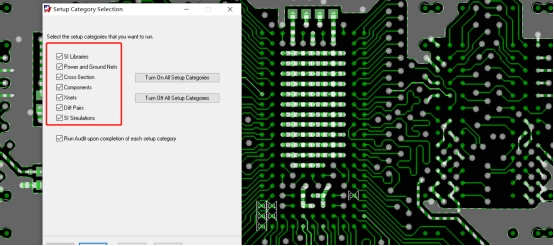

2、SI_Design_Setup信号完整性仿真设置与流程方法;

3、DDR3_DIMM2RX8内存条BRD文件实例信号完整性相关设置;

【1】仿真库的设置;【2】信号和电源的归类设置,电源要赋予电压;【3】层叠的设置;【4】原件模型设置,三种模型;【5】XNET网络设置;【6】差分对设置;【7】检查,检查仿真的网络相关设置是否对,有错误错误。

4、IBIS模型到DML转换与分配&无源LRC模型创建修改;

【1】可以在这里直接转换,如图,点击就可以完成DML的转换;

【2】转换完成的文件在工作路径下;

【3】金手指的模型;

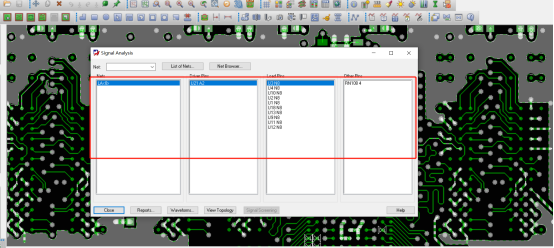

5、地址线仿真链路抽取和整理&533MHZ仿真设置;

这个地方提取信号仿真链路的时候,需要提前将芯片的模型,原件的模型,IO的模型,连接器的模型,等等和信号链路有关系的模型都赋予好,才能提出正确的拓扑结果。也就是上门的操作都需要先做,都设置好了在去提取。才可以。

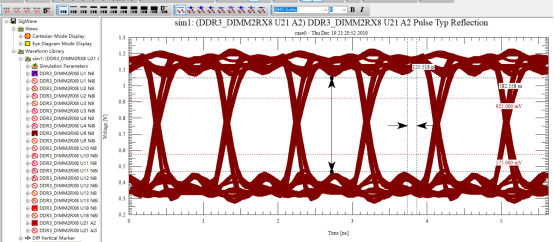

6、DDR3_DIMM2RX8仿真结果眼图分析解读&时钟线拓扑链路提取与拓扑整理;

7、DDR3_DIMM2RX8拓扑SigXp编辑&STUB支线拓扑扫描链路分支编辑修改;

【1】STUB的长度成1mm修改成了500mm之后,U18和U9的信号眼图如下,明显信号的质量下降,信号的不合格,眼宽和眼高都已经丢失。

【2】STUB之线的长度减少之后到5mm的时候,眼图如下所示,可以明显的看到,眼图的眼宽和眼高清晰可见。信号的质量明显提高。

【3】因此来说,我们需要STUB支线的长度越短越高,支线过长,会引起信号的多次反射,且信号延迟加长,信号的眼图质量下降。

【讲师介绍】:

李增(Wareleo),13年+模拟电路和数字电路及程序设计经验,著有多本Cadence和高速信号仿真书籍。资深开发工作爱好者,多次带领团队独立完成开发项目,并成功上市商用产品。在长期的开发中经验积累了丰富实战经验,尤其是快速电子类产品开发的精悍流程和开发技巧。熟悉Cadence, PADS, AD, Multisim, ADS,Sigrity, Ansys EM等EDA和分析工具,通过长期不懈的学习、探索与总结,已初步形成了一套基于高速PCB设计的实践经验及理论,累积上万粉丝。

扫码关注

扫码关注

![电子设计:数字逻辑电路基础知识回顾[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/d6/6631ce55ec5db0f7ae6624627d08cd.png)