01

栅极驱动部分

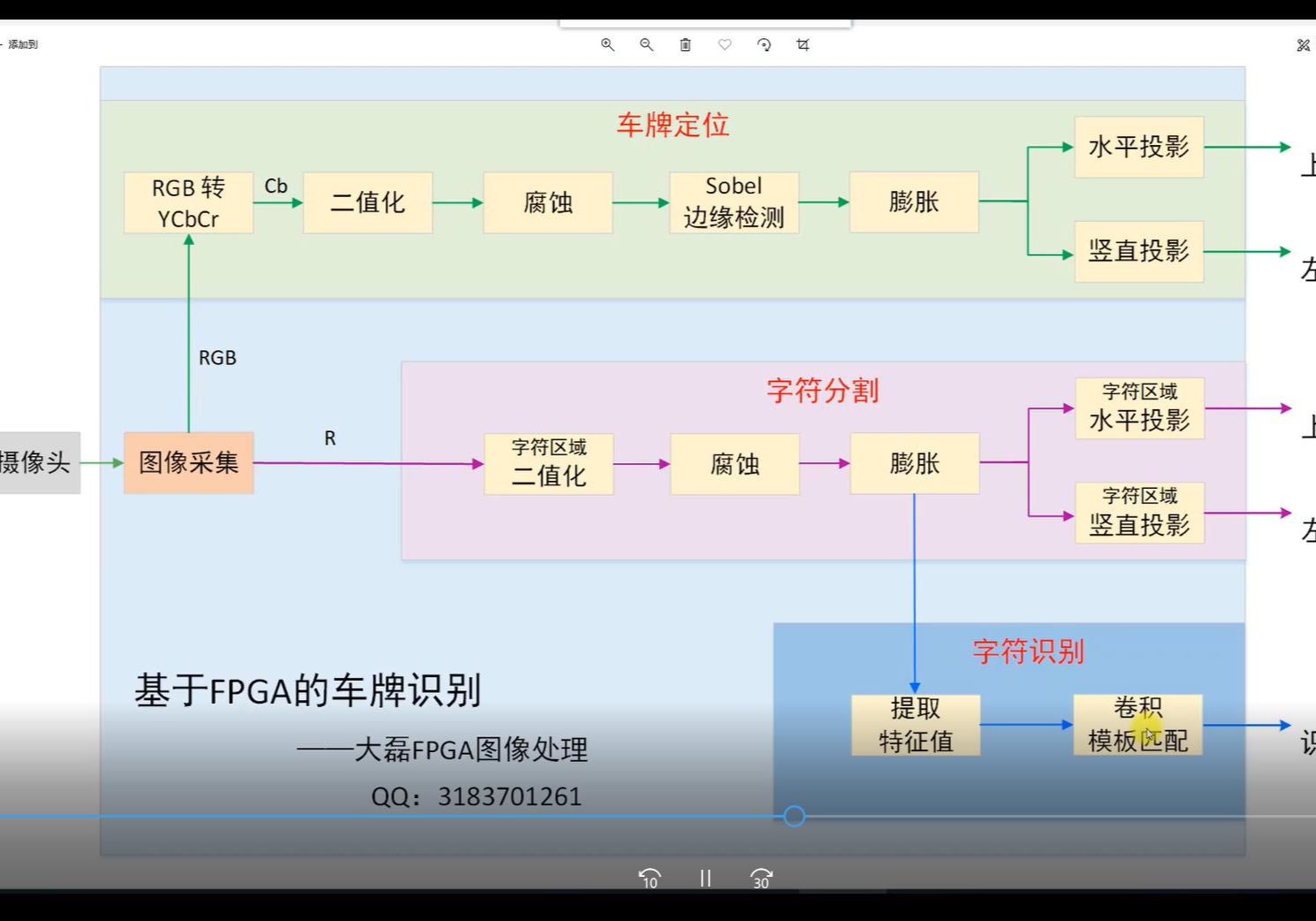

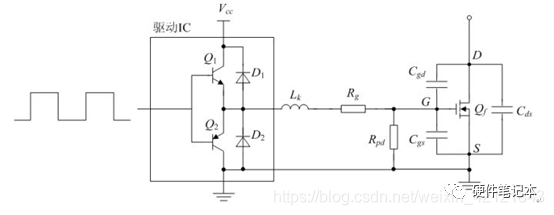

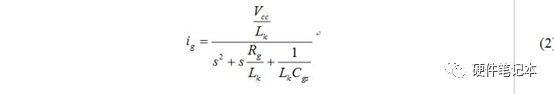

常用的mos管驱动电路结构如图1所示,驱动信号经过图腾柱放大后,经过一个驱动电阻Rg给mos管驱动。其中Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗等。在现在很多的应用中,用于放大驱动信号的图腾柱本身也是封装在专门的驱动芯片中。本文要回答的问题就是对于一个确定的功率管,如何合理地设计其对应的驱动电路(如驱动电阻阻值的计算,驱动芯片的选型等等)。

注1:图中的Rpd为mos管栅源极的下拉电阻,其作用是为了给mos管栅极积累的电荷提供泄放回路,一般取值在10k~几十k这一数量级。由于该电阻阻值较大,对于mos管的开关瞬态工作情况基本没有影响,因此在后文分析mos的开关瞬态时,均忽略Rpd的影响。

注2:Cgd,Cgs,Cds为mos管的三个寄生电容,在考虑mos管开关瞬态时,这三个电容的影响至关重要。

图1 mos驱动电路结构

1.1 驱动电阻的下限值

驱动电阻下限值的计算原则为:驱动电阻必须在驱动回路中提供足够的阻尼,来阻尼mos开通瞬间驱动电流的震荡。

当mos开通瞬间,Vcc通过驱动电阻给Cgs充电,如图2所示(忽略Rpd的影响)。根据图2,可以写出回路在s域内对应的方程:

根据式(1)可以求解出ig,并将其化为典型二阶系统的形式

根据式(2),可以求解出该二阶系统的阻尼比为:

为了保证驱动电流ig不发生震荡,该系统的阻尼比必须大于1,则根据(3)可以求解得到:

式(4)给出了驱动电阻Rg的下限值,式(4)中Cgs为mos管gs的寄生电容,其值可以在mos管对应的datasheet中查到。而Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗,驱动芯片引脚的感抗等,其精确的数值往往难以确定,但数量级一般在几十nH左右。

因此在实际设计时,一般先根据式(4)计算出Rg下限值的一个大概范围,然后再通过实际实验,以驱动电流不发生震荡作为临界条件,得出Rg下限值。

图2 mos开通时的驱动电流

1.2 驱动电阻的上限值

驱动电阻上限值的计算原则为:防止mos管关断时产生很大的dV/dt使得mos管再次误开通。

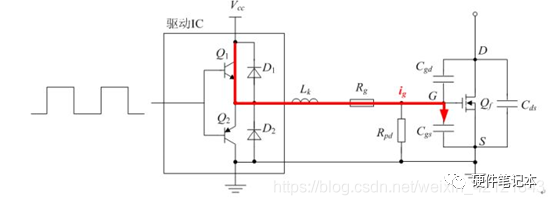

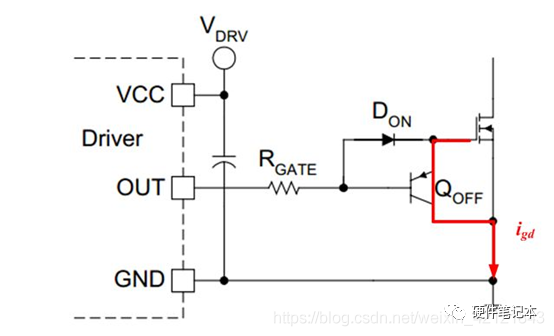

当mos管关断时,其DS之间的电压从0上升到Vds(off),因此有很大的dV/dt,根据公式:i=CdV/dt,该dV/dt会在Cgd上产生较大的电流igd,如图3所示。

图3 mos关断时的对应电流

该电流igd会流过驱动电阻Rg,在mos管GS之间又引入一个电压,当该电压高于mos管的门槛电压Vth时,mos管会误开通,为了防止mos管误开通,应当满足:

式(6)给出了驱动电阻Rg的上限值,式(6)中Cgd为mos管gd的寄生电容,Vth为mos管的门槛电压,均可以在对应的datasheet中查到,dV/dt则可以根据电路实际工作时mos的DS电压和mos管关断时DS电压上升时间(该时间一般在datasheet中也能查到)求得。

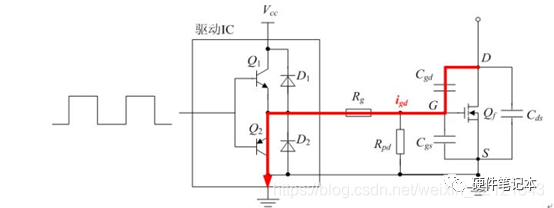

从上面的分析可以看到,在mos管关断时,为了防止误开通,应当尽量减小关断时驱动回路的阻抗。基于这一思想,下面再给出两种很常用的改进型电路,可以有效地避免关断时mos的误开通问题。

图4 改进电路1

图4给出的改进电路1是在驱动电阻上反并联了一个二极管,当mos关断时,关断电流就会流经二极管Doff,这样mos管gs的电压就为二极管的导通压降,一般为0.7V,远小于mos的门槛电压(一般为2.5V以上),有效地避免了mos的误开通。

图5 改进电路2

图5给出的改进电路2是在驱动电路上加入了一个开通二极管Don和关断三级管Qoff。当mos关断时,Qoff打开,关断电流就会流经该三极管Qoff,这样mos管gs的电压就被钳位至地电平附近,从而有效地避免了mos的误开通。

1.3 驱动电阻阻值的选择

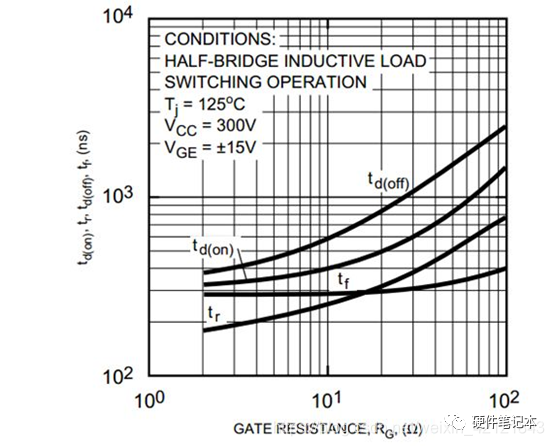

根据1.1节和1.2节的分析,就可以求得mos管驱动电阻的上限值和下限值,一般来说,mos管驱动电阻的取值范围在5~100欧姆之间,那么在这个范围内如何进一步优化阻值的选取呢?这就要从损耗方面来考虑,当驱动电阻阻值越大时,mos管开通关断时间越长(如图6所示),在开关时刻电压电流交叠时间久越大,造成的开关损耗就越大(如图7所示)。所以在保证驱动电阻能提供足够的阻尼,防止驱动电流震荡的前提下,驱动电阻应该越小越好。

图6 mos开关时间随驱动电阻的变化

比如通过式(4)和式(6)的计算得到驱动电阻的下限为5欧姆,上限为100欧姆。那么考虑一定的裕量,取驱动电阻为10欧姆时合适的,而将驱动电阻取得太大(比如50欧姆以上),从损耗的角度来讲,肯定是不合适的。

1.4 驱动芯片的选型

对于驱动芯片来说,选型主要考虑如下技术参数:驱动电流,功耗,传输延迟时间等,对隔离型驱动还要考虑原副边隔离电压,瞬态共模抑制等等(common mode transient immunity),下面就分别加以介绍。

最大电流

在mos管开通的时候,根据图2,可以得到mos开通瞬间的驱动电流ig为(忽略Lk的影响)

其中ΔVgs为驱动电压的摆幅,那么在选择驱动芯片的时候,最重要的一点就是驱动芯片能提供的最大电流要超过式(7)所得出的电流,即驱动芯片要有足够的“驱动能力”。

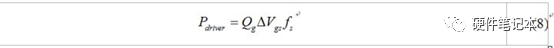

功耗

驱动功率计算表达式如下:

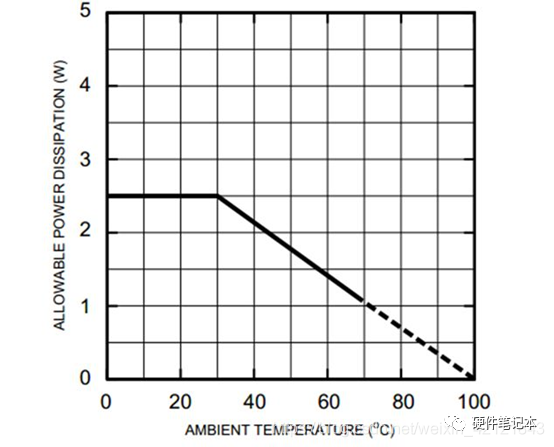

其中Qg为栅极充电电荷,可以在datasheet中查到,ΔVgs为驱动电压的摆幅,fs为mos的开关频率,在实际选择驱动芯片时,应选择驱动芯片所能提供的功率大于式(8)所计算出来的功率。同时还要考虑环境温度的影响,因为大多数驱动芯片所能提供的功率都是随着环温的升高而降额的,如图8所示。

图8 驱动允许的损耗功率随着环温升高而降低

传输延迟(Propagation Delay)

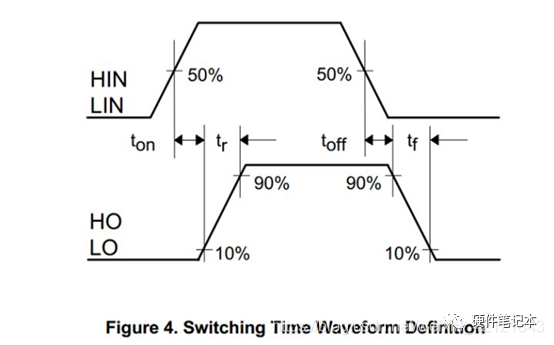

所谓传输延迟,即驱动芯片的输出上升沿和下降沿都要比起输入信号延迟一段时间,其对应的波形如图9所示。对于传输延迟来说,我们一般希望有两点:1)传输延时的实际要尽量短。2)“开通”传输延时和“关断”传输延时的一致性要尽量好。

图9 驱动芯片输入输出传输延时

下面就针对第二点来说一说,如果开通和关断传输延时不一致会有什么影响呢?我们以常用的IGBT驱动,光耦M57962为例,给出其传输延时的数据,如图10所示。

图10 M57962的传输延时数据

从图10可以看到,M57962的的开通传输延时一般为1us,最大为1.5us;关断传输延时一般为1us,最大为1.5us。其开通关断延时的一致性很差,这样就会对死区时间造成很大的影响。假设输入M57962的驱动死区设置为1.5us。那么实际到IGBT的GE级的驱动死区时间最大为2us(下管开通延时1.5us, 上管关断延时1us),最小仅为1us(下管开通延时1us, 上管关断延时1.5us)。造成实际到达IGBT的GE级的死区时间的不一致。因此在设计死区时间时,应当充分考虑到驱动芯片本身的传输延时的不一致性,避免因此造成的死区时间过小而导致的桥臂直通。

原副边绝缘电压

对于隔离型驱动来说(光耦隔离,磁耦隔离)。需要考虑原副边的绝缘电压,一般项目中都会给出绝缘电压的

相关要求。若没有相关要求,一般可取绝缘电压为mos电压定额的两倍以上。

02

外围保护电路

R7作用:防静电影响MOS,管子的DG,GS之间分别有结电容, DS之间电压会给电容充电,这样G极积累的静电电压就会抬高直到mos管导通,电压高时可能会损坏管子. 同时为结电容提供泄放通道,可以加快MOS开关速度。阻值一般为几千左右。

R6和D3作用:在MOS关断时,这个回路快速放掉栅极结电容的电荷,栅极电位快速下降,因此可以加快MOS开关速度。另外,高频时, MOSFET的输入阻抗将降低,而且在某个频率范围内将变成负阻,会发生振荡,这个电阻可以减少震荡。R6阻值一般较小,几欧到几十欧左右。

C11,R8和d5作用:MOS有分布电感,关断时会有反峰电压。Rc部分用于吸收尖波,这个设计给这个反峰提供了释放回路。D5是为了防止高电压击穿mos。经实验,去掉该回路后波形有很大的震荡。

03

减少振铃的方法

三种方法:

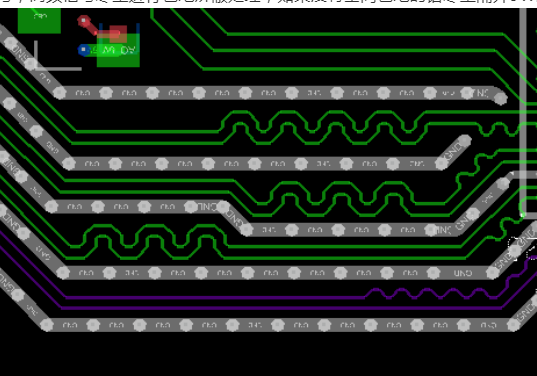

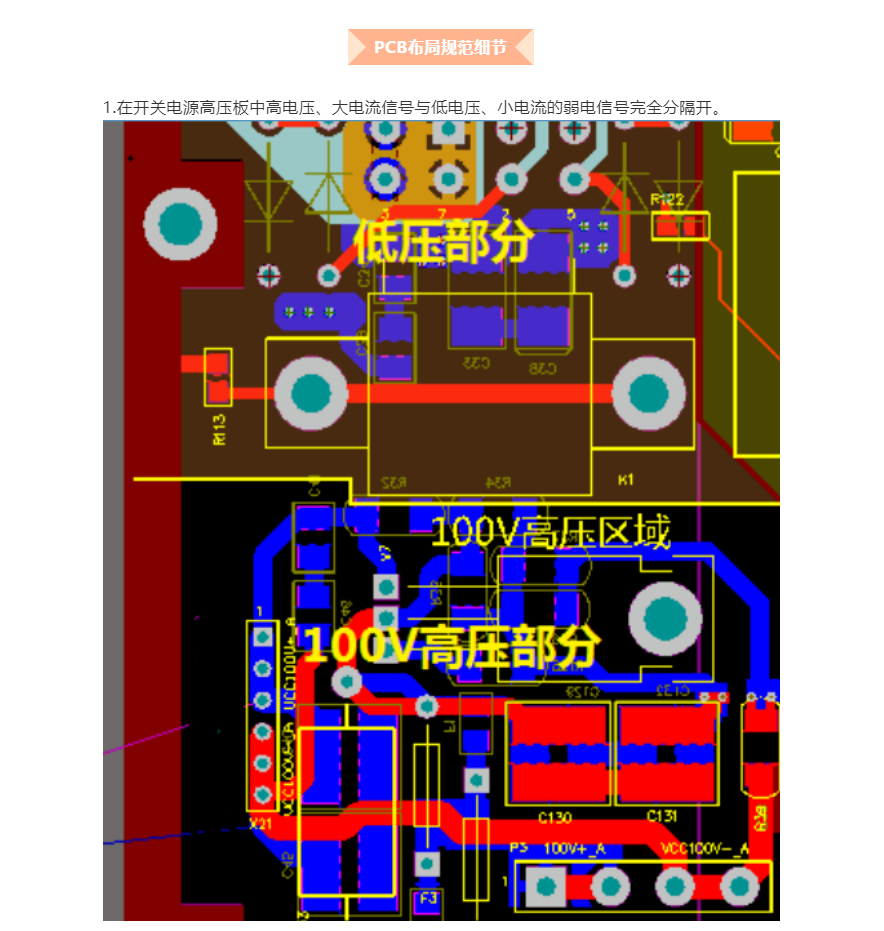

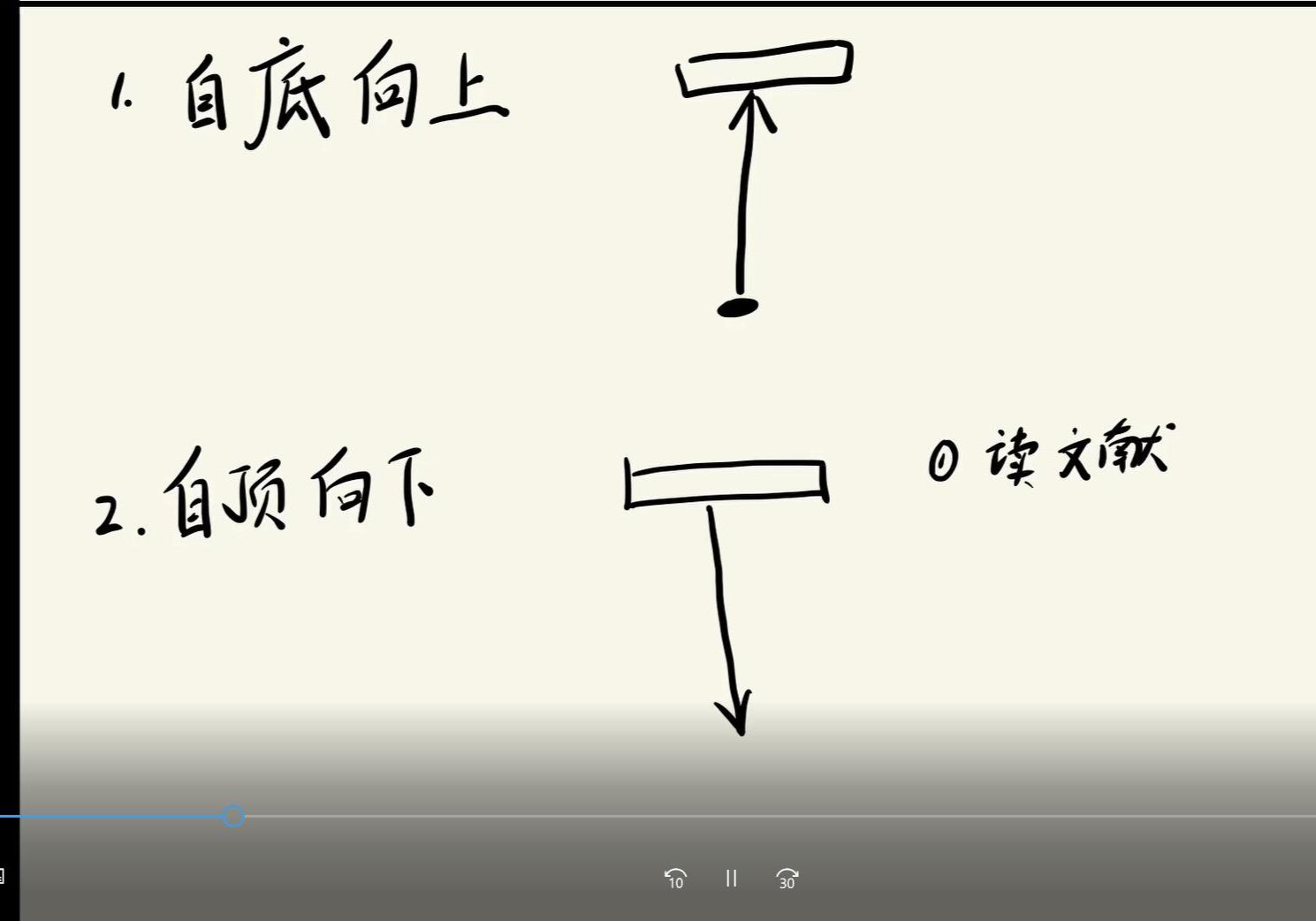

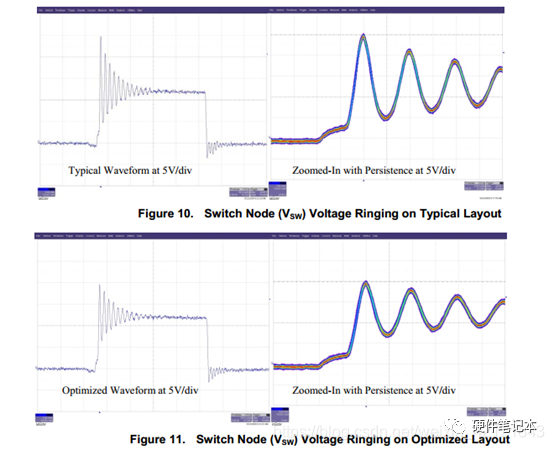

3.1 PCB设计

减少VCC,GND与MOS的距离

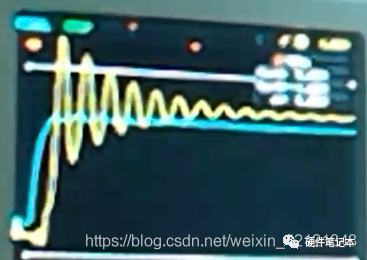

效果:

3.2 栅极/自举电阻

两电阻示意图如下:

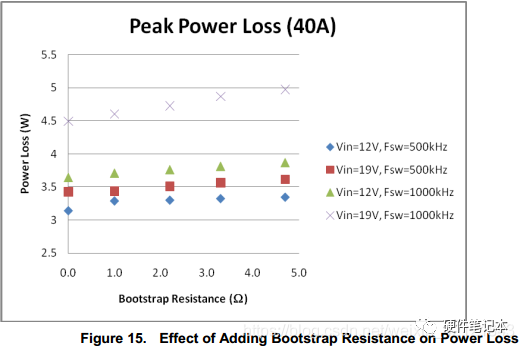

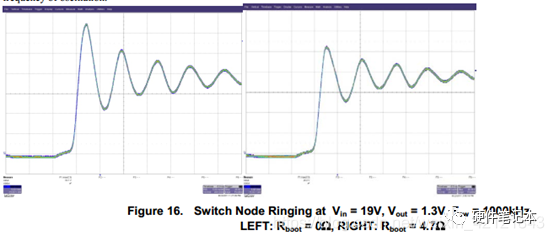

设计的特点是增加开通时间,但不影响关断时间。增大电阻可以减少振铃,但是会增大损耗,且不改变振铃频率,因为只是用其吸收能量罢了。

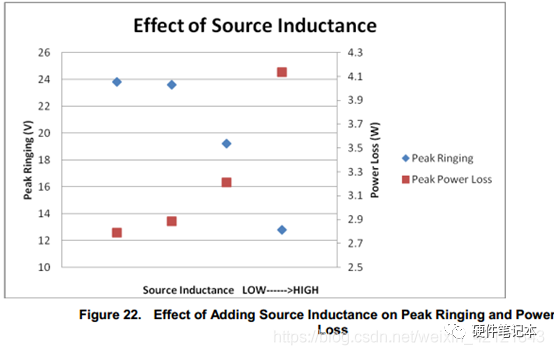

下面是振铃的幅度以及能量的损耗示意图:

3.3加入开关阻尼RC

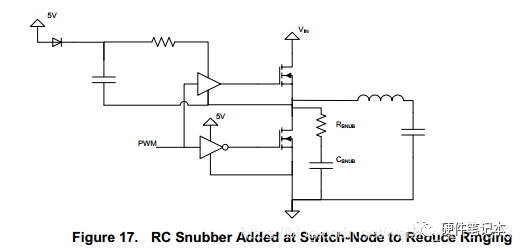

示意图

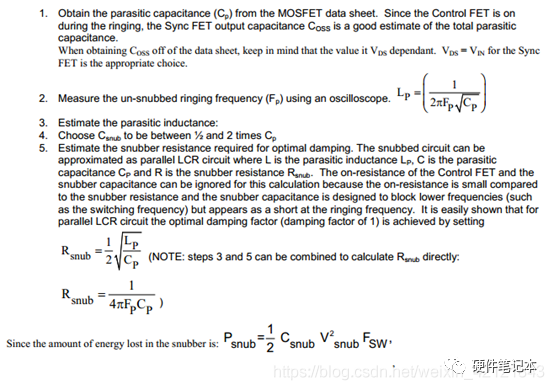

RC的选择可以根据示波器上测出的振铃频率计算:

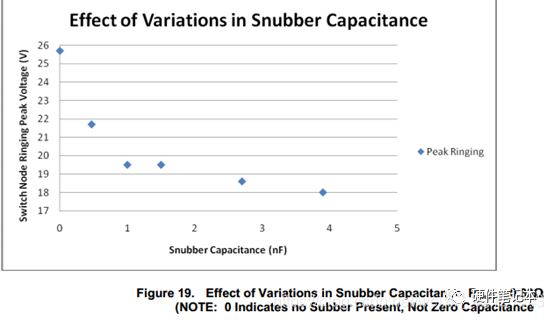

振铃减少的效果:

3.4 加入共源极电感

这种方法缺点是电感值难以调整,且损耗大。

3.5部分常见波形

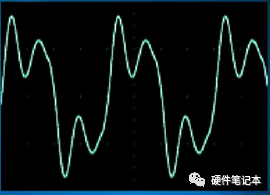

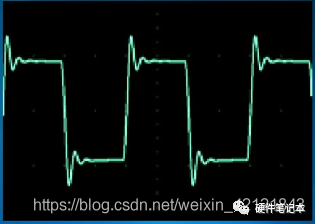

工作在线性区,损耗巨大,原因可能是布线太长,电感太大

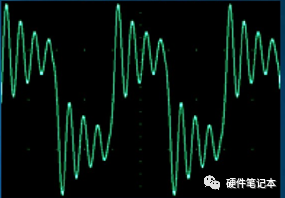

高频振铃严重

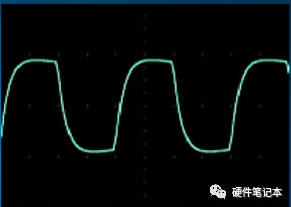

上升下降沿缓慢,可能因为驱动芯片驱动能力太差,或者是栅极驱动电阻太大

有振铃的方波,边沿陡峭,开关速度快,损耗小,可以略微增大栅极电阻

测量的是上管的驱动,由于自举电容较小,提供的电荷不足,无法保证GD间的电压

完美波形

04

缓冲电路设计

关于缓冲电路

基本拓扑电路上一般没有吸收缓冲电路,实际电路上一般有吸收缓冲电路,吸收与缓冲是工程需要,不是拓扑需要。

吸收与缓冲的功效:

●防止器件损坏,吸收防止电压击穿,缓冲防止电流击穿

●使功率器件远离危险工作区,从而提高可靠性

●降低(开关)器件损耗,或者实现某种程度的关软开

●降低di/dt和dv/dt,降低振铃,改善EMI品质

●降低di/dt和dv/dt,降低振铃,改善EMI品质

也就是说,防止器件损坏只是吸收与缓冲的功效之一,其他功效也是很有价值的。

吸收

吸收是对电压尖峰而言。

电压尖峰的成因 :

●电压尖峰是电感续流引起的。

●引起电压尖峰的电感可能是:变压器漏感、线路分布电感、器件等效模型中的感性成分等。

●引起电压尖峰的电流可能是:拓扑电流、二极管反向恢复电流、不恰当的谐振电流等。

减少电压尖峰的主要措施是:

●减少可能引起电压尖峰的电感,比如漏感、布线电感等

●减少可能引起电压尖峰的电流,比如二极管反向恢复电流等

●如果可能的话,将上述电感能量转移到别处。

●采取上述措施后电压尖峰仍然不能接受,最后才考虑吸收。吸收是不得已的技术措施

拓扑吸收

将开关管Q1、拓扑续流二极管D1和一个无损的拓扑电容C2组成一个在布线上尽可能简短的吸收回路。

拓扑吸收的特点:

●同时将Q1、D1的电压尖峰、振铃减少到最低程度。

●拓扑吸收是无损吸收,效率较高。

●吸收电容C2可以在大范围内取值。

●拓扑吸收是硬开关,因为拓扑是硬开关。

体二极管反向恢复吸收

开关器件的体二极管的反向恢复特性,在关断电压的上升沿发挥作用,有降低电压尖峰的吸收效应。

RC吸收

●RC吸收的本质是阻尼吸收。

●有人认为R 是限流作用,C是吸收。实际情况刚好相反。

●电阻R 的最重要作用是产生阻尼,吸收电压尖峰的谐振能量,是功率器件。

●电容C的作用也并不是电压吸收,而是为R阻尼提供能量通道。

●RC吸收并联于谐振回路上,C提供谐振能量通道,C 的大小决定吸收程度,最终目的是使R形成功率吸收。

●对应一个特定的吸收环境和一个特定大小的电容C,有一个最合适大小的电阻R,形成最大的阻尼、获得最低的电压尖峰。

●RC吸收是无方向吸收,因此RC吸收既可以用于单向电路的吸收,也可用于双向或者对称电路的吸收。

RC吸收设计

●RC吸收的设计方法的难点在于:吸收与太多因素有关,比如漏感、绕组结构、分布电感电容、器件等效电感电容、电流、电压、功率等级、di/dt、dv/dt、频率、二极管反向恢复特性等等。而且其中某些因素是很难获得准确的设计参数的。

●比如对二极管反压的吸收,即使其他情况完全相同,使用不同的二极管型号需要的RC吸收参数就可能有很大差距。很难推导出一个通用的计算公式出来。

●R 的损耗功率可大致按下式估算:

Ps = FCU2

其中U为吸收回路拓扑反射电压。

●工程上一般应该在通过计算或者仿真获得初步参数后,还必须根据实际布线在板调试,才能获得最终设计参数。

RCD吸收

特点

●RCD吸收不是阻尼吸收,而是靠非线性开关D 直接破坏形成电压尖峰的谐振条件,把电压尖峰控制在任何需要的水平。

●C 的大小决定吸收效果(电压尖峰),同时决定了吸收功率(即R的热功率)。

●R 的作用只是把吸收能量以热的形式消耗掉。其电阻的最小值应该满足开关管的电流限制,最大值应该满足PWM逆程RC放电周期需要,在此范围内取值对吸收效果影响甚微。

●RCD吸收会在被保护的开关器件上实现某种程度的软关断,这是因为关断瞬间开关器件上的电压即吸收电容C上的电压等于0,关断动作会在C 上形成一个充电过程,延缓电压恢复,降低dv/dt,实现软关断。

不适应性

●RCD吸收一般不适合反激拓扑的吸收,这是因为RCD吸收可能与反激拓扑相冲突。

●RCD吸收一般不适合对二极管反压尖峰的吸收,因为RCD吸收动作有可能加剧二极管反向恢复电流。

钳位吸收

RCD 钳位

●尽管RCD钳位与RCD吸收电路可以完全相同,但元件参数和工况完全不同。RCD吸收RC时间常数远小于PWM周期,而RCD钳位的RC时间常数远大于PWM周期。

●与RCD吸收电容的全充全放工况不同,RCD钳位的电容可以看成是电压源,其RC充放电幅度的谷值应不小于拓扑反射电压,峰值即钳位电压。

●由于RCD钳位在PWM电压的上升沿和下降沿都不会动作,只在电压尖峰出现时动作,因此RCD钳位是高效率的吸收。

齐纳钳位

●齐纳钳位的几种形式。

●齐纳钳位也是在电压尖峰才起作用,也是高效率吸收。

●某些场合,齐纳钳位需要考虑齐纳二极管的反向恢复特性对电路的影响。

●齐纳吸收需注意吸收功率匹配,必要时可用有源功率器件组成大功率等效电路

无损吸收

无损吸收的条件

●吸收网络不得使用电阻。

●不得形成LD电流回路。

●吸收回路不得成为拓扑电流路径。

●吸收能量必须转移到输入侧或者输出侧。

●尽量减少吸收回路二极管反向恢复电流的影响。

无损吸收是强力吸收,不仅能够吸收电压尖峰,甚至能够吸收拓扑反射电压

缓冲

缓冲是对冲击尖峰电流而言

●引起电流尖峰第一种情况是二极管(包括体二极管)反向恢复电流。

●引起电流尖峰第二种情况是对电容的充放电电流。这些电容可能是:电路分布电容、变压器绕组等效分布电容、设计不恰当的吸收电容、设计不恰当的谐振电容、器件的等效模型中的电容成分等等。

缓冲的基本方法:

●在冲击电流尖峰的路径上串入某种类型的电感,可以是以下类型:

缓冲的特性:

●由于缓冲电感的串入会显著增加吸收的工作量,因此缓冲电路一般需要与吸收电路配合使用。

●缓冲电路延缓了导通电流冲击,可实现某种程度的软开通(ZIS)。

●变压器漏感也可以充当缓冲电感。

LD 缓冲

特点:

●可不需要吸收电路配合。

●缓冲释能二极管与拓扑续流二极管电流应力相当甚至更大。

●缓冲释能二极管的损耗可以简单理解为开关管减少的损耗。

●适当的缓冲电感(L3)参数可以大幅度减少开关管损耗,实现高效率。

LR 缓冲

特点:

●需要吸收电路配合以转移电感剩余能量。

●缓冲释能电阻R的损耗较大,可简单理解为是从开关管转移出来的损耗。

●R、L参数必须实现最佳配合,参数设计调试比较难以掌握。

●只要参数适当仍然能够实现高效率。

饱和电感缓冲

●饱和电感的电气性能表现为对di/dt敏感。

●在一个冲击电流的上升沿,开始呈现较大的阻抗,随着电流的升高逐渐进入饱和,从而延缓和削弱了冲击电流尖峰,即实现软开通。

●在电流达到一定程度后,饱和电感因为饱和而呈现很低的阻抗,这有利于高效率地传输功率。

●在电流关断时,电感逐渐退出饱和状态,一方面,由于之前的饱和状态的饱和电感量非常小,即储能和需要的释能较小。另一方面,退出时电感量的恢复可以减缓电压的上升速度,有利于实现软关断。

●以Ls2为例,5u表示磁路截面积5mm2,大致相当于1颗PC40材质442的小磁芯饱和电感特性

●热特性

饱和电感是功率器件,通过进入和退出饱和过程的磁滞损耗(而不是涡流损耗或者铜损)吸收电流尖峰能量,主要热功率来自于磁芯。

这一方面要求磁芯应该是高频材料,另一方面要求磁芯温度在任何情况下不得超过居里温度。这意味着饱和电感的磁芯应该具有最有利的散热特性和结构,即:更高的居里温度、更高的导热系数、更大的散热面积、更短的热传导路径。

●饱和特性

显然饱和电感一般不必考虑使用气隙或者不易饱和的低导磁率材料。

●初始电感等效特性

在其他条件相同情况下,较低导磁率的磁芯配合较多匝数、与较高导磁率的磁芯配合较少匝数的饱和电感初始电感相当,缓冲效果大致相当。

这意味着直接采用1 匝的穿心电感总是可能的,因为任何多匝的电感总可以找到更高导磁率的磁芯配合1 匝等效之。这还意味着磁芯最高导磁率受到限制,如果一个适合的磁芯配合1 匝的饱和电感,将没有使用更高导磁率的磁芯配合更少匝数的可能。

●磁芯体积等效特性

在其他条件相同情况下,相同体积的磁芯的饱和电感缓冲效果大致相当。既然如此,磁芯可以按照最有利于散热的磁路进行设计。比如细长的管状磁芯比环状磁芯、多个小磁芯比集中一个大磁芯、穿心电感比多匝电感显然具有更大的散热表面积。

●组合特性

有时候,单一材质的磁芯并不能达到工程上需要的缓冲效果,采用多种材质的磁芯相互配合或许才能能够满足工程需要。

无源无损缓冲吸收

●如果缓冲电感本身是无损的(非饱和电感),而其电感储能又是经过无损吸收的方式处理的,即构成无源无损缓冲吸收电路,实际上这也是无源软开关电路。

●缓冲电感的存在延迟和削弱的开通冲击电流,实现了一定程度的软开通。

●无损吸收电路的存在延迟和降低了关断电压的dv/dt,实现了一定程度的软关断。

●实现无源软开关的条件与无损吸收大致相同。并不是所有拓扑都能够搭建出一个无源软开关电路。因此除了经典的电路外,很多无源软开关电路都是被专利的热门。

●无源无损软开关电路效率明显高于其他缓冲吸收方式,与有源软开关电路效率相差无几。因此只要能够实现无源软开关的电路,可不必采用有源软开关。

滤波缓冲

●电路中的电解电容一般具有较大的ESR(典型值是百毫欧姆数量级),这引起两方面问题:一是滤波效果大打折扣;二是纹波电流在ESR上产生较大损耗,这不仅降低效率,而且由于电解电容发热直接导致的可靠性和寿命问题。

●一般方法是在电解电容上并联高频无损电容,而事实上,这一方法并不能使上述问题获得根本的改变,这是由于高频无损电容在开关电源常用频率范围内仍然存在较大的阻抗的缘故。

●提出的办法是:用电感将电解和CBB分开,CBB位于高频纹波电流侧,电解位于直流(工频)侧,各自承担对应的滤波任务。

●设计原则:Π形滤波网络的谐振频率Fn应该错开PWM频率Fp。可取Fp=(1.5~2)Fn 。

●这一设计思想可以延伸到直流母线滤波的双向缓冲,或者其他有较大滤波应力的电路结构。

振铃

振铃的危害:

●MEI测试在振铃频率容易超标。

●振铃将引起振铃回路的损耗,造成器件发热和降低效率。

●振铃电压幅度超过临界值将引起振铃电流,破环电路正常工况,效率大幅度降低。

振铃的成因:

●振铃多半是由结电容和某个等效电感的谐振产生的。对于一个特定频率的振铃,总可以找到原因。电容和电感可以确定一个频率,而频率可以观察获得。电容多半是某个器件的结电容,电感则可能是漏感。

●振铃最容易在无损(无电阻的)回路发生。比如:副边二极管结电容与副边漏感的谐振、杂散电感与器件结电容的谐振、吸收回路电感与器件结电容的谐振等等。

振铃的抑制:

●磁珠吸收,只要磁珠在振铃频率表现为电阻,即可大幅度吸收振铃能量,但是不恰当的磁珠也可能增加振铃。

●RC 吸收,其中C可与振铃(结)电容大致相当,R 按RC吸收原则选取。

●改变谐振频率,比如:只要将振铃频率降低到PWM频率相近,即可消除PWM上的振铃。

●特别地,输入输出滤波回路设计不当也可能产生谐振,也需要调整谐振频率或者其他措施予以规避。

吸收缓冲能量再利用:

RCD吸收能量回收电路

●只要将吸收电路的正程和逆程回路分开,形成相对0 电位的正负电流通道,就能够获得正负电压输出。其设计要点为:

●RCD吸收电路参数应主要满足主电路吸收需要,不建议采用增加吸收功率的方式增加直流输出功率。输出电流由L1、R1控制。逆程回路的阻抗同样应满足吸收回路逆程时间的需要,调整L1、R1的大小可控制输出功率大小,当R1减少到0时,该电路达到最大可能输出电流和最大输出功率。

●输出电压基本上可由齐纳门槛电压任意设定,需注意齐纳二极管的功率匹配。

RCD钳位能量回收电路

RCD钳位吸收回收电路输出电压与钳位电压有关,可控制范围有限。如果回收电源负载不能确定,需要确保在任意负载状态下吸收状态不变,不影响主电路。

注意回收电路的接地,避免成为共模干扰源。

扫码关注

扫码关注