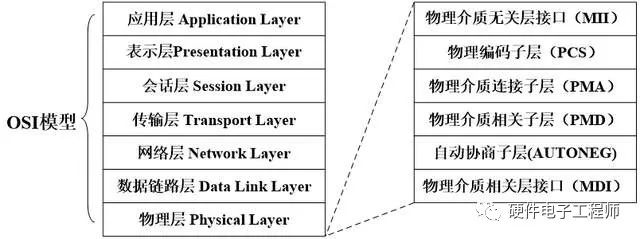

以前信号完整性(SI)问题仅仅出现在高速电路板,但随着电子器件的特征尺寸越来越小元件的供电电压、噪声容限也开始下降,耦合电容增加,这些都导致了在IC系统中会出现信号完整性问题,那么该如何处理IC设计的信号完整性问题?

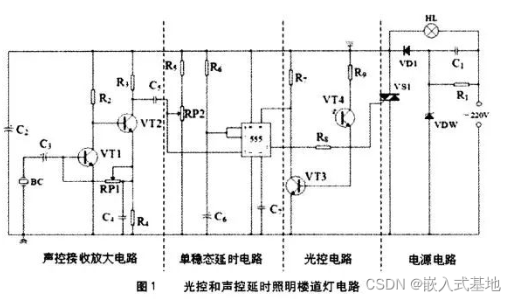

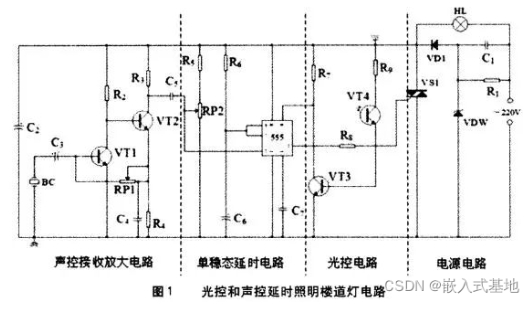

一般来说,影响信号完整性的因素主要分为串扰(crosstalk)和电源上的电压降(IR drop),前者主要是由连线的耦合电容引起的,后者是由连线的电阻效应引起的。

一般来说,串扰是会影响到芯片的时序和功能,而串扰的分析与纠正必须借助串扰分析工具、寄生参数提取工具与物理设计工具,当工程师在分析串扰时,必须要有噪声库。

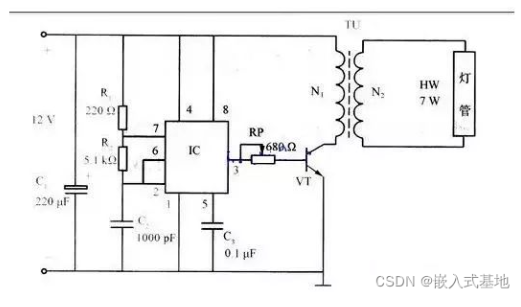

众所周知,电流流经一个有电阻的导线时会导致欧姆电压降,电源网格(VDD和GND)上的电压降将会降低芯片内单元的供电电压,这种现象会影响到芯片时序甚至导致IC系统功能出错,

分析IR drop时,可以将电源网格看作是由电阻(导线)、电流源(逻辑)构成的网格。由于在芯片中各单元的峰值电流是随时间变化的,因此IR drop是一种动态现象。影响IR drop的主要因素是一些切换事件,如时钟上的切换事件,总线驱动器上的切换事件等。

目前已有一些电源网格分析工具,例如CadencePower和RailMill。这些工具可以对芯片中的电流进行动态分析,并能够对电源网格进行模拟。

扫码关注

扫码关注

![电子设计:[2021电赛F题]OpenMV模板匹配实用教程,8数字同时识别40帧+,源码程序一行一行讲解,包教包会](https://api.fanyedu.com/uploads/image/f9/db2f5ce7a4caa6438d4267bfa894c0.png)