USB 2.0和USB 3.0是最常见的通用串行总线,也是应用广泛的输入输出技术规范,也是由Intel公司开发的总线架构之一,被广泛应用在个人电脑和移动设备等信息通讯产品,因此是工程师最为了解的接口之一,但很多人可能不太清楚USB 2.0/3.0接口的布局布线方法,所以今天分享这些设计方法。

1、USB 2.0

①USB接口靠近PCB板边放置,并伸出板边一定位置,方便插拔;

②串接阻容、ESD器件靠近USB接口,注意ESD和USB的距离,留有1.5mm的间距,也要考虑后焊的情况。

③在布局时,尽量使差分线路最短,以缩短差分线距离。

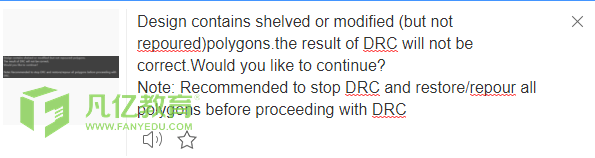

④USB要走差分,阻抗控制为90欧姆,并包地处理,总长度最好不要超过4800mil。

⑤USB差分走线在走线的时候,尽可能有减少换层过孔,过孔会造成线路阻抗的不连续,在每次打孔换层的地方加一对回流地过孔,用于信号回流换层。

⑥若USB两边定位柱接的是保护地,分割时候保证与GND的距离是2mm,并在保护地区域多打孔,保证充分连接。

⑦由于管脚分布、过孔、及走线空间等因素存在使得差分线长易不匹配,布线长一旦不匹配,时序会发生偏差,还会引起公民个人,降低信号质量,所以相应的要对差分对不匹配的情况做出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里。

2、USB 3.0

①ESD、共模电感器件靠近USB接口,放置顺序是ESD-共模电感-阻容;同样也要注意ESD和USB的距离,留有1.5mm间距,也要考虑后焊情况。

②终端匹配电阻应该尽可能靠近连接器放置,电压稳压器也应该仅能能靠近连接器放置。

②终端匹配电阻应尽可能靠近连接器放置,电压稳压器也应该尽可能靠近连接器放置。

③尽可能缩短走线长度,优先考虑对高速USB差分的布线,尽可能减少在USB信号线上的过孔数和拐角,从而可以更好做到阻抗的控制,避免信号的反射。

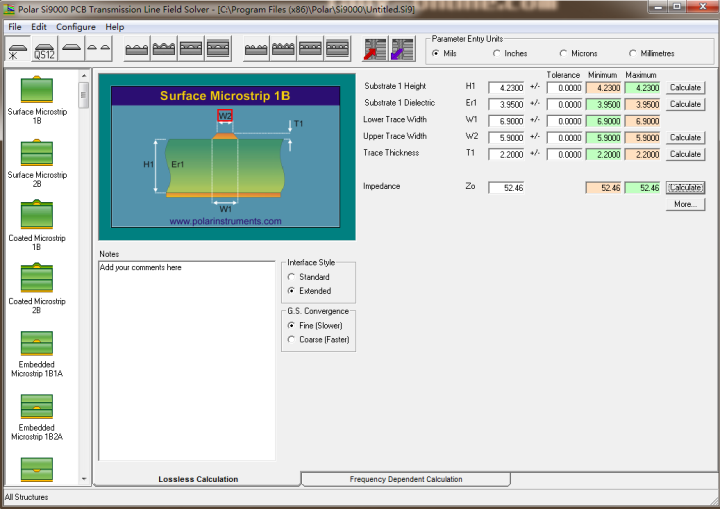

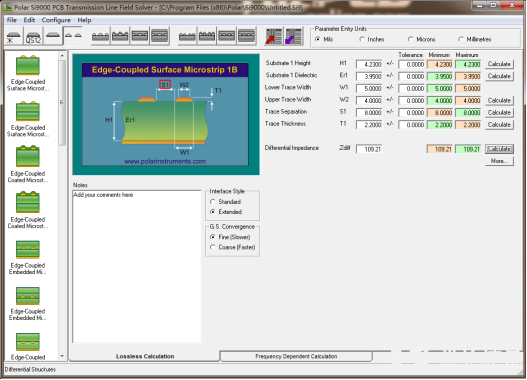

④在并行的USB差分信号对之间的阻抗,要确保90欧姆的差分阻抗,差分对间信号之间采用紧耦合模式,即走线之间的间距小于走线的宽度,这样能够提高差分信号抗外界噪声干扰的能力,具体的走线间距和宽度需要通过相关的软件计算确定。

⑤尽可能将高速信号走在同一层里,保证走线的返回路径有一个完整的无分割的镜像平面,避免跨分割。

扫码关注

扫码关注