随着业界对增加晶体管密度、增加带宽和降低功耗的需求越来越迫切,许多 IC 设计和封装团队都在深入研究如何增加垂直堆叠多个芯片裸片(die)和小芯片(chiplet)的方案。这种被称为3D-IC 的技术有望实现许多超越传统单裸片在单平面设计的优势。其架构可以将多个同质和异质的裸片/小芯片 Chiplet(例如逻辑、内存、模拟和射频功能)整合到同一设计中。这为系统级芯片(SoC)的集成提供了一个替代方案,支持设计人员希望集成在单一设计中的所有功能,并因此节省在新的制程节点重新设计这些功能而花费的昂贵成本。

3D-IC 有望在网络、图形、AI/ML 和高性能计算等领域产生广泛影响,特别是对于需要超高性能、低功耗器件的应用而言。具体的应用领域包括多核 CPUs、GPUs、数据包缓冲器/路由器、智能手机和 AI/ML 应用。虽然人们对这一新兴技术很感兴趣,但它仍然处于早期阶段。缺乏标准的定义、供应链生态系统仍在不断变化,并且需要解决设计、分析、验证和测试方面的挑战。

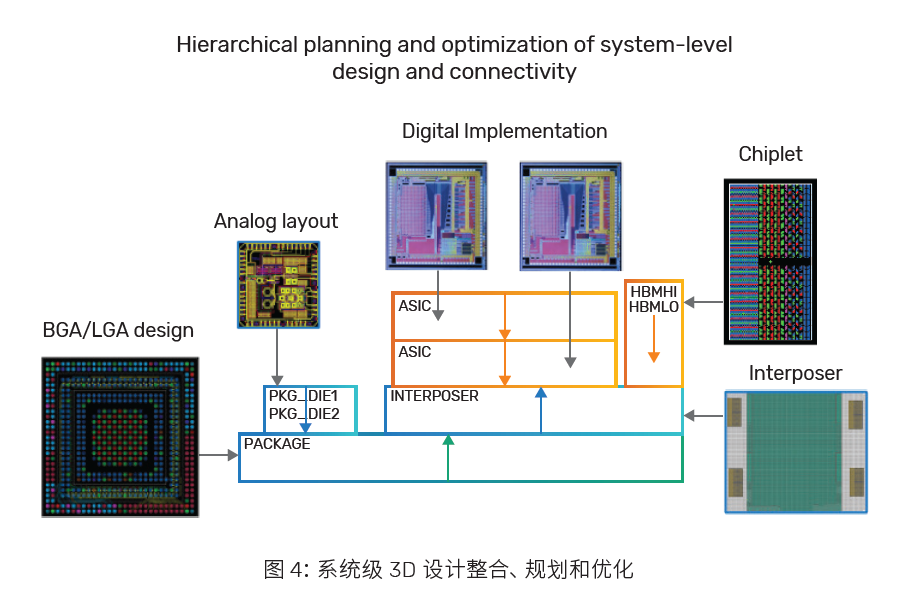

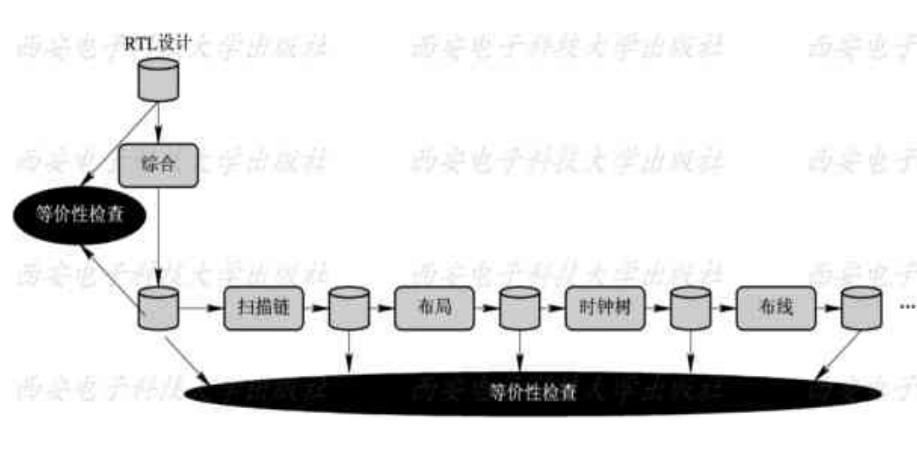

从设计的角度来看,要实现真正的 3D 集成,需要对某些设计工具进行一些加强。尤其在架构分析、热分析、多裸片间的排置、时序、测试和验证方面的功能都需要提升。此外,还需要新的系统级功能,如顶层规划和优化、芯片裸片(die)之间和小芯片(chiplet)之间的信号完整性和 IC/封装协同设计。其中一些功能现在已经具备,可以在系统设计工具中实现。

最终,设计人员需要能将所需功能全部汇聚到单一集成的设计平台的解决方案。成功的 3D-IC 设计环境可以在前期阶段捕获顶层设计意图,通过早期的功耗/发热估算支持抽象化,并通过实现、提取、时序收敛、测试、分析和封装之间实现融合。

本白皮书为PDF版本,全长7页,将简要介绍3D-IC 技术,并讨论设计挑战、生态系统要求和所需的解决方案。虽然各种类型的多晶粒封装已经存在多年,但本白皮书的关注重点是 3D 集成和多个堆叠裸片的封装:

引言

近距离分析 3D-IC

3D-IC 设计挑战与设计需求

数据提取和分析

面向测试的设计

打造 3D-IC 生态系统

结论

扫码关注

扫码关注

![电子设计:应用FFT计算线性卷积[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/3c/1a8c35db4b2ff59b9909422a499453.png)