在今年的 IMAPS(International Microelectronics Assembly and Packaging Society,国际微电子装配与封装学会 )大会上,Cadence 资深半导体封装管理总监 John Park 发表了关于封装组装设计套件(Package Assembly Design Kits,简称 ADK)的演讲:什么是 ADK,以及 ADK 能为封装设计带来哪些好处?

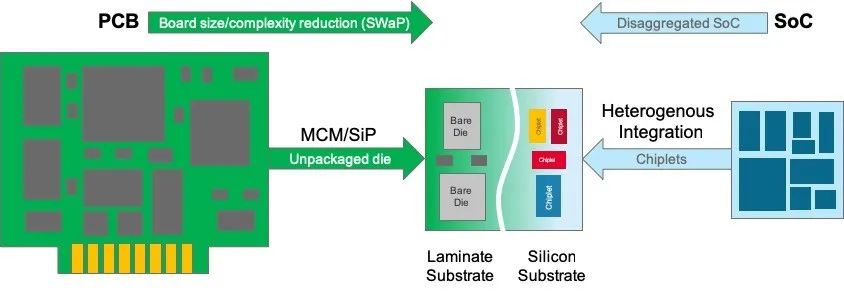

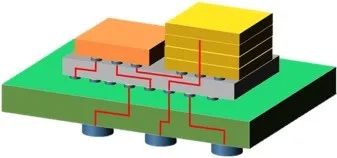

由于异质集成对不同的人来说意义各不相同,John 首先介绍了该市场的发展历史和趋势:几十年来,我们一直在从事多芯片模块 (Multi-Chip Module,简称MCM) 和类似的集成工作;但在过去五年左右的时间里,该领域更加专注于系统级芯片(System on Chip,简称 SoC)集成——不同于将所有元件都放在一个大芯片上,当前的焦点在于制造更小的芯片,通常称为“chiplet”,并把它们集成在某种高级封装中。

这种方法有很多优点,具体取决于设计的细节,其中包括:

降低 NRE(Non-recurring engineering Expense,一次性工程费用) 成本

加快产品上市

实现比标线尺寸更大的设计

更灵活的架构(多进程)

PDKs

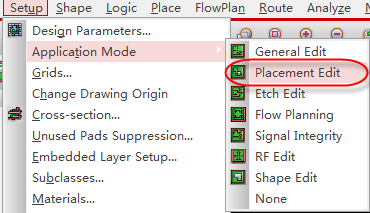

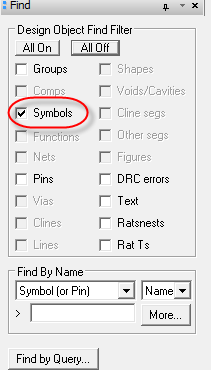

在 20 世纪 90 年代初创建 PDK(Process Design Kits,制程设计套件)之前,设计规则文件和用于电路仿真的 SPICE deck 几乎充当了晶圆厂和设计师之间的接口。随着工艺变得越来越复杂,设计规则的复杂性也在不断增加,因此上述做法无法再满足要求。

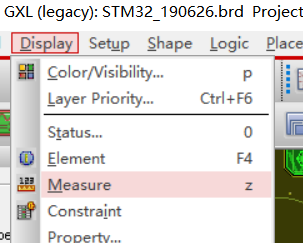

PDK 的理念是,把 IC 设计者需要知道的关于制造过程的一切知识打包起来,以实现成功设计。PDK 可以被现代 EDA 工具流程所读取,因此实际的 DRC deck 取代了过去的印刷版 DRC 手册。

面向封装设计师的类似 PDK 的解决方案

当设计变得越来越难,需要考虑的方面就越来越多。这导致封装设计团队需要考虑的设计方面日益增长:

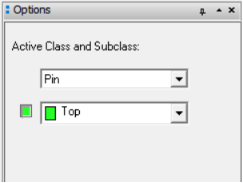

高级多芯片(多chiplet)、基于硅的封装需要专门的版图特征和形式化的物理/逻辑验证能力

特定于硅(矽)基板设计的版图特征

高级泪滴补强和走线加宽

渐进式铺铜和透氧孔的算法

大容量设计支持

来自封装设计的光罩级精确输出数据 (GDSII)

高级圆弧向量化

与 IC 实体验证工具无缝集成,并提供与封装设计工具间的反馈

光罩级 DRC

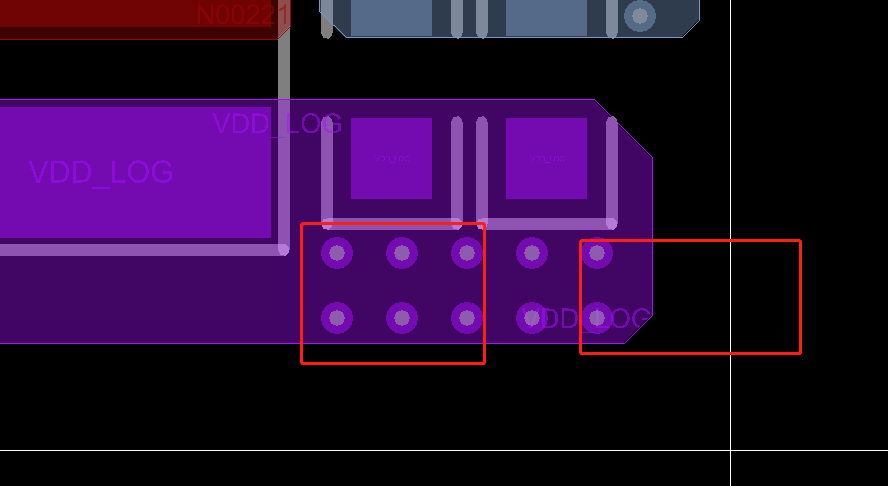

多芯片(多chiplet)设计的连通性验证(电路与布局验证)

特定区域的高级金属填充(平衡)

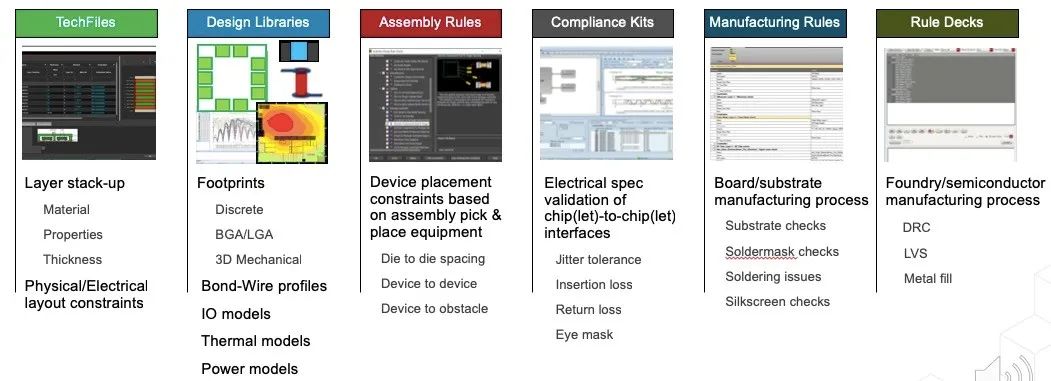

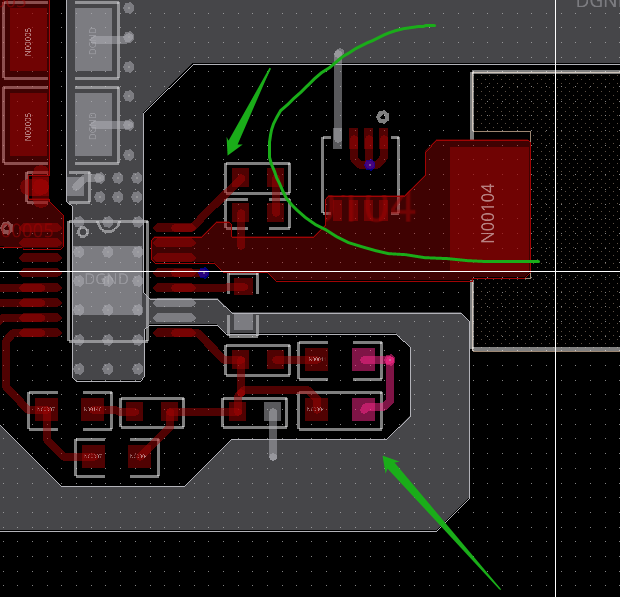

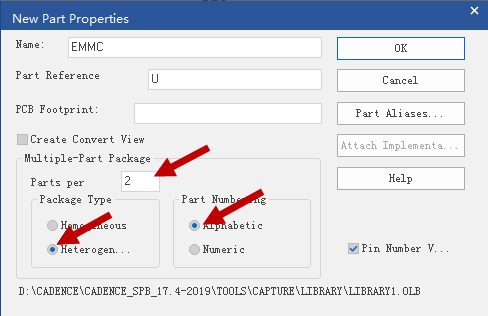

如果想让封装设计师在设计中停止猜测,就需要 ADK 封装组装设计套件,其工作方式类似于 PDK。但是,一个复杂的问题是,封装设计师对所有这些硅(矽)问题都很陌生,而 IC 设计师对封装也很陌生。那么,ADK 中会有哪些内容呢?

上表列出了 John Park认为应该放在 ADK 中的组件。让我们分别深入了解一下:

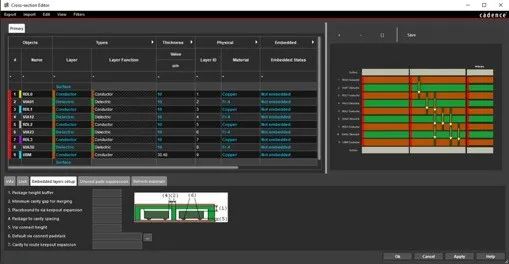

1、技术文件组件

这些应该是文本文件,以便于读取、写入、比较和共享

基板堆叠物理和电气细节

信号的物理/间距约束

信号的电气约束

约束分组

组装/放置规则

测试规则

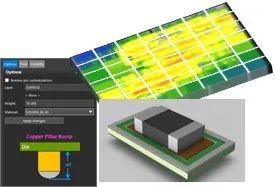

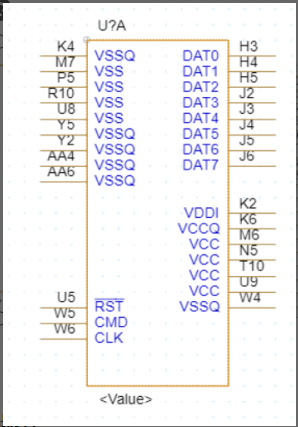

2、设计库和模型组件

Footprints

JEDEC 标准 BGA/LGA 和 SMD

焊盘

STEP 文件(真正的 3D 渲染)

3D 键合线文件

基于键合设备的模型

3D DRC 所需

I/O 模型

行为 (IBIS)

晶体管级

热/功耗模型

芯片(小芯片)级热和功耗模型

静态和瞬态功耗信息

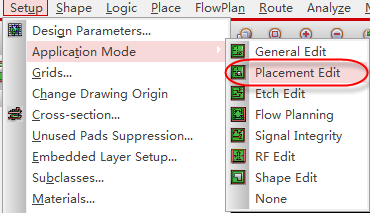

3、装配设计组件

GUI 图形式界面,简化设置

设备独有的 DFA 概要

设计同步、直接反馈组件的放置和移动情况

表格驱动、带用户定义的组件类别

基本模式(表格)和高级模式(约束管理器)

规则定义的设置可以在库级的单独工具中完成

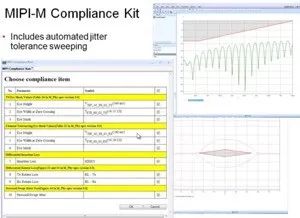

4、用于验证chiplet 到chiplet互连的

合规性测试包组件

基于与 PCB 类似的合规经验

抖动容限

插入损耗

回波损耗

眼图模板(用于 SerDes)

5、规则检查(硅(矽)中介层)组件

设计规则检查

包括 3D 堆栈引脚对齐

电路与布局验证

芯片到芯片(chiplet到chiplet)

系统级

金属填充

智能金属平衡

抓住机遇,引领市场

对于应当立刻采用ADK的原因,John Park表示:

“

数十年来,PDK 在 IC 设计界已经得到成功采用

封装技术的复杂性呈爆炸式增长,不应该在信息不充分的情况下盲目设计

IC 设计师和封装设计师都面临新的挑战,需要新的方法

封装设计界应该开始采用 ADK 了

扫码关注

扫码关注

![电子设计:FIR最优滤波器设计及AM解调[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/f1/f0bde4c1c6a428268813b906e1bcb4.png)