- 全部

- 默认排序

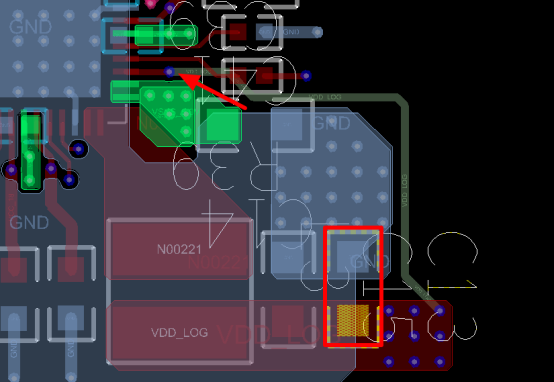

1.电容应根据原理图连接关系,靠近相应管脚放置2.同层连接不需要打孔,多处多余过孔3.部分器件可摆放到底层,减少顶层放置器件,更加美观整齐以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

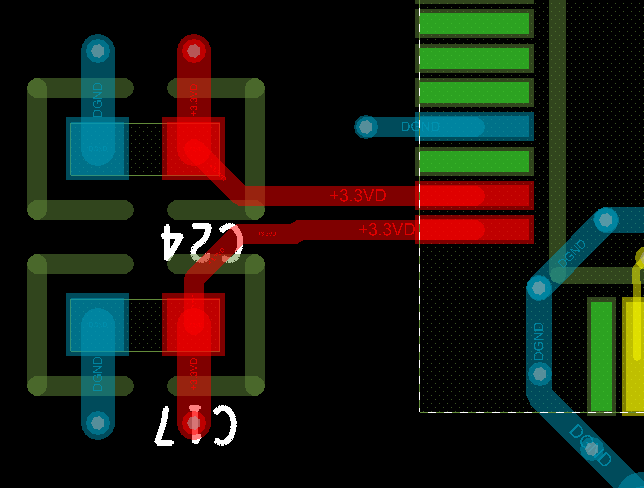

1.布局应按照先大后小原则布局,大器件打孔连接到小器件再连接到芯片管脚2.有一个数据信号等长不到位3.要保持先后线宽一一致,走线出芯片焊盘后尽快加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

在PCB布局布线中,调整拓扑结构,保证信号完整性是一项很重要的任务,因为拓扑结构决定了信号的传输形式和电路的性能,因此对电子工程师来说难度不小,那么在调整拓扑结构时需要注意哪些?1、传输速率与传输介质的选择在高速信号的传输中,需根据所需的传

PCB布线时是电子工程中非常重要的环节,对于保证信号的稳定性和完整性至关重要,若电子工程师遇上100M以上信号的布线需求,该如何设计来保证其稳定性?下面或许能给你些参考。1、选择合适的传输介质对高速信号,选择合适的传输介质是很重要的,常见的

在高速电路系统中,阻抗匹配是很重要的环节,它直接影响着信号的质量和系统的性能,那么如何在PCB上更好实现阻抗匹配?下面一起来看看吧!1、阻抗匹配的定义阻抗匹配是指通过调整电路元件的参数,使输入和输出阻抗相等,从而降低信号反射和失真的现象。在

随着时代高速发展,网络技术始终扮演着至关重要的角色,然而,在网络加载过程中可能会出现各种问题,其中之一是找不到报告NODE,针对这个问题如何解决?1、网络载入时找不到报告NODE的原因①网络配置错误网络配置可能出现错误,导致无法正确找到报告

随着时代高速发展,各种电子设备及系统层出不穷,必然要求更高的通信,因此为了提高通信覆盖率、提高通信质量、降低建网成本和提高安全性,增强国家综合国力,卫星互联网成为了极为关键的产业。近日,据上海市人民政府官网发布更高,上海印发《上海市进一步推

器件尽量整体中心对齐:等长线的gap大于等于3W:地址数据等长误差没什么问题 ,都在误差范围内:其他的基本没什么问题,完成得还可以。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

随着电子技术的飞速发展,高速电路的设计和制造已成为电子工程师的重要任务,在高速电路中,路径回流问题是一个很关键的问题,它对电路的性能和稳定性产生了重要影响,其中芯片互连、铜面切割和过孔跳跃最为复杂常见,本文将从这三方面出发介绍。1、芯片互连

扫码关注

扫码关注