- 全部

- 默认排序

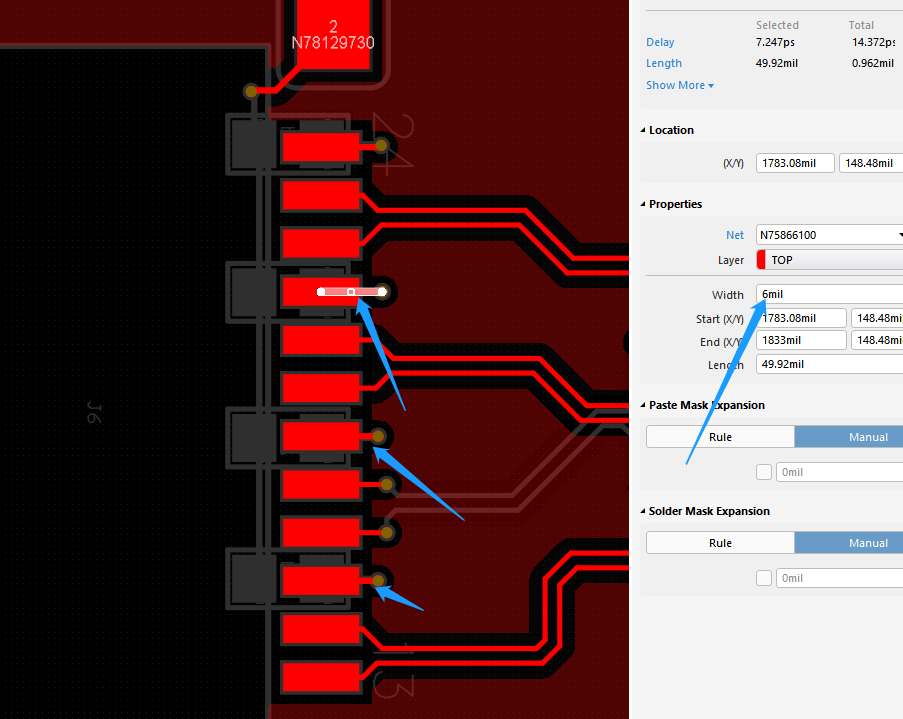

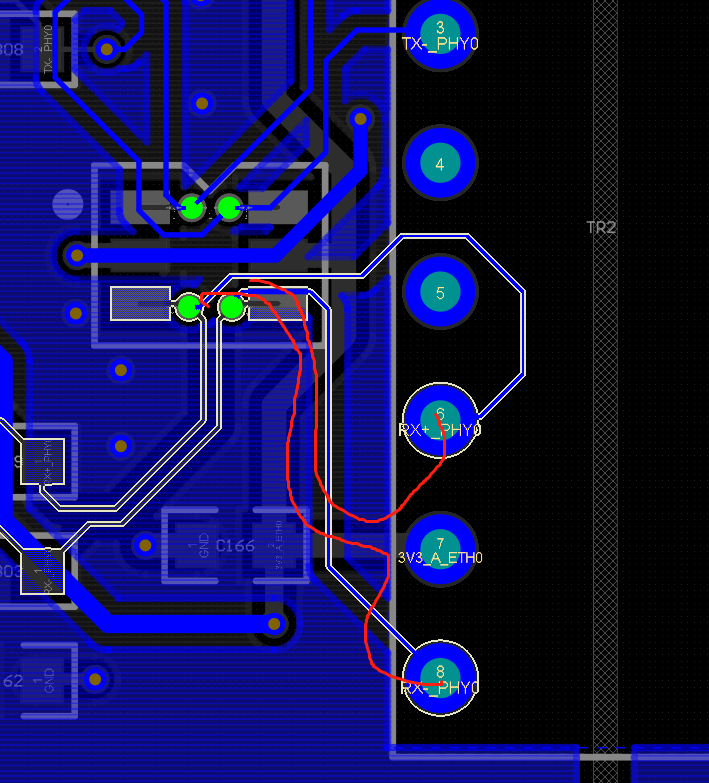

网口除差分信号外,其他信号都需要加粗到20mil2.注意网口的地分割,跨接器件旁要多打地过孔,分割间距2mm后期自己处理一下3.差分出线需要优化一下,器件可以摆放远一点,包地的线要需要均匀打上过孔4.注意差分信号需要按照阻抗线距进行走线晶振

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在PCB布局布线过程中,工程师经常面临着走线宽度变化的问题,由于布线空间的限制,可能会使用更新或更粗的线条来通过某些区域,但这种变化会导致阻抗不匹配,最终信号反射,对整体电路产生负面影响,因此会有哪些问题?一般来说,走线宽度会导致阻抗不匹配

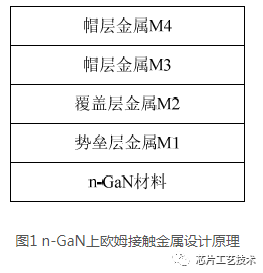

GaN的欧姆接触实验

GaN材料由于其所具有的优良光电性能,而成为固态照明、数字处理、光电器件、功率器件等半导体材料与器件领域的研究热点。金属与半导体接触可以形成肖特基接触,也可以形成非整流的接触,即欧姆接触。欧姆接触不产生明显的附加阻抗,而且不会使半导体内部的平衡载流子浓度发生显著的改变。室温下n-GaN的电子亲和势为

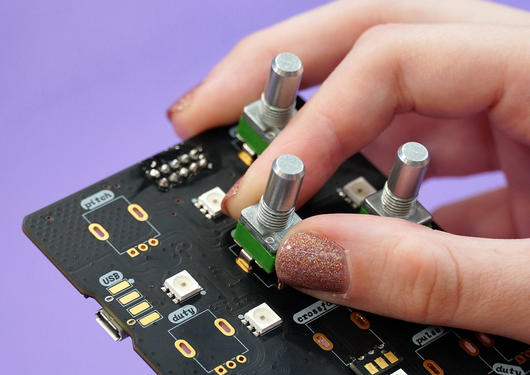

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

软硬结合板,即软硬结合电路板,是一种集成了柔性电路和刚性电路的特殊电路板,其阻抗计算是电路设计及制造的关键环节,对保证信号传输的质量,减少信号损失和提高系统性能至关重要,下面谈谈如何计算软硬结合板的阻抗。1、确定阻抗要求和频率范围在进行软硬

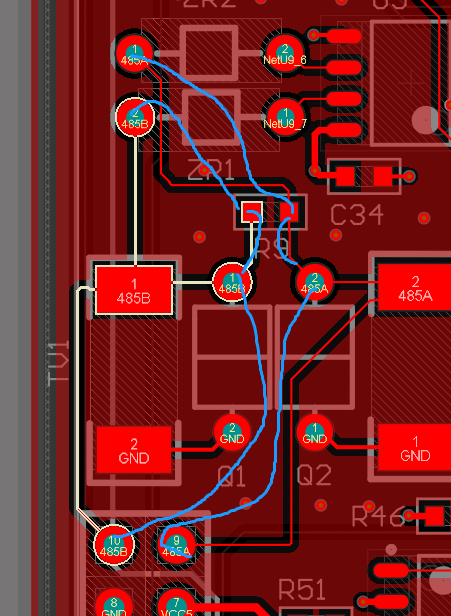

1.485需要走类差分处理或者加粗2.模拟信号需要一字型布局,走线需要加粗,并包地处理3.晶振需要走类差分处理晶振走线都需要优化一下4.差分走线需要按照阻抗线宽线距要求走,后期自己优化一下5.注意地分割,模拟地不要进去数字地里面,分割间距1

在高速数据传输中,PCI Express(PCIe)总线标准以其优越的传输性能,成为了计算机及外部设备之间连接的重要桥梁。而在PCIe系统设计中,阻抗控制直接影响着信号完整性和系统稳定性,必须做好阻抗控制,那么应该选择几欧姆?首先,需要了解

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

扫码关注

扫码关注