在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。

控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰电压,如果不进行控制,信号质量会严重下降。

本节内容就来教大家学习使用si9000软件,以高速USB(480Mbits/s)为例,计算高速差分线布线时的参数。可以按下面的步骤进行:

首先,查询到USB差分线的特征阻抗是90Ω。所以,在设计PCB时,需要按特定的参数布线,使得阻抗匹配到90Ω左右,否则会有信号反射,造成信号质量下降。

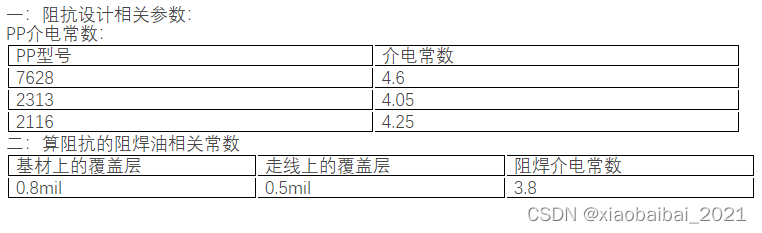

其次,我们需要查询到一些PCB制版厂的板子材料的参数,以xx创板厂为例,查询到工厂的一些PCB参数。

阻抗设计相关参数如下:

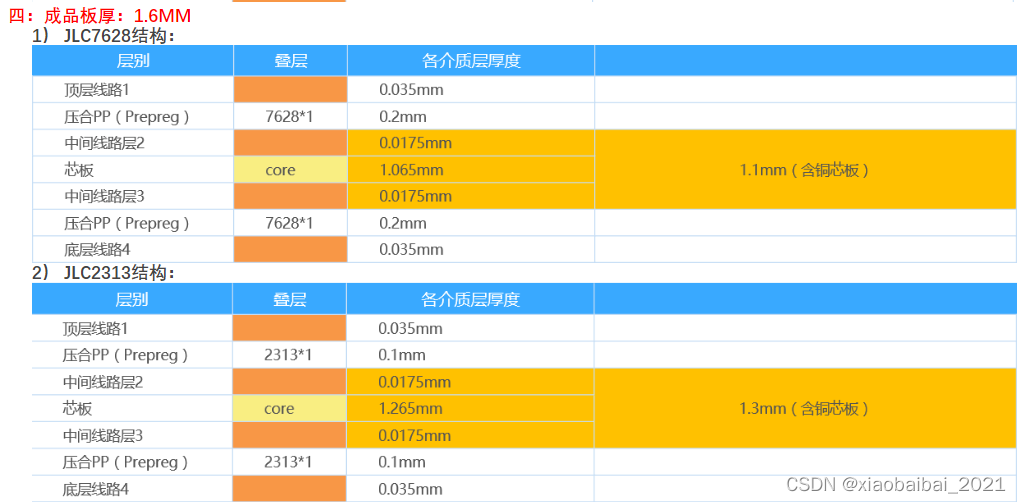

4层板16.mm厚度的PCB层叠参数如下:

从上面两张图中可以看出,如果我们使用四层板,2313叠层结构,那么板材的介电常数为4.05,顶层/底层和相邻的中间层间距是0.1mm(约4mil),顶层铜厚度为0.035mm(约1.4mil),另外还有一些阻焊的参数,有了这些参数,就可以在si9000中计算布线的参数了。

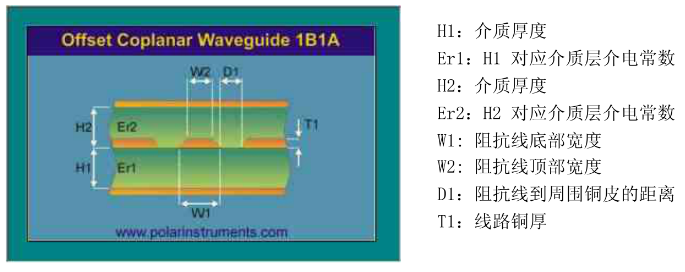

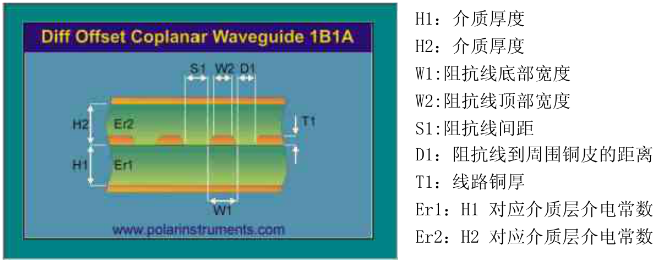

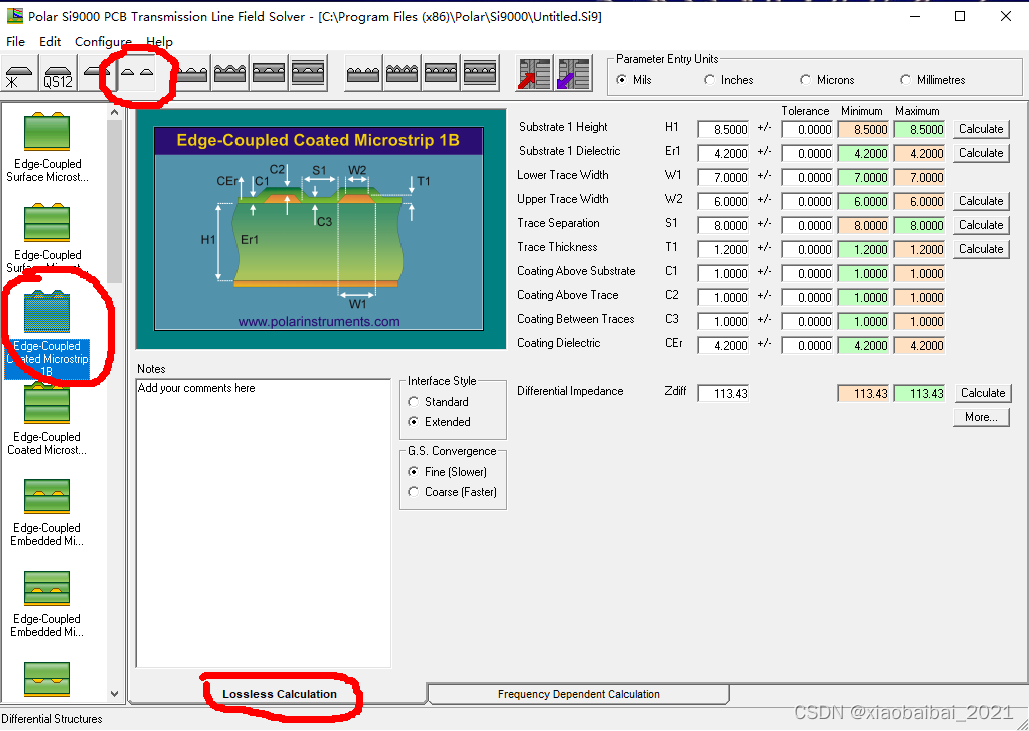

由于我们设计的是USB差分线,当设计高速差分线时,需要把相邻层作为一个完整的参考面。这里我们计划在顶层走线,第二层设计为地层(也可以是电源层),作为参考面。确定之后,打开si9000后,选择差分对,微带线模型,如下:

(如果不是按这样的叠层设计,请在左侧选择相对应的模型)

(如果不是按这样的叠层设计,请在左侧选择相对应的模型)

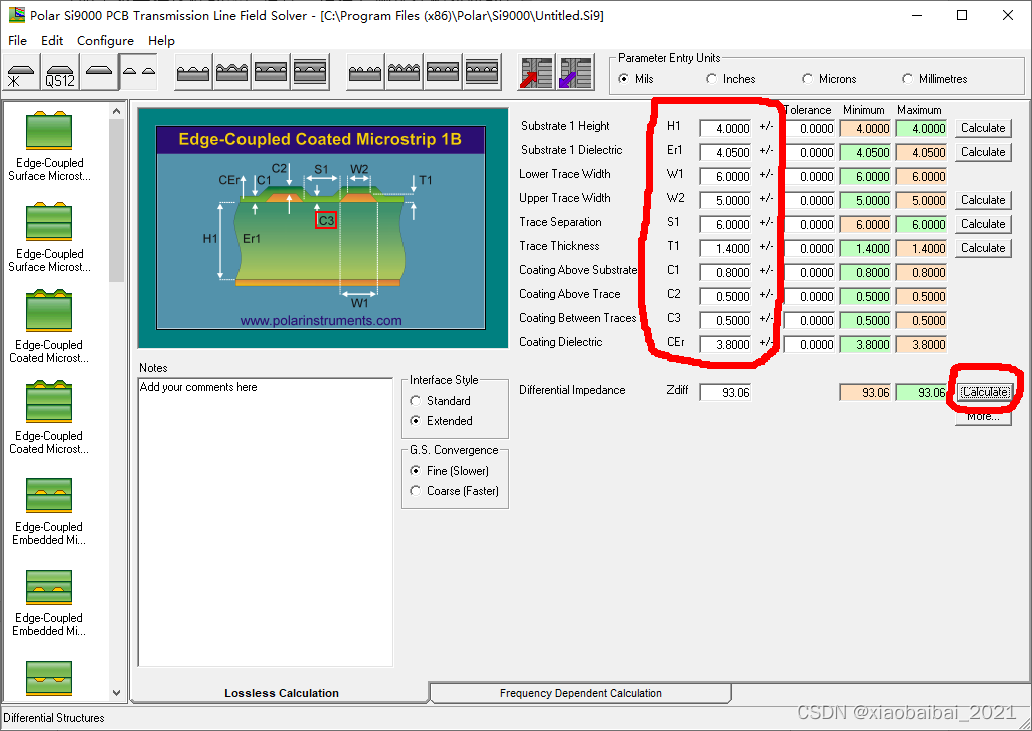

可以看到右上侧有很多参数需要填写,我们一个个来解释一下:

H1:介质厚度,也就是走线层和参考面的距离(板厂提供,为4mil);

Er1:介电常数(板厂提供,为4.05);

W1:差分信号线的底部宽度;

W2:差分信号线的顶部宽度(一般可认为是W1-1mil);

S1:差分线的线间距;

T1:走线的铜厚(板厂提供,1.4mil);

C1:基材阻焊厚度(板厂提供,0.8mil);

C2:铜皮或走线上的阻焊厚度(板厂提供,0.5mil);

C3:基材走线中间的阻焊厚度(一般可认为与C2一样);

CEr:阻焊的介电常数(板厂提供,3.8)。

我们使用si9000的目的,就是要利用已有的板厂提供的参数和目标特性阻抗值,来计算线宽和线间距。

将以上已知参数填入,W1和S1的值可以先填入一个常规的数值(比如W1为6mil、S1为6mil),进行计算:

点击calculate之后,Zdiff就是计算得到的特征阻抗,可以看到现在的参数计算出为93.06Ω,实际上与标准的90Ω相差不大了。一般在±10%的范围内,用这个参数设计USB的差分线一般来说也是可行的。

如果计算与目标阻抗值相差较大,可以调整W1、S1的值,使得计算出的阻抗值与要求值一致。如下图,再调整一点S1的值,改为5mil,就可以很接近90Ω了:

这样,我们就得到了一组W1和S1的值,即我们用线宽6mil、正负线间距5mil的规则来设计USB差分线,阻抗是匹配的。

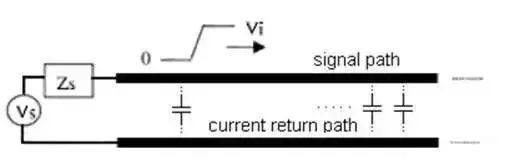

a) 在布高速差分线时,要求相邻层为完整的参考平面,最好的是地平面(也可以是电源平面),但是一定要保证走线下方连续,只有这样阻抗才是匹配的;

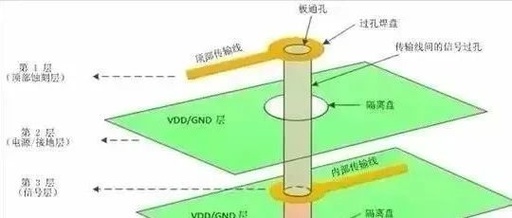

b) 差分线上一般不要有过孔,过孔会有寄生电容、电感,也会导致阻抗不连续。而且过孔换层时,会导致参考面变化,如顶层走线的参考面在第二层,而穿到底层后参考面变成了倒数第二层;会使得信号的回流路径受阻;如果实在避免不了过孔,需要紧邻过孔放置连接地/电源过孔,这样信号回流时可以通过过孔,从第二层的参考面直接流到倒数第二层的参考面,保证了回流路径顺畅;

c) 如果差分线上有串电阻、电容,在这些器件处,由于焊盘一般比线宽,会使得阻抗变小,所以一般在这些器件下方,要把参考面挖空;

d) 差分对正负之间的等长比等间距更重要一些,如果等间距布线和等长布线无法同时满足时,优先满足等长的要求。

扫码关注

扫码关注