在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。

如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的SerDes器件,例如飞兆半导体的μSerDes系列。

1、SerDes器件选择

μSerDes器件基于恒流型I/O设计,允许差分阻抗在70Ω至120Ω范围内变动。这种宽泛的匹配范围提供了更大的设计灵活性,有助于应对实际布线中可能出现的各种挑战。

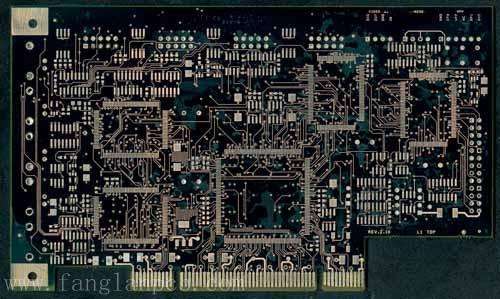

2、差分阻抗计算与优化

在设计串行传输线时,使用差分阻抗计算器进行精确模拟至关重要。这些专业工具综合考虑了邻近接地和磁场效应,能够提供最精确的阻抗预测。若无专业设备,也可采用业界公认的公式进行计算,但需注意其使用范围和局限性。

3、实际测量及问题识别

完成PCB或FPCB布线后,应使用时域反射计(TDR)进行实际测量。TDR通过发送差分信号并测量由阻抗失配引起的反射,从而有效识别和解决潜在的差分阻抗问题。这些问题通常源于接地屏蔽的不当设计,特别是在连接器处和柔性线缆的可动部分。

4、接地屏蔽优化策略

针对差分阻抗问题,一种常见的解决方法是优化接地屏蔽布局。具体措施包括减少屏蔽、增加串行线与接地之间的间距或使用网格状接地屏蔽而非实心覆铜。这些措施旨在提高差分阻抗,同时保持适当的屏蔽效果。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注