- 全部

- 默认排序

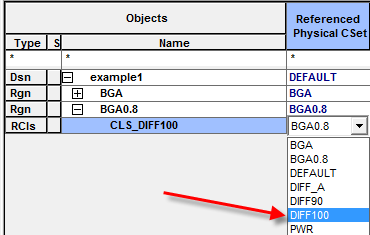

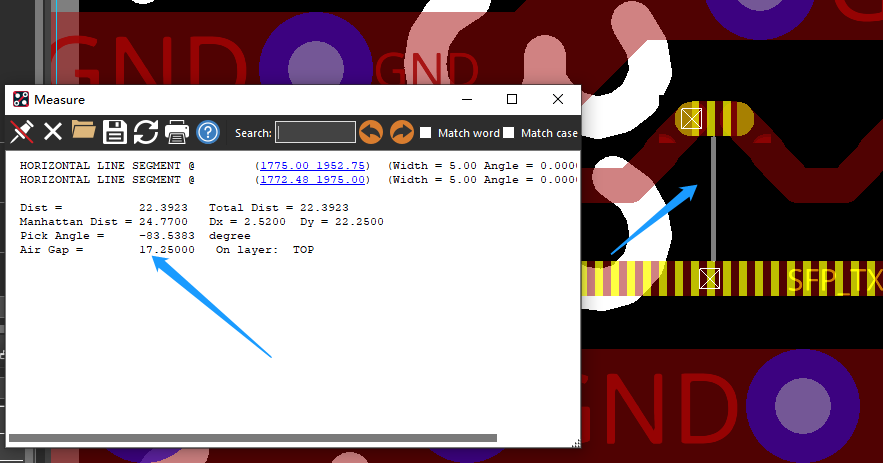

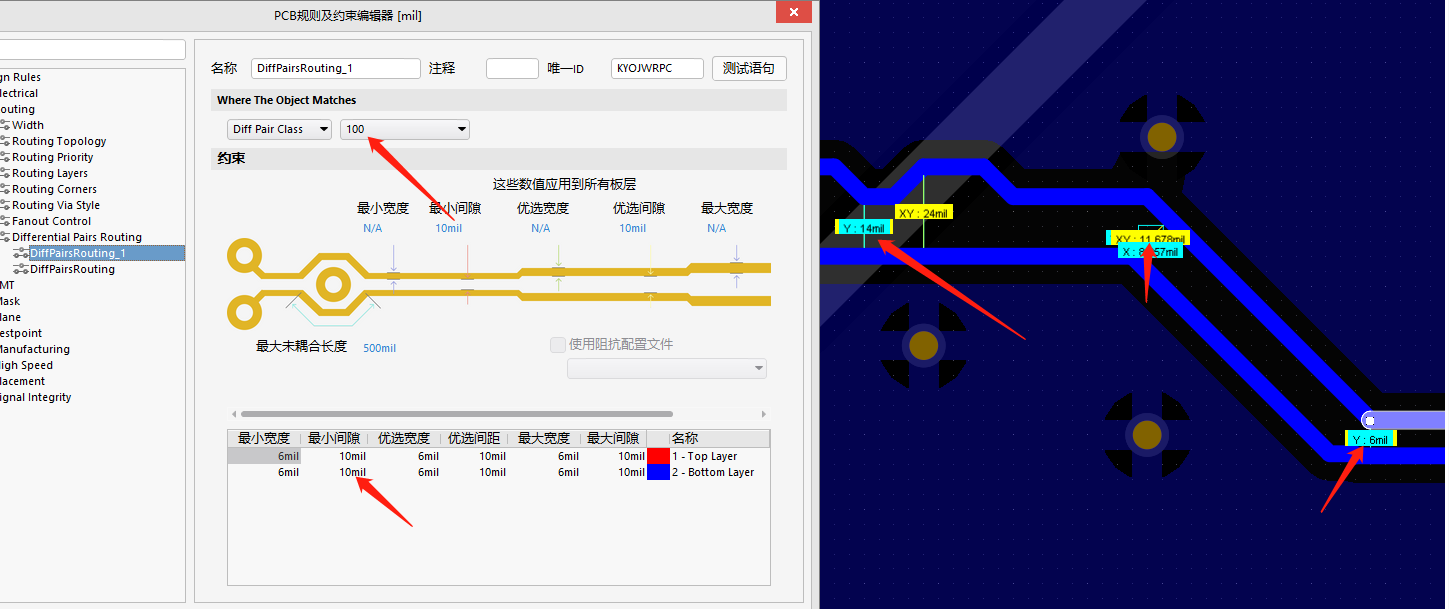

答:在进行PCB设计布线时,优先是根据阻抗线宽进行走线设计,但是在BGA区域为了方便出线,一般会添加区域走线规则,当然能够满足阻抗线宽的情况下,尽量使用阻抗线宽。这里,我们讲解一下,如何设置可以让差分阻抗线宽的优先级高于区域规则线宽,操作如下所示:

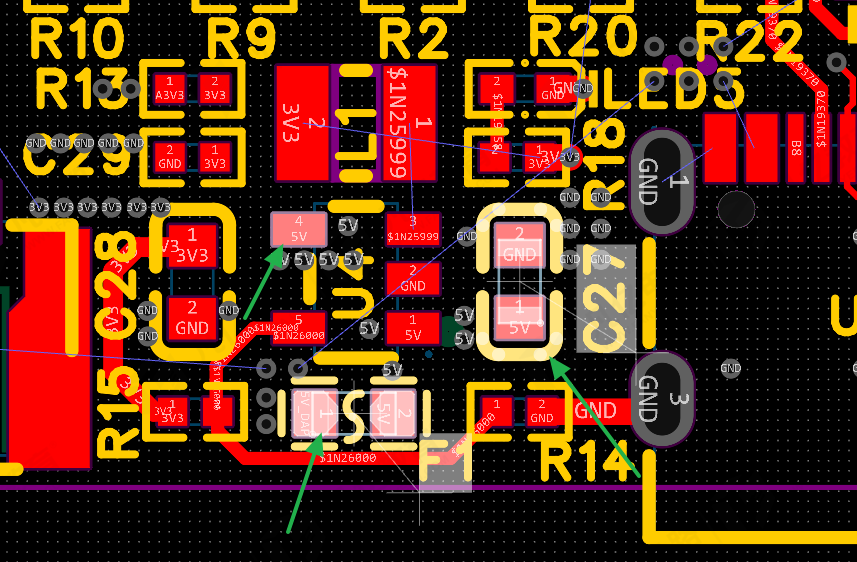

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

晶振布局、布线错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要建立差分对走差分阻抗控制90欧姆做对内等长,换层需要靠近过孔打回流地过孔,D7、D8应该尽量靠近typec管脚放置。TF卡所有信号

随着现代高速数字电路急速发展,差分信号传输已成为当代电子工程师必须掌握的重点技术之一,它可以有效抵消信号传输过程中的共模噪声,在差分信号传输中,如何正确匹配差分阻抗是至关重要的,所以本文将讨论如何在PCB布线阶段中正确匹配差分阻抗?在PCB

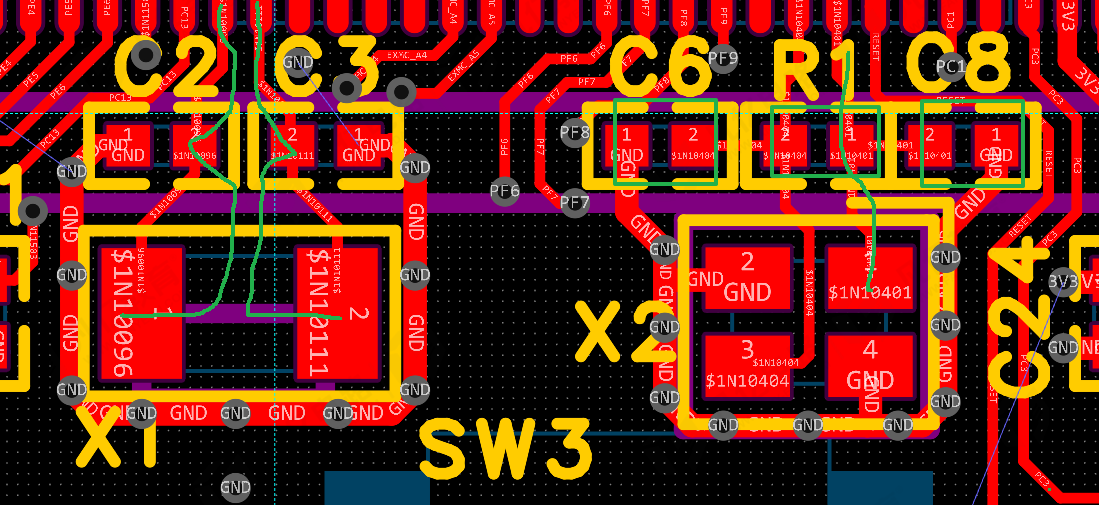

差分对内等长凸起高度不能超过线距的两倍差分走线不满足差分阻抗间距要求3.光口模块座子下面需要所有层挖空处理4.后期自己在电源层铺铜尽量连接差分出线方式需要再优化一下跨接地旁边可以尽量多打地过孔以上评审报告来源于凡亿教育90天高速PCB特训班

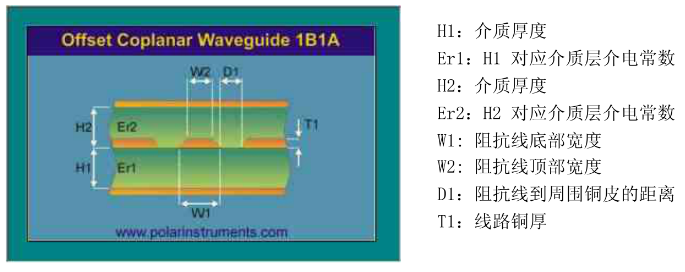

由于文章篇幅限制,将此文分为上中下,欲看上下篇可点击右侧链接《不能错过!阻抗计算模型超全必看!(上)》。7、内层单端阻抗共面计算模型适用范围:内层单端共面阻抗计算。8、内层差分阻抗共面计算模型适用范围:内层差分共面阻抗计算。9、嵌入式单端阻

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

扫码关注

扫码关注