在PCB布局布线过程中,工程师经常面临着走线宽度变化的问题,由于布线空间的限制,可能会使用更新或更粗的线条来通过某些区域,但这种变化会导致阻抗不匹配,最终信号反射,对整体电路产生负面影响,因此会有哪些问题?

一般来说,走线宽度会导致阻抗不匹配,这是因为走线的特性阻抗是与其宽度成反比。

当走线宽度减小时,特性阻抗增大;

当走线宽度增大时,特性阻抗减小。

这种阻抗不匹配会在走线宽度变化时产生反射,反射信号与原信号叠加,最终导致信号失真、噪声叠加及整体电路性能下降。

而反射的严重程度主要受到三种因素影响,分别是阻抗变化的大小、信号上升时间及窄线条上信号的时延。

首先,阻抗变化的大小决定了反射程度,当阻抗变化率超过一定阈值(如10%)时,反射信号可能对整体电路性能产生显著影响。

其次,信号上升时间越短,反射信号对整体信号的影响越大。

最后,窄线条上信号的时延也可能导致反射信号的叠加及增强。

为了减小走线宽度变化引起的反射问题,工程师可采取以下方法来解决:

1、阻抗匹配

通过调整走线宽度或添加匹配电阻等方式,使走线在不同区域的阻抗保持一致,从而减小反射;

2、优化布线设计

尽量避免在布线空间有限的区域使用过细的线条,以减少阻抗变化的可能性;

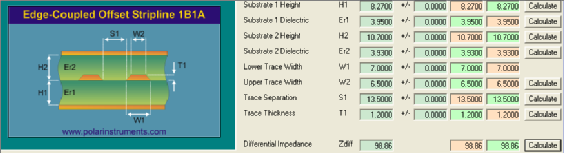

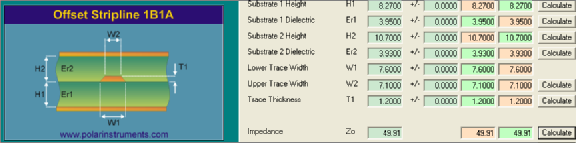

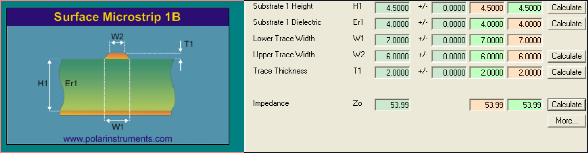

3、选择合适的板材及介质厚度

根据实际需求选择合适的板材和介质厚度,以优化走线的特性阻抗;

4、端接处理

在走线宽度变化处进行端接处理,如添加终端电阻或电容等,以减小反射信号的幅度。

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注