在高速数据传输中,PCI Express(PCIe)总线标准以其优越的传输性能,成为了计算机及外部设备之间连接的重要桥梁。而在PCIe系统设计中,阻抗控制直接影响着信号完整性和系统稳定性,必须做好阻抗控制,那么应该选择几欧姆?

首先,需要了解的是:PCIe的阻抗选择并非随意,而是需要根据具体的PCIe版本和系统需求来确定。一般来说,PCIe 3.0及以下的版本,推荐使用的共模阻抗为100欧姆。

而随着技术的不断进步,PCIe 3.0及更高版本则采用了更为严格的85欧姆标准。这种阻抗标准的调整,是为了适应更高速率的数据传输需求,确保信号的稳定性和完整性。

那么,问题来了,为什么PCIe的阻抗有这样的选择?

①信号完整性

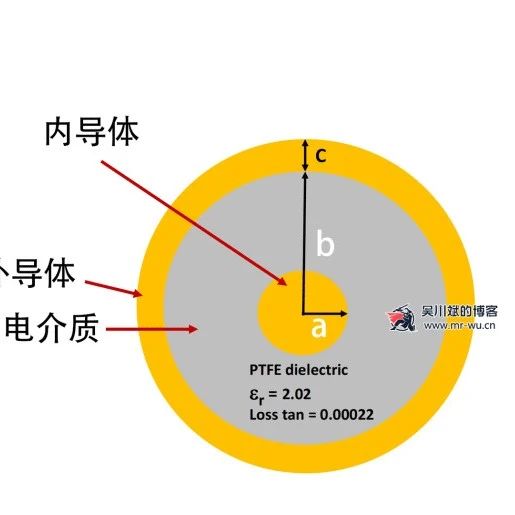

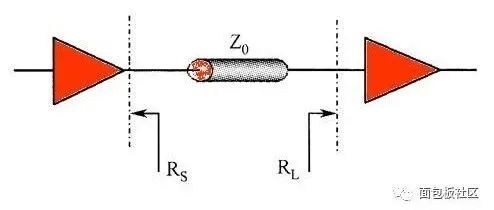

PCIe系统采用差分信号作为主要的传输方式,而共模阻抗的控制对于减小电磁干扰(EMI)和保持信号完整性至关重要。通过选择适当的阻抗值,可以确保信号在传输过程中的衰减和失真达到最小,从而提高信号的质量。

②系统稳定性

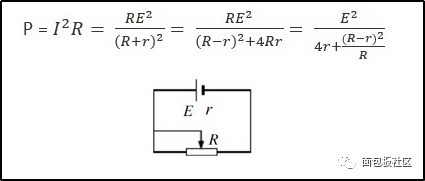

阻抗的不匹配会导致反射和噪声的产生,从而影响系统的稳定性。选择符合PCIe标准的阻抗值,可以最大限度地减少这种不匹配带来的负面影响,确保系统的稳定运行。

③兼容性

PCIe作为一种通用的总线标准,需要考虑到与各种设备和系统的兼容性。通过规定统一的阻抗标准,可以确保不同设备之间的互联互通,提高系统的整体性能。

总的来说,在具体应用中应根据PCIe版本和系统需求来确定阻抗值。

一般是PCIe 3.0及以下版本推荐使用100Ω阻抗;而PCIe 3.0及以上版本选择85Ω标准。

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注