- 全部

- 默认排序

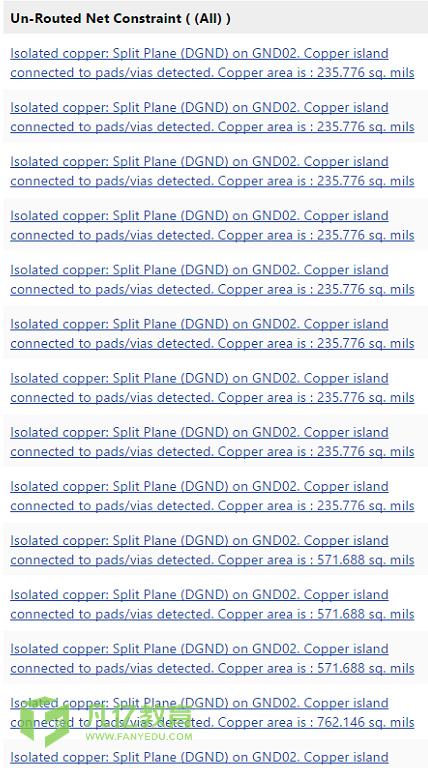

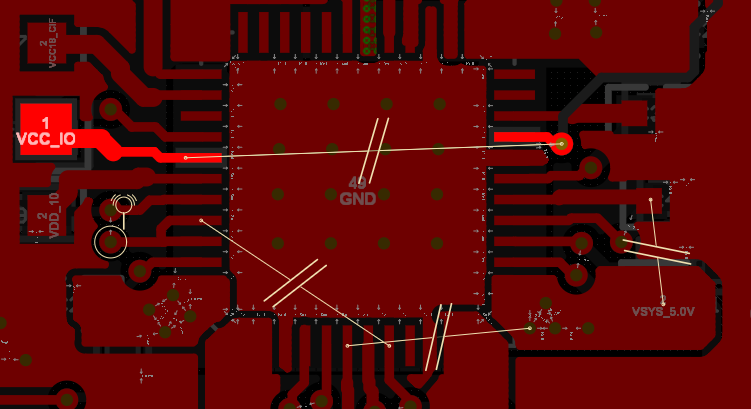

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

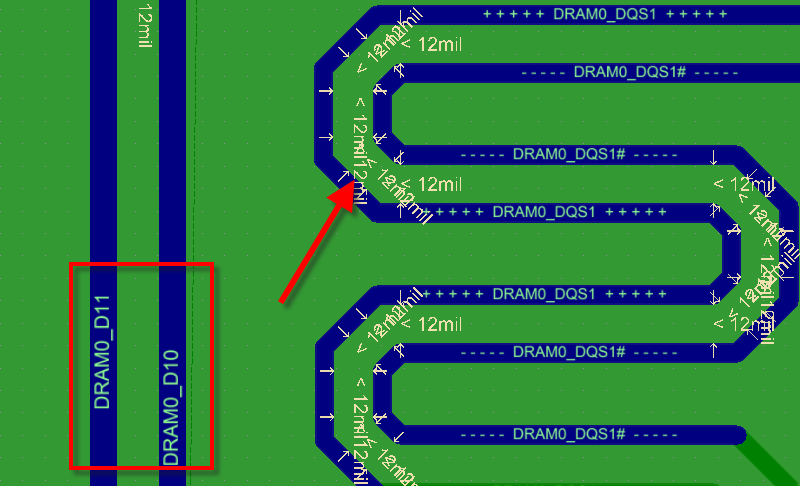

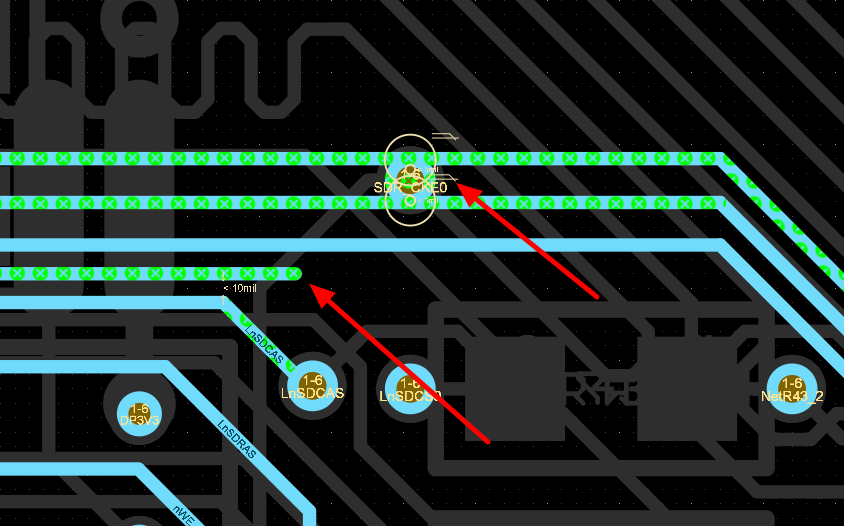

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

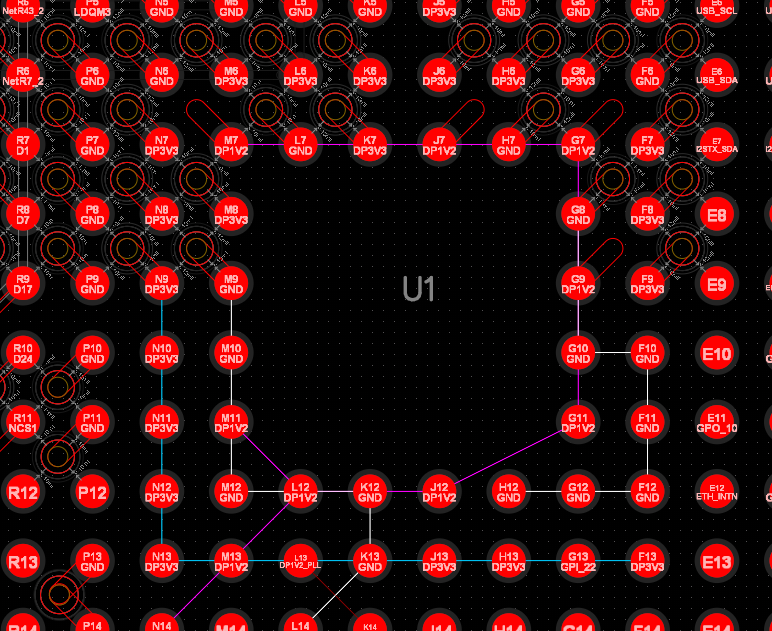

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

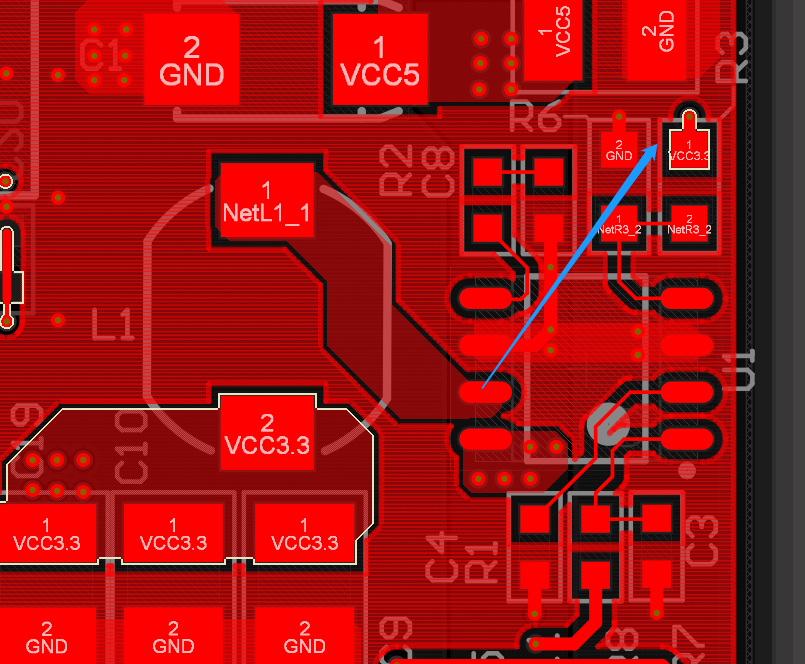

还存在多处开路报错:看下此处是什么元素跟元素的间距报错:检查了对应自己修改。电感底部不要放置器件 ,净空,自己重新布局下:并且电感内部挖空处理:看下此处VCCIO线宽是否满足其载流大小:处理下多余线头删除,连接到过孔中心:走线不要出现直角:

存在短、天线、间距报错布线要求3w间距规则等长绕线太乱,锯齿状等长尽量咬合地址线等长不达到要求误差范围时钟线等长错误电源布线注意加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

反馈信号需要走线连接,并加粗处理2.模拟信号需要包地,走线加粗到12mil3.跨接器件旁边要多打过孔,间距最少2mm,有器件的地方可以不满足4.网口需要添加差分对按照差分间距走线,对内等长误差5mil5.存在间距报错,太近,后期容易造成短路

扫码关注

扫码关注