- 全部

- 默认排序

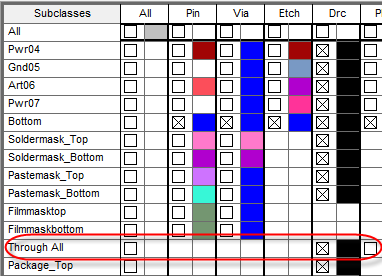

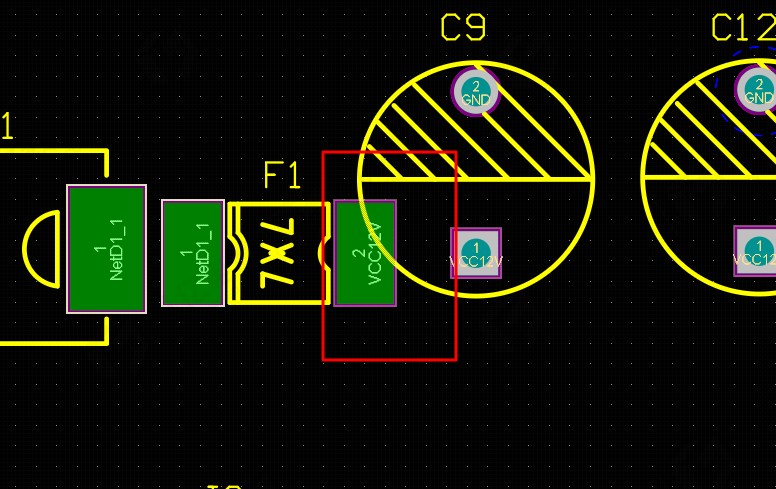

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

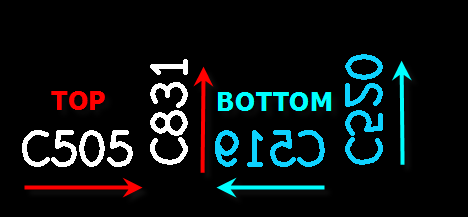

答:一般情况下,我们推荐位号字符在与阻焊不干涉的情况下,推荐位号字符与SMD焊盘、插装焊接孔、测试点、Mark点至少保证6mil的间距,位号字符之间部分重合是可以的,任何位号字符由于重叠导致的无法辨认必须进行调整。

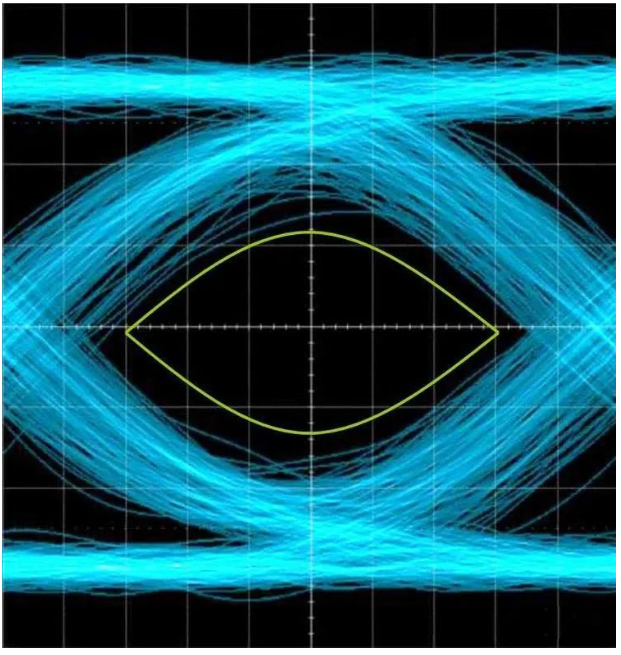

PCB上的眼图是什么?

眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。本文将带领大家了解PCB上的眼图是什么,眼图是怎样形成的,眼图中包含有哪些信息,如何根据眼图情况分辨信号质量。想看 懂示波器眼图需要掌握以下4点:什么是眼图?

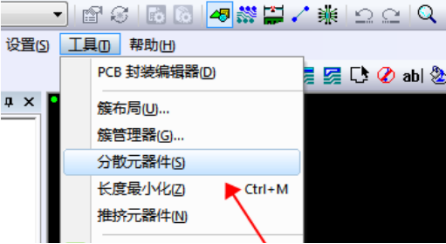

PADS分散元器件

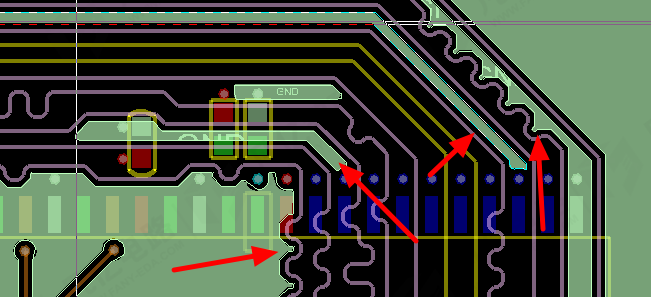

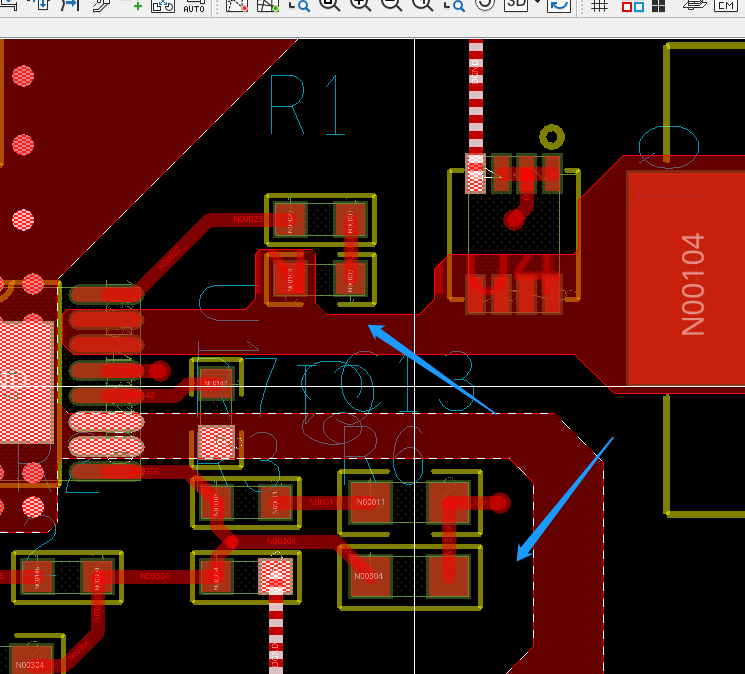

布局时,有部分器件堆叠在一起,器件重叠导致选择不精准,而且一个一个抓开效率比较低,为了方便,可以使用分散元器件命令快速处理。1)若需要将整板的器件(除胶黏)进行打散,执行菜单栏“工具-分散元器件”。如图5-103、5-104所示。图5-10

薄膜电容器是以金属箔当电极,将其和聚乙酯,聚丙烯,聚苯乙烯或聚碳酸酯等塑料薄膜,从两端重叠后,卷绕成圆筒状的构造之电容器。本文收集整理了一些资料,期望能对各位读者有比较大的参阅价值。薄膜电容有多种分类方法,可以按电解质分类,按薄膜(介质)和

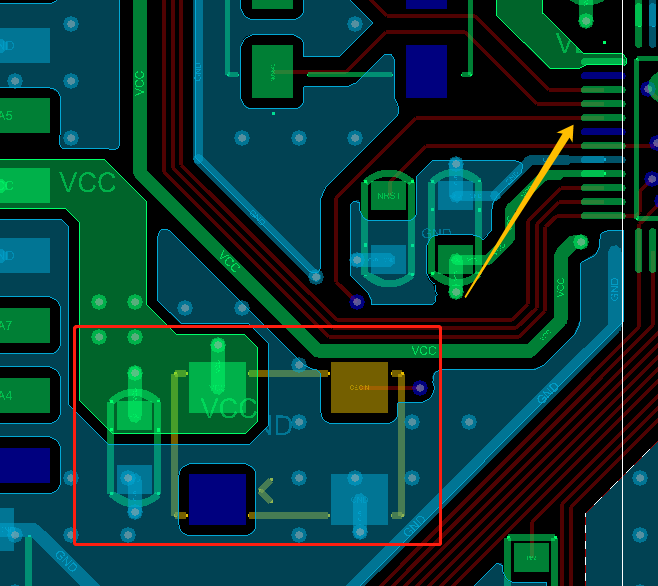

器件摆放干涉,如生产会造成两个器件重叠无法焊接。部分器件摆放过于紧凑,间距大小不一不同方;建议器件对齐等间距摆放,尽量相邻器件同方向放置。J8连接器应该放到电路的输出末端,电源应该铺铜加大载流电源应该从电阻流到芯片在到连接器。焊盘应该出宽方

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

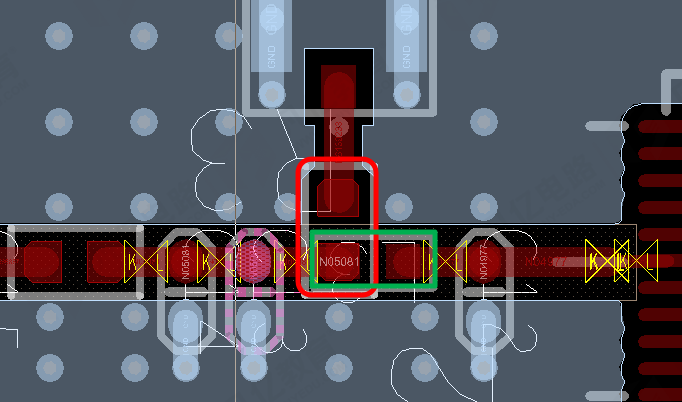

1.器件重叠,焊盘重叠会导致器件无法焊接。2.底层没有铺铜处理3.过孔应打到走线最后一段,完全包围走线。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.t

晶振靠近管脚放置,尽量少打孔换层,包地处理2.差分包地地线上需要多打地过孔3.器件摆放尽量对齐处理4.注意过孔不要上焊盘后期自己检查一下过孔上焊盘和过孔重叠5.信号包地应该用地网络,不要用电源6.SD卡组内误差不能超过400mil7.注意走

配置电阻电容注意布局可以向下向上放置,中间腾出空间优先放置主干道上的器件:主干道上的器件布局优先级最高。建议吧静态铜皮转换为动态铜皮,设计基本放置动态铜皮:反馈信号走个8-12mil即可:注意器件丝印最好调整下,不要重叠了:注意同焊盘网络连

扫码关注

扫码关注