- 全部

- 默认排序

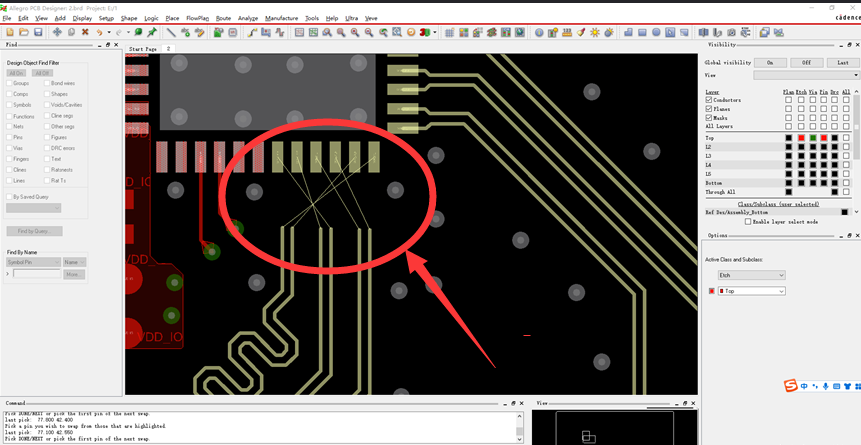

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些mipi或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

Cadence allegro学习笔记第一节 启动与板框的制作1、启动操作启动PCB Editor图标,弹出对话框后选择Allegro PCB Designer后择OK进入界面。 选择File文件菜单选择New新建弹出下面对话框。设置

为了更好就业,寻高薪工作现在的工程师早已卷成麻花面试被问会不会以下技能:AD/Allegro/Pads、单片机、硬件等没办法,只能多学本领提升价值然而外面付费课程动辄上千免费课程质量不行费时费力这种时候,就让凡亿教育来帮忙《Cadence

许多电子工程师会选择Cadence Allegro来设计PCB,在使用时会遇到许多操作,其中之一是在Cadence环境中创建封装库,确保数据的高效与准确,那么在操作Cadence时需要注意什么?1、精确测量与缩放Pad尺寸根据Pin脚的精确

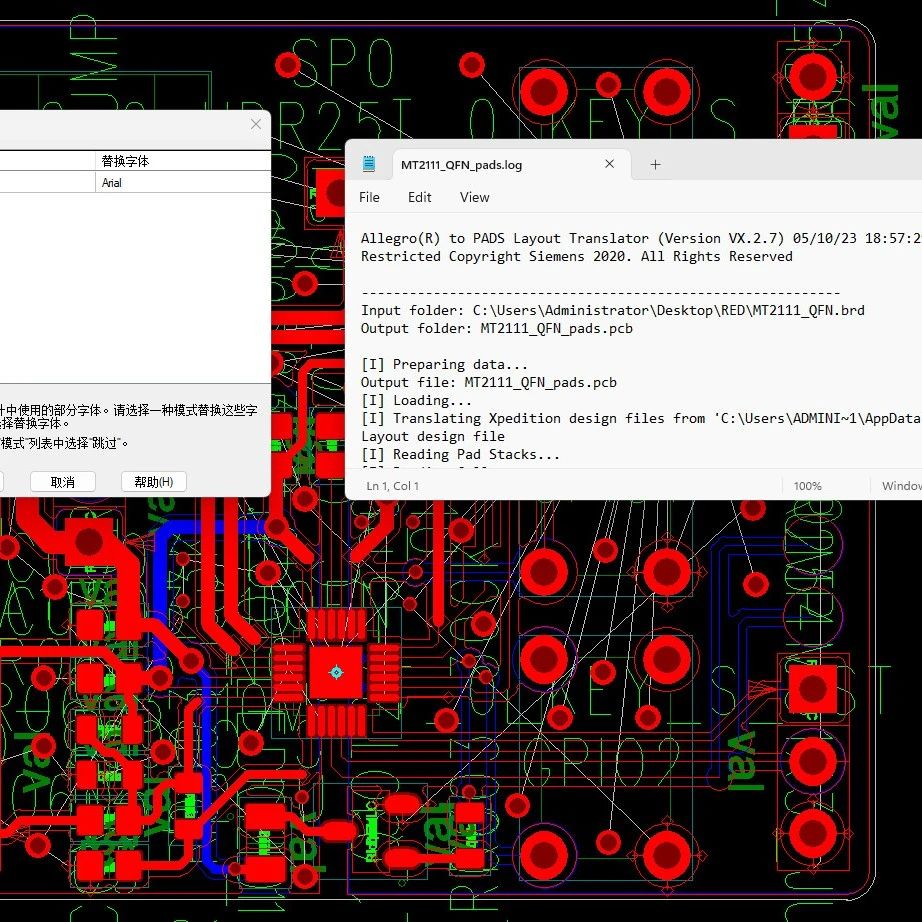

添加用户变量 变量名:AEX_BIN_ROOT 值:PADS软件中translators软件的bin目录路径 如下图所示: AEX_BIN_ROOT= C:\MentorGraphics\PADSVX.2.7\SDD_HOME ranslators\win32\bin 添加 用户变量

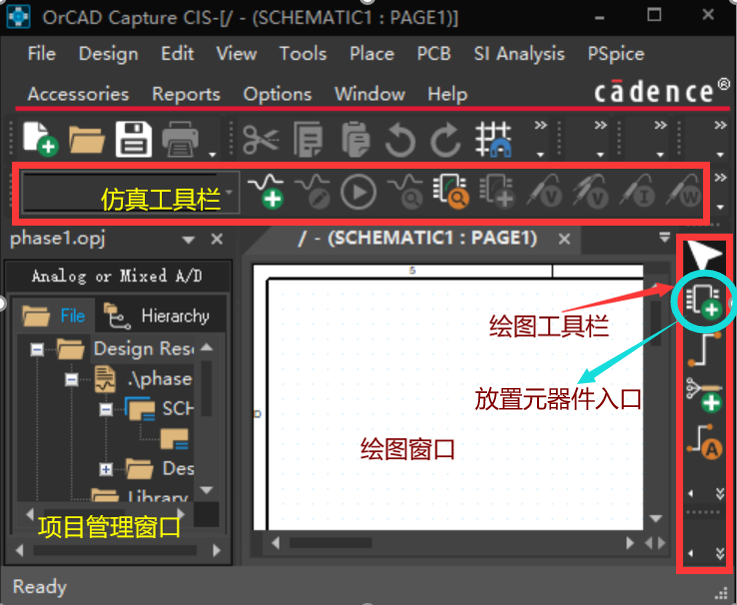

今天有小伙伴向老wu咨询了个Capture 16.6的启动异常问题,如下图所示这个问题老wu之前也有遇到过,只是当时没有找到造成该异常的真正原因,所以直接使用了重装操作系统大法解决了。今天再次面对这个启动异常的问题,老wu建议其尝试了清空Spb_data目录,卸载VC 2005运行库之后重装Cad

这周让我们从繁杂的模电学习中逃离出来,看看占据中国EDA30%市场份额的巨头公司Cadence带来的原理图仿真工具PSpice的应用。开设新版块的原因 小电最近在给Cadence公司的官方公众号写PCB产品线中原理图仿真部分的教程,感觉不管是针对刚刚开始接触模拟电路的同学,还是已经工作的小

Cadence于今年2月收购了cccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccc Software公司,该公司的所有工程师和创始人最初都来自贝尔实验室,在没有市场营销的情况下,Integrand产品仅靠口碑就获得了业界的巨

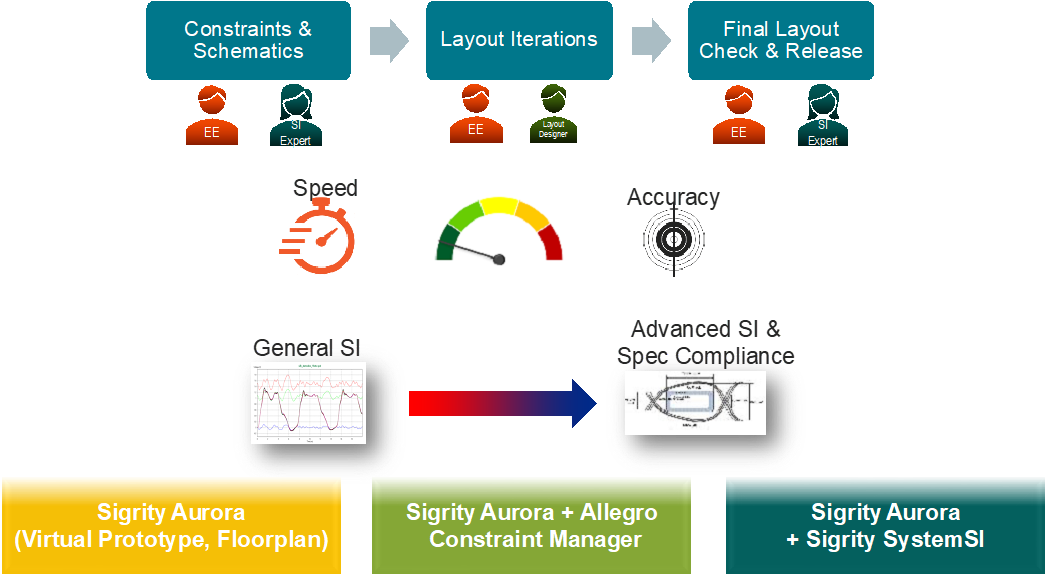

本文作者为 Cadence Design Systems 产品管理组总监 Brad Griffin,文章首发于 iconnect007.com。预计阅读时长:18分钟本文将重点介绍如何在无需久等 SI 和 PI 专家反馈的情况下,助力 PCB 设计团队在预算范围内按时交付合格的产品。对于当今设计高速

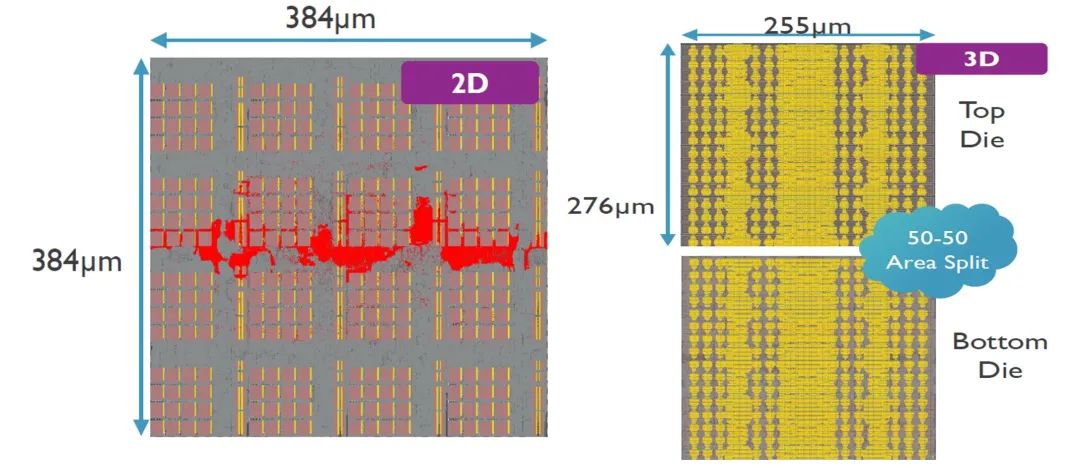

Cadence员工Mohamed Naeim 博士曾在CadenceLIVE 欧洲用户大会上做过一场题为《2D/3D 热分析和三裸片堆叠设计实现》的演讲,本文将详细讲述该演讲内容。实验:两个裸片是否优于一个裸片?由于线长缩短,3D-IC 会减少功耗,带来性能提升。在此,3D-IC 指的是将一个裸片(

扫码关注

扫码关注